## **Scalability of Microkernel-Based Systems**

Zur Erlangung des akademischen Grades eines

#### DOKTORS DER INGENIERWISSENSCHAFTEN

von der Fakultät für Informatik der Universität Fridericiana zu Karlsruhe (TH) genehmigte

#### **DISSERTATION**

von

#### **Volkmar Uhlig**

aus Dresden

Tag der mündlichen Prüfung: 30.05.2005

Hauptreferent: Prof. Dr. rer. nat. Gerhard Goos

Universität Fridericiana zu Karlsruhe (TH)

Korreferent: Prof. Dr. sc. tech. (ETH) Gernot Heiser

University of New South Wales, Sydney, Australia

Karlsruhe: 15.06.2005

#### **Abstract**

Microkernel-based systems divide the operating system functionality into individual and isolated components. The system components are subject to application-class protection and isolation. This structuring method has a number of benefits, such as fault isolation between system components, safe extensibility, co-existence of different policies, and isolation between mutually distrusting components. However, such strict isolation limits the information flow between subsystems including information that is essential for performance and scalability in multiprocessor systems.

Semantically richer kernel abstractions scale at the cost of generality and minimality—two desired properties of a microkernel. I propose an architecture that allows for *dynamic adjustment* of scalability-relevant parameters in a general, flexible, and safe manner. I introduce isolation boundaries for microkernel resources and the system processors. The boundaries are controlled at user-level. Operating system components and applications can transform their semantic information into three basic parameters relevant for scalability: the involved processors (depending on their relation and interconnect), degree of concurrency, and groups of resources.

I developed a set of mechanisms that allow a kernel to:

- 1. efficiently track processors on a per-resource basis with support for very large number of processors,

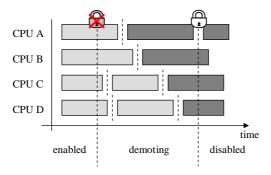

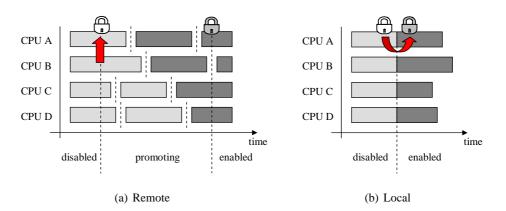

- 2. dynamically and safely adjust lock primitives at runtime, including full deactivation of kernel locks in the case of no concurrency,

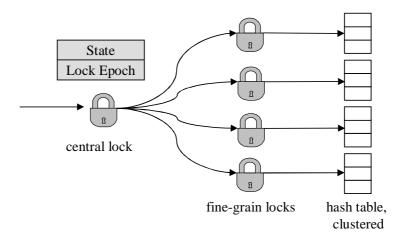

- 3. dynamically and safely adjust locking granularity at runtime,

- 4. provide a scalable translation-look-aside buffer (TLB) coherency algorithm that uses versions to minimize interprocessor interference for concurrent memory resource re-allocations, and

- efficiently track and communicate resource usage in a component-based operating system.

Based on my architecture, it is possible to efficiently co-host multiple isolated, independent, and loosely coupled systems on larger multiprocessor systems, and also to fine-tune individual subsystems of a system that have different and potentially conflicting scalability and performance requirements.

I describe the application of my techniques to a real system: L4Ka::Pistachio, the latest variant of an L4 microkernel. L4Ka::Pistachio is used in a variety of research and industry projects. Introducing a new dimension to a system — parallelism of multiprocessors — naturally introduces new complexity and overheads. I evaluate my solutions by comparing with the most challenging competitor: the uniprocessor variant of the very same and highly optimized microkernel.

### Zusammenfassung

Mikrokernbasierte Systeme teilen die Betriebssystemfunktionalität in unabhängige und isolierte Komponenten auf. Die Systemkomponenten unterliegen dabei denselben Isolations- und Schutzbedingungen wie normale Nutzeranwendungen. Solch eine Systemstruktur hat eine Vielzahl von Vorteilen, wie zum Beispiel Fehlerisolation zwischen Systemkomponenten, sichere Erweiterbarkeit, die Koexistenz mehrerer unterschiedlicher Systemrichtlinien und die strikte Isolation zwischen Komponenten, die sich gegenseitig mißtrauen. Gleichzeitig erzeugt strikte Isolation auch Barrieren für den Informationsfluß zwischen den individuellen Subsystemen; diese Informationen sind essentiell für die Performanz und die Skalierbarkeit in Multiprozessorsystemen.

Kernabstraktionen mit semantisch höherem Gehalt skalieren auf Kosten der Allgemeinheit und der Minimalität, zwei erwünschte Eigenschaften von Mikrokernen. In dieser Arbeit wird eine Architektur vorgestellt, die es erlaubt, die für die Skalierbarkeit relevanten Parameter generisch, flexibel, und sicher dynamisch anzupassen. Es werden Isolationsschranken für die Mikrokernresourcen und Systemprozessoren eingeführt, welche unter der Kontrolle von Nutzerapplikationen stehen. Die Betriebssystemkomponenten und Anwendungen können das ihnen zur Verfügung stehende semantische Wissen in die folgenden drei skalierbarkeitsrelevanten Basisparameter umwandeln: die involvierten Prozessoren (abhängig von den Prozessorbeziehungen und dem Speichersubsystem), den Grad der Parallelität und Ressourcengruppierungen.

Es wurden die folgenden Methoden und Mechanismen entwickelt:

- 1. eine effiziente Methode zur Speicherung und Auswertung der zu einer Ressource zugehörigen und relevanten Prozessoren,

- ein dynamisches und sicheres Synchronisationsprimitiv, welches zur Laufzeit angepaßt werden kann (dies beinhaltet die vollständige Deaktivierung von Kernsperren für den Fall, daß keine Parallelität vorhanden ist),

- 3. die dynamische und sichere Anpassung der Granularität von Sperren zur Laufzeit,

- 4. ein skalierbarer *translation-look-aside buffer* (TLB) Kohärenzalgorithmus, der zur Vermeidung von wechselseitigen Beeinflussungen von Prozessoren ein Versionsschema nutzt, sowie

- 5. ein Mechanismus zur effizienten Ermittlung und Weiterleitung von Ressourcennutzungsinformationen in einem komponentenbasierten Betriebssystem.

Basierend auf dieser Architektur ist es möglich, mehrere unabhängige, isolierte, und lose verbundene Systeme gleichzeitig auf einem Mehrprozessorsystem zu betreiben. Desweiteren ermöglicht die Architektur, einzelne Subsysteme

individuell feinabzustimmen. Dies ist selbst dann möglich, wenn Subsysteme unterschiedliche oder sogar widersprüchliche Skalierbarkeits- und Performanceanforderungen haben.

Die Techniken werden an einem real existenten System exemplarisch evaluiert: dem L4Ka::Pistachio Mikrokern, der die neueste L4-Version darstellt. L4Ka::Pistachio wird aktiv in einer Reihe von Forschungs- und Industrieprojekten eingesetzt. Die Einführung der neuen Dimension *Parallelität von Prozessoren* erhöht sowohl die Komplexität als auch die Kosten. Die Effizienz der vorgestellten Lösungen werden daher an dem größten Konkurrenten gemessen: der Uniprozessorvariante desselben hochoptimierten Mikrokerns.

### Acknowledgements

First, I would like to thank my supervisor, Prof. Gerhard Goos. After the loss of Jochen Liedtke, he not only ensured the survival of our group but rather its blossoming. It took me a while to realize the wisdom behind many of his demanding requests and I am extremely thankful for his patience and guidance over the last few years. I am particularly thankful for many of his advices in areas that were not related to this work or even computer science.

Jochen Liedtke, who passed away in 2001, was most influential on my interest in research in general and operating systems in particular. I am grateful to him in many ways: he was a great researcher, excellent teacher, mentor, and friend. This work would not exist without his groundbreaking achievements, the astonishing intellect he had, and his ability to help all of the people around him thrive.

I want to specifically thank Joshua LeVasseur, who is a good friend and colleague. With him, it was not only possible to achieve excellent research results, but also to have a life in Karlsruhe. I hope we will continue to work together over the coming years. Thanks also to Susanne for her endless supply of excellent food and many fun hours.

Thanks to Jan Stöß for his efforts in our joined projects, including but not limited to multiprocessor L4. Andreas Haeberlen and Curt Cramer have both been influential in many ways; I enjoyed the constant technical and political discussions. I still owe Andy a two-lettered rubber stamp. I had endless hours of brainstorming and discussions with Lars Reuther and many of my research ideas (including those in this thesis) were born with him on the other end of the phone line.

I am thankful to the people of the System Research Lab of Intel MTL, in particular Sebastian Schönberg and Rich Uhlig. It was a wonderful time working in such an inspiring environment and getting deep insights into the hardware architecture. Rich is an excellent manager and good friend and was supportive in many ways. Intel supported this research with a generous research grant, which financed the required multiprocessor hardware and also supported me during the last three months of my thesis. I really enjoyed the productive and intellectually challenging work with Sebastian, but also our regular Wednesday evenings at Imbri Hall.

I thank Gernot Heiser for his support, for reading initial drafts of this thesis, and coming over from Australia for the defense. Although we have had many flame wars on internal and external mailing lists, it is always a joy to work with him. I also want to thank Gernot for offering me a PhD position in Sydney when things got rough.

I want to thank Julie Fast for editing the final version of this thesis, and also for her support and encouragement. I also have to thank Monika Schlechte, my sister, and my parents for their constant support on this interesting journey. Monika was probably most influential on the directions of my life including starting a research career. Jan Langert and Michaela Friedrich were of great support during the hardest years of my PhD studies in 2002. I want to thank them for their patience, the uncountable hours on the phone, and their very helpful advice.

I have to thank the people of the System Architecture Group for making L4 and L4Ka::Pistachio such a great success. I want to specifically mention Espen Skoglund and Uwe Dannowski who helped make V4 happen, James McCuller for the most amazing IT environment ever, and Gerd Liefländer for shouldering the primary teaching load and thus enabling our research results (even though Gerd was always skeptical that I will finish on time). Without those people this work would not have been possible. I also want to thank Frank Bellosa, who is now the new head of our group. He has not only been very supportive in the short period we have been working together, but also gave great advice during my interviewing time.

Last, but not least I have to thank the whole L4 community for the insightful discussions on microkernel design. We still have a long way to go and I hope it will be as much fun in the upcoming years.

# **Contents**

| 1 | Intr         | oductio                   | n                                          | 1  |  |

|---|--------------|---------------------------|--------------------------------------------|----|--|

| 2 | Fact         | ts and N                  | Notation                                   | 5  |  |

| 3 | Related Work |                           |                                            |    |  |

|   | 3.1          | Scalab                    | ole Systems                                | 9  |  |

|   |              | 3.1.1                     | Operating System Scalability               | 10 |  |

|   |              | 3.1.2                     | Clustering                                 | 12 |  |

|   | 3.2          | Locks and Synchronization |                                            |    |  |

|   |              | 3.2.1                     | Locks: Software Approaches                 | 14 |  |

|   |              | 3.2.2                     | Locks: Hardware Approaches                 | 15 |  |

|   |              | 3.2.3                     | Lock-free Synchronization                  | 16 |  |

|   |              | 3.2.4                     | Message-based Synchronization              | 16 |  |

|   |              | 3.2.5                     | Read-Copy Update                           | 17 |  |

|   | 3.3          | Partitio                  | oning                                      | 18 |  |

|   |              | 3.3.1                     | Hardware Partitioning                      | 18 |  |

|   |              | 3.3.2                     | Software Partitioning and Virtual Machines | 19 |  |

|   | 3.4          | Microl                    | kernel-based Systems                       | 20 |  |

|   |              | 3.4.1                     | The Microkernel Argument                   | 20 |  |

|   |              | 3.4.2                     | Multiprocessor Microkernels                | 22 |  |

| 4 | Mic          | rokerne                   | el Performance Adaptation                  | 25 |  |

|   | 4.1          | Overvi                    | iew                                        | 26 |  |

|   | 4.2          | Tracki                    | ng Parallelism                             | 29 |  |

|   |              | 4.2.1                     | Processor Clusters                         | 30 |  |

|   |              | 4.2.2                     | Processor Cluster Mask                     | 31 |  |

|   | 4.3          | Kernel                    | Synchronization                            | 33 |  |

|   |              | 4.3.1                     | Trade-offs                                 | 34 |  |

|   |              | 4.3.2                     | Dynamic Lock Primitive                     | 37 |  |

|   |              | 4.3.3                     | Lock Granularity                           | 41 |  |

|   | 4.4          | TLB C                     | Coherency                                  | 44 |  |

|   |              | 4.4.1                     | Independence of Coherency Updates          | 46 |  |

|   |              | 4.4.2                     | Version Vector                             | 47 |  |

viii CONTENTS

|   | 4.5 |          |                                   | 1      |

|---|-----|----------|-----------------------------------|--------|

|   |     | 4.5.1    |                                   | 2      |

|   |     | 4.5.2    | Data Accumulation                 | 2      |

|   |     | 4.5.3    | Event Sources and Groups          | 4      |

|   |     | 4.5.4    | Log Entries and Log Configuration | 5      |

|   |     | 4.5.5    | Log Analysis                      | 6      |

|   | 4.6 | Summa    | ary                               | 9      |

| 5 | App | lication | to the L4 Microkernel             | 1      |

|   | 5.1 | Overvi   | ew of L4                          | 2      |

|   | 5.2 | Require  | ements                            | 3      |

|   |     | 5.2.1    | Design Goals                      | 3      |

|   |     | 5.2.2    |                                   | 5      |

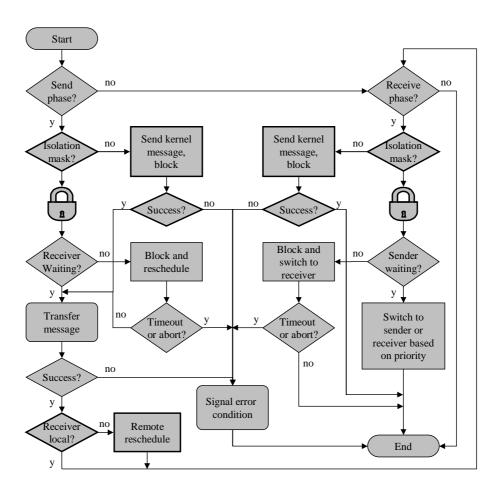

|   | 5.3 | Inter-p  | rocess Communication              | 7      |

|   |     | 5.3.1    |                                   | 7      |

|   |     | 5.3.2    |                                   | 2      |

|   |     | 5.3.3    |                                   | 3      |

|   |     | 5.3.4    |                                   | 3      |

|   |     | 5.3.5    |                                   | 5      |

|   | 5.4 |          |                                   | 6      |

|   |     | 5.4.1    |                                   | 7      |

|   |     | 5.4.2    | , ,                               | '8     |

|   |     | 5.4.3    | J .                               | 80     |

|   |     | 5.4.4    | 11 &                              | 34     |

|   | 5.5 |          | ,                                 | 88     |

|   | 3.3 | 5.5.1    | , E                               | 88     |

|   |     | 5.5.2    | 26 6                              | 1      |

|   |     | 5.5.3    |                                   | 3      |

|   | 5.6 |          |                                   | ر<br>4 |

|   | 5.0 | Sullilli | 11.9                              | 4      |

| 6 | _   |          |                                   | 7      |

|   |     |          |                                   | 7      |

|   | 6.2 | •        |                                   | 9      |

|   |     | 6.2.1    |                                   | 9      |

|   |     | 6.2.2    | Cross-processor IPC               | 1      |

|   |     | 6.2.3    | Parallel Programming              | 2      |

|   |     | 6.2.4    | Scalability and Independence      | 15     |

|   | 6.3 | Event I  | Logging                           | 6      |

|   | 6.4 | Memor    | ry Management                     | 7      |

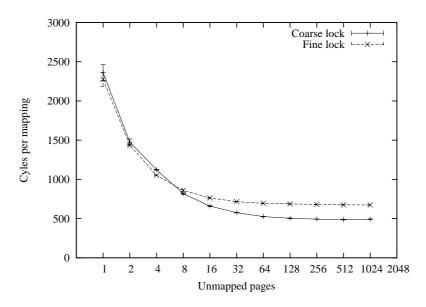

|   |     | 6.4.1    | Locking Overhead                  | 8      |

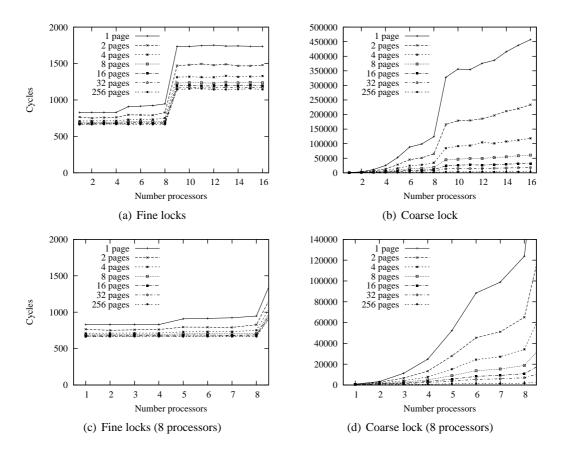

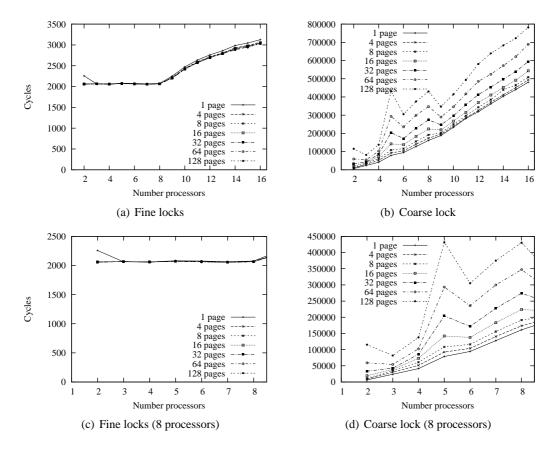

|   |     | 6.4.2    | Scalability                       | 19     |

|   | 6.5 | Summa    | ary                               | 2      |

CONTENTS ix

| 7 | Conclusion |                             |     |  |  |  |

|---|------------|-----------------------------|-----|--|--|--|

|   | 7.1        | Contributions of This Work  | 115 |  |  |  |

|   | 7.2        | Suggestions for Future Work | 116 |  |  |  |

|   | 7.3        | Concluding Remarks          | 117 |  |  |  |

CONTENTS

## **Chapter 1**

## Introduction

In the last years two important trends are changing the systems area: First, performance scaling by increasing processor frequency is reaching the point where further frequency increases are uneconomical. The current leakage that is inherent in small structure size of today's high-frequency processors results in massive energy dissipation that is emitted as heat. In order to further increase compute power, processor development is switching the focus to increasing parallelism. All primary processor vendors are providing or announcing systems with a large number of tightly coupled processors, that have previously been only available in mainframe-class systems.

Second, the increasing variety of usage cases of computers as multi-purpose devices is setting new demands on operating systems which remain unfulfilled by traditional operating systems, such as UNIX and Windows. These new demands require radical new system designs, and cannot be achieved by simply extending the existing systems with new features. Examples of these requirements are higher level of security and confidentiality of critical information, real-time support, and safe sharing of hardware resources in consolidated server environments of potentially untrusted clients.

I argue, that microkernels present a viable alternative for structuring operating systems that fulfill these new system requirements *if they scale on large multiprocessor systems*.

Scalability of operating systems for shared-memory multiprocessors is a complex problem that requires careful design of the complete software stack. The complexity stems from the structure of the underlying hardware architecture. With an increasing number of processors resource access latencies are non-uniform which has to be considered by the operating system. Naïve synchronization and resource allocation schemes that are efficient in smaller multiprocessor systems often lead to resource contention, starvation, high overhead, and ultimately to system saturation on more sophisticated hardware.

The operating system is an omnipotent software layer on top of the hardware and therefore a crucial contributor to overall scalability. It manages and multiplexes

all hardware resources and mediates them between the competing applications. Depending on resource usage patterns, the degree of resource sharing, object scope, and object granularity, the operating system selects the most appropriate and efficient synchronization algorithm, and thereby minimizes overhead and maximizes scalability. The choice for the optimal algorithm requires detailed semantic information about system subjects and objects. For example, the relevant literature differentiates between as many as ten different synchronization schemes.

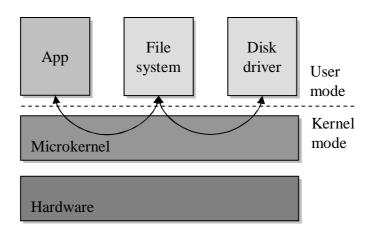

In microkernel-based systems, the microkernel is only a very thin software layer that multiplexes the hardware between isolated or cooperating entities in a secure, safe, and extensible manner. The managed resources are limited to basic memory pages, processor resources, and processor time. All high-level operating system abstractions, such as file systems, network stacks, and device drivers are implemented as unprivileged user-level servers.

This system structure drastically reduces the complexity of the kernel itself and previous research validates that it is possible to construct real-time [53] and secure systems [90] on a microkernel. However, moving operating system constructs out of the kernel also eliminates detailed semantic information that is required to achieve optimal scalability. The microkernel lacks the necessary information to make an educated decision on the most efficient strategy.

Previous research on multiprocessor microkernel systems therefore compromised either on the scalability aspect (by choosing one specific synchronization policy), or on the strict separation of mechanism and policy and blurred the line between kernel and applications. The latter approach looses the desired properties of a microkernel.

In this thesis I present solutions that allow for an uncompromised microkernel design while achieving excellent scalability with low overhead. My solutions comprise four areas: I developed a space and time efficient tracking scheme for parallelism allowing every kernel object to be tagged with a processor mask. Using the tracking mask, the kernel derives the potential concurrency on kernel objects and adjust its synchronization scheme.

I developed *dynamic locks* that can be safely enabled and disabled at runtime thus eliminating synchronization overhead while still guaranteeing functional correctness in the kernel. Based on the dynamic locking scheme, I derived a method for dynamically adjusting the *lock granularity* for divisible objects. This provides applications with control over lock granularity in the microkernel. Applications can dynamically choose between coarse-grain locking for lower runtime overhead or fine-grain locking for a higher level of parallelism.

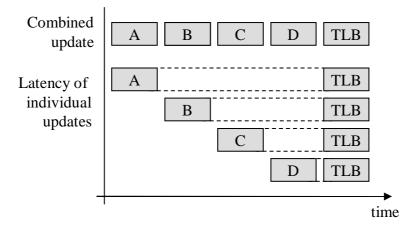

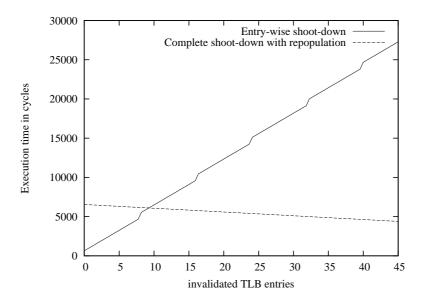

Memory is a primary resource managed at application level but enforced by the microkernel. Besides synchronization on kernel meta data, the microkernel has to enforce coherency of the translation look-aside buffer (TLB). I present an algorithm that decouples memory permission updates from outstanding TLB updates. With this scheme, multiple processors can manipulate permissions to memory objects in parallel while still minimizing the overhead for TLB coherency updates.

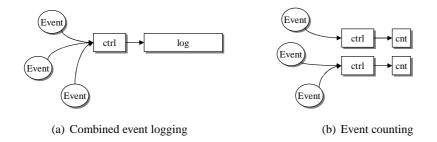

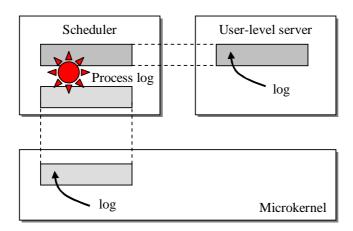

Finally, I present a low-overhead event logging mechanism that transfers

scheduling-relevant resource usage data between system components. The mechanism uses memory as a high-bandwidth and low-overhead transport mechanism and thereby only induces a marginal runtime overhead. It enables application-level schedulers to efficiently manage and allocate kernel resources, such as allocating threads to processors and also managing the per-processor kernel memory pools.

I describe the application of my techniques to a real system: L4Ka::Pistachio, the latest variant of an L4 microkernel. I played a significant role in the design and development of L4Ka::Pistachio. At this time, it supports nine different hardware architectures and is used in a number of industry and research projects. Introducing a new dimension to a system — parallelism of multiprocessors — naturally introduces new complexity and overheads. I evaluate my solutions by comparing with the most challenging competitor: the uniprocessor variant of the very same and highly optimized microkernel.

I see my contribution as extending minimalistic microkernel design, epitomized by L4, to the important domain of multiprocessors. However, the solutions are not restricted to microkernels, but are also applicable in the area of virtual machines, monolithic operating systems and even applications.

### **Organization**

This thesis is structured as follows: In Chapter 2, I define common terms and principles required for the following sections. In Chapter 3, I evaluate related work on synchronization, scalability of multiprocessor operating systems in general, and microkernel-based systems in particular.

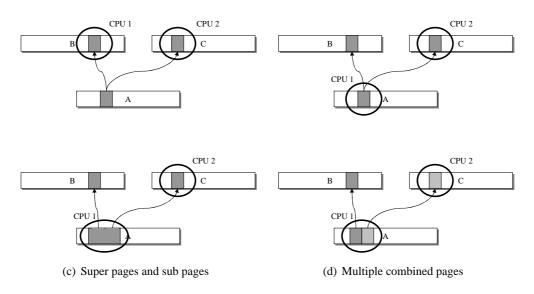

In Chapter 4, I develop my principles for adaptive synchronization primitives for the kernel. In Section 4.1, I discuss the structural differences of microkernel-based systems as compared to traditional operating systems for large multiprocessor systems. Then, I develop my resource tracking scheme (Section 4.2) which forms the foundation for the dynamic locking scheme described in Section 4.3. In Section 4.4, I describe the TLB coherency tracking algorithms that decouples memory permission management and TLB coherency updates. Finally, in Section 4.5, I develop the event-logging mechanism that enables the microkernel and isolated system components to efficiently exchange resource usage information that is required for user-level scheduling and multiprocessor resource allocation policies.

Chapter 5 shows how I applied my methodology to L4Ka::Pistachio, an L4 microkernel. In Section 5.1, I give a general overview of L4 primitives required for the later development. In Section 5.2, I specify functional and performance requirements and define design goals and non-goals. I then introduce the multiprocessor extensions to the uniprocessor kernel abstractions. In Section 5.3, I describe the implications of parallelism to L4's most performance-critical primitive: interprocess communication (IPC). I use dynamic locks for IPC to eliminate the synchronization overhead for the most important common cases. Section 5.4 details scalable user-level memory management applying dynamic locking and the

TLB coherency scheme to L4. Finally, in Section 5.5, I show how event-tracing can be used to manage kernel memory and threads via a user-level scheduler.

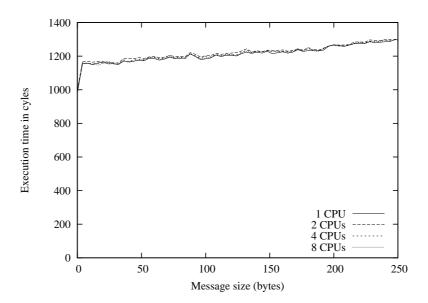

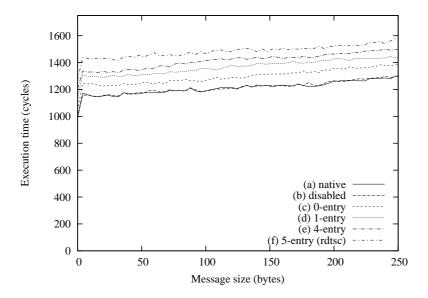

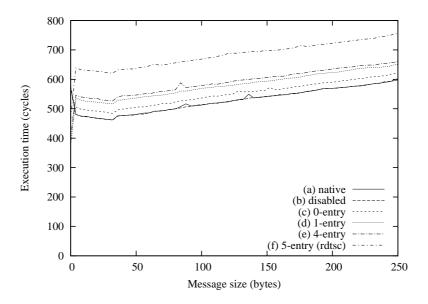

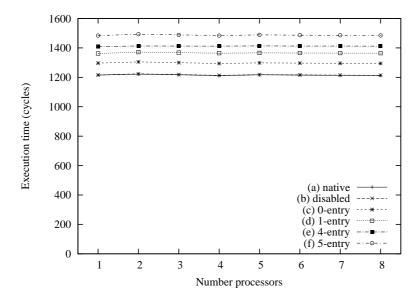

In Chapter 6, I evaluate the performance of my design for L4Ka::Pistachio. After detailing the peculiarities of my evaluation platform in Section 6.1, I evaluate the performance and scalability of the multiprocessor IPC primitive on the same and different processor (Section 6.2), the event logging scheme (Section 6.3), and user-level memory management (Section 6.4).

Chapter 7 includes a summary and suggestions for future work.

## **Chapter 2**

## **Facts and Notation**

In this chapter I introduce common terminology and principles of operating systems and multiprocessor hardware that is used throughout the later chapters in this dissertation.

#### **Operating System and Microkernels**

An operating system (OS) is a program (or a set of programs), which mediates access to the basic computing resources provided by the underlying hardware. Most operating systems create an environment in which an application can run safely and without interference from other applications. In addition, many OSes provide the application with an abstract, machine independent interface to hardware resources that is portable across different platforms.

There are two popular views of an operating system: The operating system as a resource manager or the operating system as an abstract virtual machine.

The view of a resource manager has the operating system acting as an arbiter for system resources. These resources include disks, networks, processors, time and others. The resources are shared among the various applications depending on individual applications' requirements, security demands, and priority.

An alternative view of operating systems is that of an abstract virtual machine. Each virtual machine provides a level of abstraction that hides most of the idiosyncrasies of lower-level machines. A virtual machine presents a complete interface to the user of that machine. This principle can be applied recursively.

An operating system provides an interface to its applications to enhance the underlying hardware capabilities. This interface is more portable, provides protection among competing applications, and has a higher level of abstraction than bare hardware. Briefly, operating systems typically provide services in the following areas: (*i*) program creation, (*ii*) program execution, (*iii*) access to I/O devices, (*iv*) controlled access to devices, (*v*) error detection and response, and (*vi*) accounting.

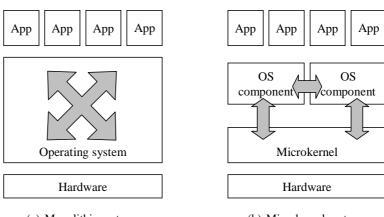

A number of different architectural organizations are possible for an operating system; the two most relevant structures are *monolithic* and *client-server*. In the monolithic system, all OS functions are integrated into a single system image.

The advantage is good performance with the disadvantage of high complexity. In monolithic systems, all subsystems share the same protection domain and faults in one subsystem can propagate into others. Client-server systems employ a *microkernel*, that mediates resource access to the bare hardware. The OS subsystems are implemented as applications that run in their own address space. The microkernel provides inter-process communication for interaction between the subsystems. Microkernels provide significantly better fault isolation because subsystems are confined to their own protection domain.

#### **Multiprocessor Systems**

In multiprocessor systems, multiple connected processors operate in parallel. Depending on the processor interconnect, the systems are differentiated in (i) *clusters* (or multicomputers) and (ii) *shared memory multiprocessors*. In clusters, each processor has its dedicated memory and is an autonomous computer; the computers communicate via a network. Shared memory multiprocessors have common memory for code and data and communication between processors may take place via shared memory.

One general classification of shared memory multiprocessors is based on how processes are assigned to processors. The two fundamental approaches are *master/slave* and *symmetric*. For master/slave, the operating system always runs on a particular processor and the other processors execute applications. In *symmetric multiprocessor systems* (SMP), the operating system can execute on any processor.

For a small number of processors, multiprocessor systems commonly use a *shared memory bus* that connects all processors and the memory. The shared bus structure limits the overall memory bandwidth, because only one processor can access the bus at a time. With an increasing number of processors, the shared bus becomes a performance bottleneck. Large scale systems therefore use either multiple interconnected buses or per-processor memory. The buses are interconnected via memory routers. These systems, however, exhibit different access latencies for memory that is local to the accessing processor compared to remote memory. The *non-uniform memory access* property gave the systems their name: NUMA.

With the increasingly high integration, two other multiprocessor structures become more common: *simultaneous multithreading* (SMT) and *chip-level multiprocessing* (CMP). SMT uses the multiple-issue-per-instruction features of modern superscalar processors to hide latencies of resource stalls, such as cache misses. SMT processors [108] provide multiple threads of execution that share the functional units of one processor. On resource stalls the processor automatically switches to another thread. The primary goal of SMT is to increase the utilization of functional units of one processors.

CMP is an SMP implemented on a single chip. Multiple processor cores typically share a common second- or third-level cache and interconnect. CMPs are also often referred to as multicore processors.

#### **Caches**

Cache memory is intended to give memory speed approaching that of the fastest memory available, and at the same time provide a large memory size at the price of less expensive memory. The cache contains a copy of portions of main memory. When the processor attempts to read a word of memory, a check is made to determine whether the word is in the cache. If so, the word is delivered to the processor, otherwise a block of memory is fetched from main memory into the cache.

A consistency problem arises in multiprocessor systems, where each processor has its own cache. When one processor modifies a datum, the other processors' caches may still contain the old value, which is now incorrect. *Cache coherency mechanisms* that are implemented in hardware transparently update the processor caches. In bus-based systems processors can *snoop* the memory bus for addresses that they have cached. When a write operation is observed to a location that a cache has a copy of, the cache controller invalidates its own copy. Various models and protocols have been devised for maintaining cache coherency (e.g., MESI, MSI, MOSI, and MOESI).

In cache-coherent NUMA systems (ccNUMA), processors have no common memory bus prohibiting cache snooping for cache coherency. Instead, ccNUMA systems use directory tables to keep track of which processors cache a specific word. On modification, the hardware sends directed update and invalidate messages to the processors. This scheme has a significantly higher overhead compared to snoopy caches and requires specific attention when designing a system.

#### **Memory Management Unit**

The memory management unit (MMU) of a processor is responsible for handling memory accesses requested by the CPU. Among others, the MMU translates virtual address to physical addresses (to implement virtual memory), it enforces memory protection, and controls the caching strategy. The virtual address space is divided into pages of a size of  $2^N$ , usually a few KBytes. When accessing memory, the lower N bits remain unchanged while the upper bits select the (virtual) page number. The page number is used to index into a *page table*, that contains the translation from virtual address to the physical memory page.

To reduce the translation latency, processors cache page table entries in the *translation look-aside buffer* (TLB) [66]. TLBs work similarly to normal caches and contain the page table entries most recently used. Given a virtual address, the processor will first inspect the TLB, and if the page table entry is present (i.e., a TLB hit) the physical address is retrieved. Otherwise, the processor examines the page table and if a valid entry is found the entry is loaded into the TLB. If the page table contains an invalid entry, the processor signals a page fault exception to the operating system.

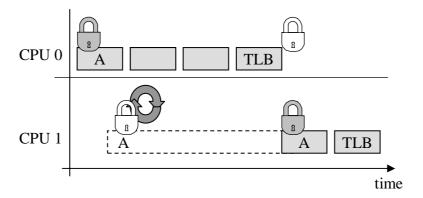

Similar to memory caches, TLBs need to be kept coherent between multiple processors. While cache coherence for memory is implemented in hardware, en-

forcement of TLB coherence is left to the operating system. When updating a page table entry, the operating system has to specifically issue a *TLB invalidation* instruction. With very few exceptions, architectures require explicit invalidation of TLB entries on remote processors. The updating processor sends an inter-processor interrupt (IPI) to the remote processors, which then invoke the TLB invalidation instruction updating their respective TLB. This remote invalidation is commonly referred to as *TLB shoot-down*.

## Chapter 3

## **Related Work**

Related work to this thesis can be classified into the following four areas:

**Scalable systems.** My thesis proposes a number of mechanisms that control and adjust kernel algorithms for resource allocation and management. In Section 3.1 I discuss the general problem of multiprocessor scalability. I review previous work that addresses the problem of operating system scalability, discuss the relevant findings and relate them to my work.

**Locks and synchronization.** Locks are an important primitive for mutual exclusion in multiprocessor systems but also a main source for limited scalability and overhead. My thesis proposes an adaptable locking mechanism. In Section 3.2 I describe the scalability problem of locks and other approaches that address lock overhead and lock contention in scalable systems.

**Partitioning.** I use resource partitioning to isolate independent subsystems and thereby avoid potential interference. In Section 3.3 I review other approaches — software and hardware — that use resource partitioning to achieve better scalability.

**Microkernel-based systems.** This thesis investigates scalability of microkernels. As the disappointing performance results of early approaches have shown, microkernels require careful design and implementation. In Section 3.4 I describe the state of the art in microkernel-based systems laying the ground for many design decisions, but also discuss other related work in the field of microkernels on multiprocessors.

### 3.1 Scalable Systems

Multiprocessor scalability is addressed at various levels of the system stack: the hardware level, the operating system, and the application and algorithmic level.

At the hardware level, a higher degree of circuit integration and the limitations of frequency scaling puts a stronger focus on parallelism. Most microprocessor

vendors ship now or have announced multicore versions of their processors, and offer multiprocessors based on a single shared bus. Single bus systems, however, are not scalable beyond a small number of processors. Because of this, the memory bus becomes the system's performance bottleneck.

The first scalable shared-memory machines are based on Omega 0 networks [101], such as the NYU Ultra-Computer [3], the IBM RP3 [89], and the BBN Butterfly [28]. In these systems, each processor has locally accessible memory, but is able to access the memory of remote processors via the memory interconnect. Accesses to remote memory have a higher latency than to local memory. The non-uniformity for memory accesses gives these machines their name: *NUMA*. Alternative interconnect structures are ring or grid topologies, as used by the Stanford DASH [68] and KSR [24] architectures, and the HECTOR [118] multiprocessor.

A critical design issue of all shared memory architectures is the cache coherency scheme. Each processor in a multiprocessor system has its own cache; hence data can appear in multiple copies among the various caches. Cache coherence ensures that all processors have identical copies of a datum. In shared bus systems, snoopy caches [11] provide a very simple method for cache coherence, whereas NUMA systems employ directory-based cache-coherency approaches [50]. In this scheme, a directory keeps track of which processors have cached a given memory block. When a processor wishes to write into that block, the directory sends point-to-point messages to processors with an updated copy, thus invalidating all other copies.

Cache-coherency updates and cache-migration costs are the prime limiting factors for scalability and need to be considered for software and system construction. The overhead for cache-coherency updates has implications on all areas of multiprocessor systems, including the selection of synchronization primitives (such as locks), the overhead for data sharing between processors, and for memory allocations in order to reduce the cost for memory accesses.

The metric for software scalability is speedup. According to Amdahl's law [4], the maximum speedup that parallelism can provide is bounded by the inverse of the fraction that represents the serial portion of the task. Theoretical parallel computing models, such as PRAM [38, 87] and LogP [31], provide abstractions of hardware machines in a portable high-level manner. For example, LogP incorporates four parameters into its model: communication latency, communication overhead, the gap between consecutive messages, and the number of processors. However, LogP and PRAM assume that they can distribute the workload across processors and model a strategy for load distribution. This strategy is not applicable to operating systems and therefore theoretical models consider the operating system as a given extension of the hardware platform.

#### 3.1.1 Operating System Scalability

Unrau's thesis [113] is probably the first that addresses operating system scalability in a new and systematic manner. Instead of addressing the algorithmic speedup, he

proposes the concept of the operating system as a *service center*. His work bases the scalability evaluation on queuing theory [65] with the three fundamental performance metrics: throughput, utilization, and response time. Based on his analysis, Unrau derives the following three fundamental design criteria for a scalable operating system that are quantified as runtime overhead of an operating system function.

**Preserving parallelism:** The operating system must preserve the parallelism afforded by the application. If several threads of an executing application request independent operating system services, then they must be serviced in parallel. Otherwise the OS becomes a bottleneck limiting scalability and application speedup.

**Bounded overhead:** The overhead for each independent operating system service call must be bounded by a constant, independent of the number of processors. If the overhead of each service call increases with the number of processors, the system will ultimately saturate.

**Preserving locality:** The operating system must preserve the locality of the application. It is important to consider the memory access locality in large-scale systems, because many large scale multiprocessors have non-uniform memory access times, where the cost of accessing memory is a function of the distance among accessing processors, and because cache consistency incurs higher overhead in large systems.

While these three design principles are a necessary requirement for scalable systems, they are not sufficient for the following reason: Unrau's requirements only address the scalability of a *given system*. This approach leaves two important aspects unaddressed: *overhead* and *isolation*.

According to Unrau's first and second design rule, a system is still considered scalable if the actual execution time of a function is significantly higher than the achievable minimum. The problem thereby is to determine the minimally achievable overhead, which depends on the specific system scenario and on the number of processors.

In order to determine the minimal overhead, I propose to incorporate an additional aspect: the *isolation property* of an operation. This proposal is based on the following observation from hardware partitioning: Hardware partitioning divides a large multiprocessor system into a set of independent smaller systems. The individual subsystems are fully isolated and behave (almost) like a physically partitioned multiprocessor system. Most importantly, the isolated subsystems *preserve* their performance and scalability properties. Hence, the achievable minimum overhead for an operation, which is executed on (or affects) only a subset of the processors of the system, should be identical to the overhead of a system of the size of the subsystem.

The overhead of an operation is a function of its isolation boundaries; the boundaries are represented by the processors affected by the operation. I propose

a fourth design rule that addresses the overhead of a system function in relation to its isolation boundaries:

**Preserving isolation:** The operating system must preserve the isolation properties of an application. When applications are restricted to a subset of processors, the overhead for a system operation should be identical to the overhead of a system with the size of the processor subset.

An implication of that requirement is that the cost for operations which are restricted to a single processor should also have the overhead of a single-processor system.

A system with more processors has an inherently higher management overhead. This overhead includes memory resources that need to be allocated and more complex algorithms in order to accommodate hardware peculiarities which do not exist in smaller hardware configurations. Therefore, it is hard to strictly follow the postulated isolation requirement. However, in some cases it is possible to trade memory footprint against less performance for the uncommon case.

Unrau's third design rule addresses the special case of NUMA access overhead. More generally, the operating system should use memory that is isolated to one (or a subset) of the system's processors.

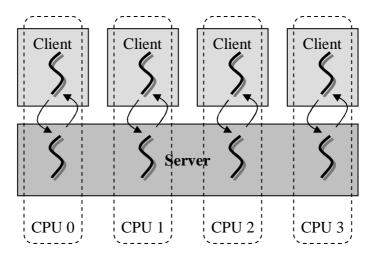

#### 3.1.2 Clustering

Hierarchical clustering is a way to structure shared-memory multiprocessor operating systems for scalability [113,114]. The basic unit of structuring is a cluster. A cluster provides the functionality of an efficient, small-scale SMP that comprises a small number of processors only. On larger systems, multiple clusters are instantiated such that each cluster manages a group of neighboring processing modules. A processing module consists of a small number of processors, local memory, and the memory interconnect. Major system services are replicated to each cluster so that independent requests can be handled locally. In a later paper, Gamsa et al. [41] list a number of problems with this approach, including poor locality, increased complexity, and difficulties to support customized policies.

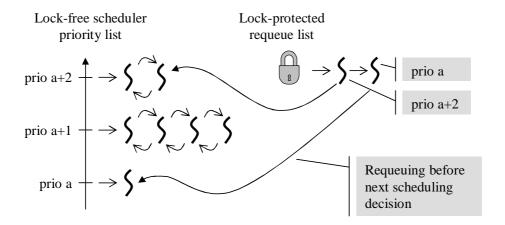

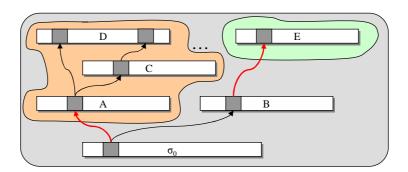

Clustered objects [7,41] (as used in Tornado and K42) extend the idea of a clustered system structure to the OS object granularity (i.e., a C++ object instance). A clustered object presents the illusion of a single object but is actually composed of multiple object instances. Each individual instance handles calls from a subset of the processors and the object instance presents the collective whole for all processors. The specific implementation of clustered object instance can differ to reflect the degree of parallelism and access patterns. The key to the implementation is the use of a per-processor translation table that contains a reference to a handling method. The indirection table allows the creation of object representatives on demand by installing a default fault handler in the table. When an object is first referenced on a processor, the default handler catches the access attempt and instantiates a local representative.

Clustered objects are a powerful method for runtime adaptation. In particular, it is possible to dynamically replace object code and the object's synchronization models via the indirection table. The faulting scheme, however, creates the problem that it only supports a forward scheme. The per-processor representatives are established on access fault. There is no similar event for the destruction of representatives and a fall-back to a less-scalable scheme that may incur a lower overhead. While the authors describe a garbage collection mechanism very similar to read-copy-update, there is no equivalent for a down-sizing (or de-parallelization) of a clustered object. While this may not impose a problem for short-lived kernel objects, it is critical for long-lived objects with significantly changing access patterns, as seen in microkernels with user-level resource management.

### 3.2 Locks and Synchronization

Locks provide individual processors with exclusive access to shared data and critical sections of code. The most common locks for in-kernel synchronization are *spin locks*, where a shared memory location stores the lock state (i.e., taken or free). In order to acquire the lock, the processor atomically replaces the content of the lock variable with the value that denotes a taken state. If the previous value was *free*, the lock was acquired successfully, or otherwise the processor retries in a loop.

The overhead for locks falls into three different categories: (*i*) the runtime overhead for the lock primitive itself, (*ii*) the cache footprint for the lock, and (*iii*) utilization of memory bus bandwidth.

Locks are implemented with atomic processor primitives. A variety of alternative atomic primitives have been proposed and implemented on shared memory architectures in order to minimize locking overheads. Many of those special primitives support one particular synchronization operation [45, 59, 68]. Although special-purpose primitives have advantages in certain scenarios, common processor architectures support a set of general-purpose primitives, such as FETCH&Ф [46], COMPARE&SWAP [25], and the pair of LOADLINKED-STORECONDITION-AL [61].

• The FETCH& $\Phi$  primitive takes two parameters: the address of the destination and a value parameter. The primitive atomically reads the value from the destination, computes the new value as  $\Phi$ (original value, parameter), stores it, and returns the original value.

Example primitives are TEST&SET, FETCH&ADD, and FETCH&STORE<sup>1</sup>.

• COMPARE&SWAP takes three parameters: the address of the destination, an expected value and a new value. If the original value at the destination

<sup>&</sup>lt;sup>1</sup>FETCH&STORE is also known as EXCHANGE that atomically replaces a register value with a memory location. It is the atomic operation with the lowest overhead for IA32.

address is identical to the expected value, it gets replaced atomically with the new value. The return value indicates success or failure.

• The pair LOADLINKED-STORECONDITIONAL must be used together to read, modify, and write a shared location. LOADLINKED returns the value stored at the shared location and at the same time sets a reservation associated with processor and location. The reservation remains valid until another processor accesses the recorded cache line. STORECONDITIONAL checks the reservation; if valid it writes the new value and returns success, otherwise failure. The reservation is commonly implemented in the processor cache and invalidation can be easily embedded in the cache snooping protocol. When a STORECONDITIONAL fails it fails locally and does not cause any bus traffic.

#### 3.2.1 Locks: Software Approaches

The naïve use of atomic operations can induce significant overhead in larger multiprocessor systems. Processors that compete for a lock create memory bus traffic due to the cache coherency protocol. Alternative locking schemes, such as Mellor-Crummey Scott locks (MCS locks) [82], reduce the overhead with locking queues and employ spinning on local memory. Local spinning reduces the overhead of the cache coherence protocol from all competing processors to one.

The optimal synchronization scheme depends on the peculiarities of the scenario, such as the level of contention, the memory interconnect of competing processors, and access frequency and pattern. Less concurrency and less complex memory interconnects (such as simple snoopy caches of SMP systems) also require less complex lock mechanisms and code paths, thus reducing runtime overhead and cache footprint.

Overhead and complexity increases when locks are contended and lock attempts cross NUMA node boundaries. However, no single best locking scheme exists. Anderson [6] observed that the choice between spin-locks and MCS queue locks depends on the level of lock contention. Lim [76] proposes dynamic runtime adaptation between both lock protocols. Depending on the degree of lock contention the code adapts the lock protocol. For low contention cases (with less than four processors) the scheme uses spin locks with the significantly lower runtime overhead, whereas in high contention cases the more expensive, but better scalable, MCS locks are used.

McKenney [79] argues that the choice for the best locking strategy depends on a large number of factors, such as duration of critical section, read-to-modify ratio, contention, and complexity. He differentiates as much as ten alternative design patterns for choosing an optimal locking strategy.

Unrau et al. [115] address the problem of overhead vs. parallelism for fine granular locks. They propose a hybrid coarse-grain/fine-grain locking strategy that has the low latency and space overhead of a coarse grain locking strategy while having the high concurrency of fine-grain locks. The idea is to implement fine-granular locks using non-atomic memory operations and protect the lock data structures with a single coarse lock. The coarse lock must be held in order to acquire the fine granular locks, which then can be implemented as a simple reserve bit. When spinning on the lock, only the reserve bit is tested and does not require an acquisition of the coarse lock.

The scheme has two limitations. First, the coarse lock still has to be taken by *all processors* and thus needs to be migrated between the different processor caches. Real fine granular locks can eliminate that inter-dependency and overhead. Second, in order to reduce contention on the coarse lock, processors spin on the reserve bit of the object. Only when the reserve bit gets cleared do the processors retry the lock acquisition via the coarse lock. That scheme puts restrictions on object destruction and prohibits free memory reuse. A lock that is embedded in an object which is released and re-allocated may never be cleared. Processors that are spinning on such a lock will spin infinitely. The authors solve this problem by introducing object classes for memory in order to guarantee that the particular reserve bit reaches an unlocked state.

#### 3.2.2 Locks: Hardware Approaches

In addition to software-based approaches, research proposes special hardware support in order to minimize the lock overhead.

Goodman et al. proposed the Queue-On-Lock-Bit primitive (Qolb) [45] that was also the first proposal for a distributed, queue-based locking scheme. Qolb maintains a hardware queue of waiting processors in the cache so that processors can spin locally. On lock release the first processor in the queue receives a specially formed cache-coherency packet; the other processors remain spinning. Kägi et al. [63] compares the throughput of Test&Set locks, Test&Test&Set locks [95], MCS locks, LH locks [77], M locks [77], and Qolb locks. The Qolb locks outperform all other lock mechanisms, however, the locks rely on support of the special Qolb primitive. The simple Test&Set and Test&Test&Set locks performs well under low contention but throughput degenerates quickly for more than four processors.

Rajwar et al. [92] reduce the runtime overhead for locks via *speculative lock elision* (SLE). SLE is a micro-architectural technique similar to speculative execution. The processor dynamically identifies synchronization operations, predicts them as unnecessary, and elides them. By removing these operations, the program behaves as if synchronization were not present in the program. Conflicts that would violate the correctness due to the missing synchronization primitives, are detected via the cache-coherency mechanisms and without executing the actual synchronization operations. Safe dynamic lock removal exploits the properties of locks and critical sections as they are commonly implemented. If data is not concurrently accessed between the lock acquisition and release operations, both operations can be elided. Data written within the critical section is buffered in an intermediate

buffer while monitoring the lock variable. If the operation completes without a violation of atomicity, the buffer is written back. Otherwise the operation is restarted with a normal lock.

Speculative lock elision addresses the problem of the high overhead for lock primitives in cases of no concurrency. While SLE is a generic and transparent solution it has limitations. SLE requires an extension of the hardware microarchitecture and is thus not applicable to currently available hardware architectures. The size of the critical section is further limited by the size of the write buffer. Since the processor monitors the cache line of the lock, SLE induces cache and memory footprint for the lock variable. Furthermore, nesting of locks requires multiple locks being monitored concurrently.

#### 3.2.3 Lock-free Synchronization

An alternative to lock-based synchronization is lock-free synchronization. Critical code sections are designed such that they prepare the results out of line and then try to commit them using an atomic update instruction such as COMPARE&SWAP. The most prominent operating systems using lock-free synchronization are the Cache kernel [48], Synthesis [78], and Fiasco [58], which is an L4 microkernel variant. (A more detailed discussion of Fiasco follows in Section 3.4.2.)

The Cache kernel and Synthesis run on architectures with a COMPARE&SWAP2 instruction (Motorola 68K). The authors report lock-free synchronization as a viable alternative, however, they do not address the performance implication due to frequent atomic operations or lock contention. For example, the SYNTHE-SIS kernel was only tested on a two-way machine with a shared memory bus and the CACHE kernel on a four-way machine. The authors argue that the overhead induced by lock-free synchronization in number of *instructions* is minimal. However, the overhead of the COMPARE&SWAP2 operation is reported to be as high as 114 cycles. The reported overhead for a variety of common kernel operations using lock-free synchronization vs. unsynchronized operations is between 50 up to 350 percent.

Lock-free synchronization via atomic operations further eliminates the possibility for *critical-section fusing* [79], where multiple critical sections are protected by a single lock. Hence, while a single lock may be highly sufficient, scalable, and induce a very low overhead, the lock-free synchronization scheme adds the overhead of an atomic COMPARE&SWAP2 to every critical section.

#### 3.2.4 Message-based Synchronization

Chaves et al. [26] discuss alternative in-kernel synchronization schemes for large-scale shared memory multiprocessors. The authors distinguish between three primary synchronization mechanisms for kernel–kernel communication:

**Remote memory access:** The operation executes on processor i reading and writing processor j's memory as necessary.

**Remote invocation:** Remote invocation is based on sending a message from processor i to processor j asking j to perform the operation on behalf of i.

**Bulk data transfer:** The kernel moves the data required by the operation from processor *j* to *i*, where it is inspected or modified and possibly copied back.

The work discusses the performance trade-offs for the different synchronization schemes. The authors conclude that the choice between remote invocation and remote access is highly dependent on the cost of the remote invocation mechanism, the cost of the atomic operations used for synchronization, and the ratio of remote to local memory access time. Although, coming to this conclusion, the authors do not discuss methods on *how* to resolve the open problem.

A number of operating systems use in-kernel messaging for synchronization: most prominent are the DragonFly BSD project [1], which bases most in-kernel synchronization on inter-processor interrupts, and Tornado [41].

I am not aware of any previous work which provides the choice for dynamic selection of message *and* lock based synchronization in one kernel.

#### 3.2.5 Read-Copy Update

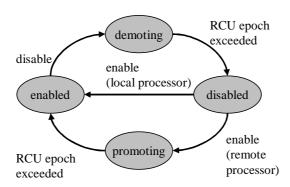

For read-mostly data structures, performance can be greatly improved by using asymmetric locking primitives that provide reduced overhead for read-side accesses in exchange for more expensive write-side accesses. *Read-copy update* (RCU) [80, 81] takes the idea to the extreme, permitting read-side accesses with no locking or synchronization. This means that updates do not block reads, so that a read-side access that completes shortly after an update can return old data.

Data structures in parallel systems cannot be considered stable unless a particular update policy is followed, such as holding locks to data. After the locks are released, the system cannot make any prior-knowledge assumptions about the state of the data which was protected by the locks. Thus, if a thread does hold no lock, it cannot make any assumption about *any* data structure that is protected by any lock. When a thread holds no locks, it is in a quiescent state with respect to any lock-protected data.

The fundamental idea of read-copy update is the ability to determine when all threads have passed through a quiescent state since a particular point in time. Afterward, it is guaranteed that the threads see the effects of all changes made prior to the interval. This guarantee significantly simplifies many locking algorithms and eliminates many existence locks.

The processors signal the event of passing a quiescent state by circulating a token. When the processor that currently possesses the token reaches a quiescent state, it passes on the token to the next processor. A new *RCU epoch* starts with completion of a full round trip of the token. By then it is guaranteed that all processors have passed a quiescent state; thus the effects of an operation of the previous epoch are complete and globally visible.

Operating systems have well-known code paths, where it is structurally guaranteed that the current thread does not hold locks and thus are in a quiescent state. Examples of these code paths include when a thread exits from kernel to application level, as well as when the processor enters the idle loop, or on context switches.

Read-copy update is used in a variety of scenarios in operating systems, such as deferred deletion of list members or module existence locks for kernel-loadable modules. In this thesis I apply the core idea of RCU to a novel domain: *kernel lock primitives*.

### 3.3 Partitioning

Multiprocessor partitioning divides a large multiprocessor system into a set of independent, smaller multiprocessor subsystems. Each subset acts relatively autonomously and independent of the others. The strict independence between partitions eliminates interference, information leakage as well as restricts the level of parallelism within each partition. The scalability requirements for an operating system in a partition are therefore limited by the physical resources (i.e., processors) allocated to it.

Partitioning shares a subset of goals with scalable microkernel-based systems. The hard boundaries eliminate the overhead induced by a high degree of parallelism, such as cache and TLB coherency, and also restrict the degree of parallelism and thus the possibility for contention. Hence, operating systems that run *within* the partition, can act as if they would run on a smaller overall system, even though the hardware may have significantly more processors. The OS can reduce overhead for precautions for processors that are not supported and use the best synchronization scheme for the partition's specific resource configuration.

#### 3.3.1 Hardware Partitioning

Hardware partitioning is a well-known technique from mainframe class computers and was recently introduced on enterprise-class UNIX systems. Hardware resources, including processors, memory and I/O devices, are allocated to individual partitions. The partitions are strictly isolated from each other via specialized hardware support.

Brown Associates [32] compares the Sun E10000 and Unisys ES7000 systems that both support hardware partitioning. The Sun E10000 [102] supports up to sixteen domains that achieve complete isolation while sharing the interconnect. Registers on the system boards define the domain per board. All components controlled by the system board become part of the domain. Failures within a domain do not affect other domains, except for failure of system-wide components.

The Unisys ES7000 [112] supports up to eight partitions and the quantity of processors, memory, and I/O devices in a partition can be freely configured. Resources between partitions can be adjusted dynamically. The ES7000 memory sys-

3.3. PARTITIONING

tem supports private memory and memory to be shared among partitions. Similar hardware partitioning is supported by IBM Sequent, and HP (nPar).

The limiting factors of hardware partitioning are the *relatively static resource allocation* and the *strict partition boundaries*. Resources that are allocated to one partition cannot be easily shared by another. In particular it is not possible to share processor resources between partitions, in case a processor falls idle while another system is overloaded.

An important feature of partitioning is fault containment. The two possible failure types are hardware failures and software failures. While microkernel-based systems naturally achieve containment of software failures of applications via address space protection, hardware fault containment requires specific support in the microkernel (hardware fault containment is not addressed in this work).

#### 3.3.2 Software Partitioning and Virtual Machines

Similar to the hardware based partitioning approach, software partitioning multiplexes the hardware resources between different operating system instances. Each OS instance has a subset of the overall system resources.

Software partitioning is often used in the context of virtual machines (VM) [43], where multiple concurrent operating systems compete for the system resources. The virtual machines are under control of a privileged virtual machine monitor (VMM) that serves as the controlling entity and resource manager. VMs and microkernel-based systems are very similar in respect of the isolation goals. They differ insofar that microkernel-based systems provide a set of abstractions that enable fine-granular resource isolation and recursive resource control for all system services, whereas most VMMs solely target for monolithic coarse-grain hardware multiplexing [15]. As our group has shown, a microkernel can serve as the core platform for virtualization [69, 111], while the opposite is often not the case because of the lack of high-performance communication primitives.

Besides our work on scalable virtual machines [111], the other most prominent research addressing VMs for multiprocessor systems is Cellular Disco [47].<sup>2</sup> Cellular Disco aims to provide the advantages of hardware partitioning and scalable operating systems while avoiding the scalability bottlenecks. Cellular Disco uses a small, privileged VMM that multiplexes resources of different virtual machines. The system is divided into cells that act independently and interact via an in-kernel RPC mechanism. A primary goal of the messaging system is to preserve independence for fault containment and to ensure survival of cells in case of remote failures.

While Cellular Disco shares some goals with my thesis, it differs in the way these goals are achieved. Cellular Disco specifically targets VMs and provides the core services, such as scheduling, page allocation, and device drivers *within* the privileged VMM. Thus, the VMM follows a traditional monolithic operating

<sup>&</sup>lt;sup>2</sup>That does not include commercial systems, such as IBM's OS 390.

system design paradigm, with in-kernel policies.

A key design decision of Cellular Disco is to assume that the code is correct. The assumption is warranted by the fact that the size of the virtual machine monitor is small. The authors report a prototype kernel of 50K lines of code (compared to 13K for L4Ka::Pistachio), however, it is *co-located* with an SGI IRIX 6.4 OS for device accesses. Despite the inherent dependence on IRIX for correctness, such co-location also has implications on scalability. The scalability of an important aspect of the system — hardware device accesses — becomes dependent on the overall scalability of IRIX. Also, the work does not specifically address scalability of multiprocessor systems but has a stronger focus on general problems of VMs, such as eliminating double paging and memory balancing policies.

### 3.4 Microkernel-based Systems

#### 3.4.1 The Microkernel Argument

A common method for structuring operating systems is a *monolithic system*, which integrates all OS functionality in a single system image (e.g. UNIX [93] and VMS [44]). The main advantage of such a monolithic structure is good performance and global visibility of system state. Monolithic systems, however, have a number of disadvantages. Since all system services reside within the monolithic system image, all subsystems share a single protection space and may interfere. Faults within one subsystem can propagate to others with potentially fatal consequences for the system.

In order to extend such systems with new functionality such as different scheduling policies, file systems or device drivers, the extension has to be *integrated* with the monolithic kernel. The extension is code that is injected in the kernel and runs with full privileges. Thus, the injected code becomes globally trusted, however may neither be trustworthy nor error free. A variety of approaches address trustworthiness, such as simple code signing [33,83], sandboxing [119], interpreted languages [84], type-safe languages [18], domain-specific languages [40], and proof-carrying code [85,86].

In contrast to monolithic designs, in microkernel-based systems the operating system functionality is implemented as *user-level servers*. These servers run in separate address spaces and communicate using inter-process communication (IPC) built into the microkernel. Extensibility is achieved by replacing the system servers, similar to normal applications.

Microkernels isolate operating system components via address spaces from each other and also provide them with separate resources. Both properties enable multiple OS services with different resource policies to co-exist on one system. These include systems with different security requirements [90] or systems with real-time and non-real-time demands [53,97].

The second important property is the size and complexity of microkernels. Microkernels are tiny and thus can be used as a secure platform for custom, applica-

tion specific operating systems [62,75].

#### **First-Generation Microkernels**

First-generation microkernels failed to fulfill the promise for better structured and more flexible systems. The most prominent kernel is Mach [2] and it provides a good example of the problems of first-generation microkernels. Mach was designed to exploit modern hardware features such as multiprocessors, and enable new application domains. At the same time, Mach was supposed to provide backward compatibility to existing operating systems such as UNIX [93]. As a result, Mach was constructed by refactoring a UNIX kernel and introducing new kernel interfaces. The UNIX functionality was moved to application servers.

Mach lead to a number of important innovations, such as user-level pagers [123], with the result of a tremendous growth of the API surface area and an increase of kernel complexity and size. The primary problem of Mach, however, was its opulent and extremely slow IPC mechanism that resulted in severe performance problems for systems constructed on Mach.

#### **Second Generation Microkernels**

Second generation microkernels addressed the above problems with radical new designs. Liedtke [71] identified poor structuring and high cache footprint of Mach's IPC primitive as the main performance problems. By careful design of the communication mechanism, second generation microkernels such as L4 [71], Exokernel<sup>3</sup> [34, 62], and EROS [98] exhibited the envisaged properties with superior performance to other extension methods.

The fundamental design principles for most second generation microkernels are:

- The kernel provides a minimal set of abstractions: threads and address spaces.<sup>4</sup>

- The kernel provides a *minimal set of mechanisms* in order to multiplex hardware in a safe and secure manner. The key primitive is inter-process communication which enables extensibility of the system via interacting user-level servers [73].

- The kernel should be *policy free*. The policies should be provided by the system servers using the kernel mechanisms.

<sup>&</sup>lt;sup>3</sup>Exokernels differ from microkernels insofar that exokernels avoid high-level abstractions but directly multiplex the hardware. I still discuss them with microkernels because many goals are very similar.

<sup>&</sup>lt;sup>4</sup>More general, each microkernel needs at least one abstraction for execution (or an activity) and one abstraction for a protection domain to permanently bind resources.

Based on these design principles a number of microkernels were developed that yielded excellent performance for both system software and user applications. Härtig et al. [54] showed that L4 not only has excellent IPC performance but also incurs a minimal overhead when running a monolithic operating system (Linux) on top of the microkernel. The reported overhead for macrobenchmarks was between 5 to 10 percent compared to monolithic Linux. Still, microbenchmarks showed overheads of a factor of three for short-running system calls. I and colleagues [110] further reduced the microkernel-induced communication overhead from a factor of three to about thirty percent.

#### 3.4.2 Multiprocessor Microkernels

One aspect of previous research in the area of microkernels is multiprocessor systems. The reduced complexity of microkernels as compared to monolithic systems makes them a feasible system architecture.

The Hydra kernel [122] was designed with the goal of separating mechanisms and policy and thereby provides an exploration testbed for multiprocessor systems.

Mach targets large-scale multiprocessor systems and provides lightweight threading in order to utilize the parallelism offered by the hardware [20]. Being a first-generation microkernel, Mach employs a traditional scalability approach comparable to many monolithic multiprocessor OS's. The in-kernel subsystems were optimized on a case-by-case basis [64] by first identifying and then removing scalability bottlenecks. However, Mach still exhibited its poor IPC performance.

The Raven microkernel [94] specifically targets multiprocessor systems with a focus on minimizing the overhead for kernel invocations. Raven provides user-level scheduling with a kernel-based callback (similar to scheduler activations [5]), user-level interrupt handling, user-level interprocess communication, and user-level synchronization primitives. While moving significant system parts to application level, Raven uses a number of global data structures, thus limiting its scalability. For example, the memory pool is protected by a global lock and accesses to task objects are serialized.

Chen [27] extended the uniprocessor Exokernel system to multiprocessor systems. The fundamental idea of Exokernel is to expose the hardware properties directly to application level thus avoiding the overhead introduced by high-level OS abstractions. The OS itself is implemented as a library at application level. The multiprocessor Exokernel uses a variety of alternative synchronization strategies. Similar to my approach described in this thesis, Exokernel localizes kernel resources and uses in-kernel messaging to manipulate remote resources. However, the choice for synchronization primitives is ad-hoc and static. The specific kernel implementation dictates the synchronization granularity and may result in high overheads. This is, for example, reflected in the memory subsystem, where the reported cost for memory mappings is three times higher than on the uniprocessor version of the kernel. Furthermore, the overhead for the kernel's IPC primitive (even for uniprocessor systems) is almost an order of magnitude more expensive

than L4.

The most prominent work in the area of scalable microkernel systems is Tornado [41] and its successor K42 [8]. K42 is a microkernel-based system that employs many of the previously described techniques for scalability, including read-copy update, clustered objects, and lock-free synchronization. K42 scales well to a large number of processors, provides a Linux-compatible API, and reuses Linux components in the kernel [9]. K42 differs from my approach insofar, as K42 blurs the line between kernel and application level and allows the kernel to be extended in order to overcome performance bottlenecks. For example, K42 allows for colocation of device drivers if performance requires. K42's underlying microkernel provides access to kernel-internal data structures via a wide kernel-user interface (e.g., for scheduling information). K42 also achieves adaptability of synchronization mechanisms, however, via runtime code replacement and with the limitations of the fault-based scheme described in Section 3.1.2.

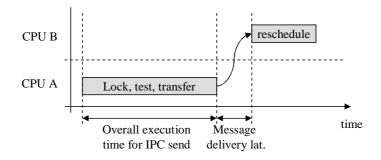

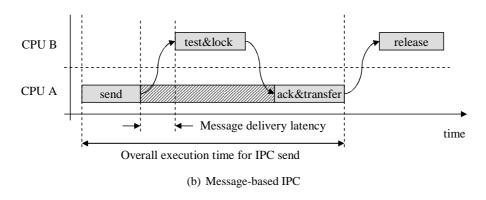

#### L4

Besides the work presented in this thesis, there are at least two other L4 microkernel variants that support multiprocessor systems. Liedtke [70] briefly discusses the implications of multiprocessor support and argues that locking will have a significant performance impact on all critical system operations including IPC. Potts et al. [91] realized a multiprocessor version of L4 on the Alpha architecture with the primary focus on the performance of the local-case IPC. All inter-processor operations use message-based synchronization schemes. The kernel, however, does not support kernel memory pool management and also lacks a TLB coherency scheme.

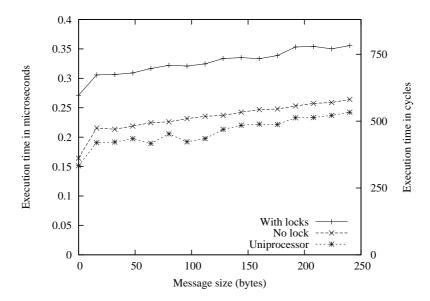

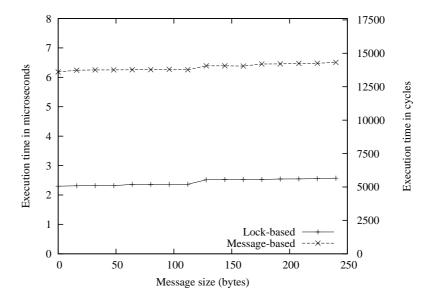

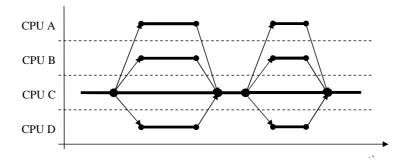

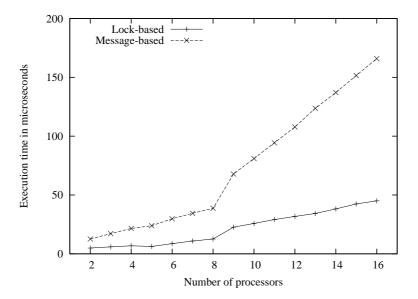

Hohmuth [58] describes Fiasco, an L4 kernel that focuses on real-time properties via non-blocking synchronization. Fiasco uses a locking-with-helping scheme in order to minimize thread blocking time in real-time systems. If thread *A* tries to acquire a lock that is held by a preempted thread *B*, *A* donates its time to *B*. After the lock is released, *B* immediately switches back to *A*. Fiasco's helping scheme is also used across processor boundaries. The approach, however, is questionable for larger multiprocessor systems for the following reasons: