Universität Karlsruhe (TH) Institut für Betriebs- und Dialogsysteme Lehrstuhl Systemarchitektur

# Hardware-Supported Virtualization for the L4 Microkernel

Sebastian Biemüller

**Diploma** Thesis

Verantwortlicher Betreuer: Prof. Dr. Frank Belosa Betreuender Mitarbeiter: Dipl. Inf. Jan Stöß

29. September 2006

Hiermit erkläre ich, die vorliegende Arbeit selbständig verfaßt und keine anderen als die angegebenen Literaturhilfsmittel verwendet zu haben.

I hereby declare that this thesis is a work of my own, and that only cited sources have been used.

Karlsruhe, den 29. September 2006

Sebastian Biemüller

# Abstract

Despite the immense popularity virtual machines regained in the last years current virtualization environments force significant compromises to the host system architecture. Hypervisor-based virtual machine environments are missing system construction principles; they only provide the coarse grained abstraction of a virtual machine, preventing small and efficient systems. Hosted virtual machine environments reuse the host's operating system services and thereby massively increase the trusted code base, preventing small, reliable and verifiable systems.

We propose a novel approach for the construction of virtual machine environments: We divide the virtual machine environment into a necessarily privileged part, and a user-level monitor. The privileged part and microkernels share a common set of goals such as reliability, security, and isolation so that integrating virtual machines and microkernels is a promising approach. In fact, modern microkernels, such as the L4 microkernel, already provide the abstractions and mechanisms necessary to cater for virtual machines. We identify shortcomings of the current kernel with respect to virtual machine support and add a minimalistic set of extensions. As a normal microkernel application, the user-level monitor can interact with services provided by other components to maintain the virtual machine.

To demonstrate our approach we implemented a prototype virtualization environment on top of the modified microkernel. We successfully run a guest operating system, utilizing all types of services side-by-side with other, native microkernel applications.

Our design preserves the performance of the microkernel, especially the mechanism for inter-process communication needed no adaption. Measurements indicate only minimal side-effects caused by the increased hardware-overhead of the worldswitch needed for the virtual machine environments.

# Contents

| Ał | Abstract |                                            |    |  |  |

|----|----------|--------------------------------------------|----|--|--|

| 1  |          | oduction                                   | 1  |  |  |

|    | 1.1      | The Problem                                | 1  |  |  |

|    | 1.2      | Approach                                   | 2  |  |  |

| 2  | Bacl     | kground & Related Work                     | 5  |  |  |

|    | 2.1      | Virtual Machine Environments               | 5  |  |  |

|    |          | 2.1.1 Theory of Virtualization             | 6  |  |  |

|    |          | 2.1.2 The Virtual Machine Monitor          | 7  |  |  |

|    |          | 2.1.3 Selected Virtualization Environments | 8  |  |  |

|    | 2.2      | The L4 Microkernel                         | 9  |  |  |

|    |          | 2.2.1 The Microkernel Argument             | 9  |  |  |

|    |          | 2.2.2 Abstractions                         | 9  |  |  |

|    |          | 2.2.3 Primitives                           | 9  |  |  |

|    | 2.3      | Microkernels and Virtual Machines          | 10 |  |  |

|    | 2.4      | Summary                                    | 11 |  |  |

| 3  | Desi     | an                                         | 13 |  |  |

| U  | 3.1      | Design Goals                               | 13 |  |  |

|    | 3.2      | Proposed Scheme                            | 14 |  |  |

|    | 5.2      | 3.2.1 System Architecture                  | 14 |  |  |

|    |          | 3.2.2 Virtual Machine Representation       | 15 |  |  |

|    | 3.3      | Virtual Machine Resources                  | 17 |  |  |

|    | 5.5      | 3.3.1 Physical Memory                      | 17 |  |  |

|    |          | 3.3.2 Virtual Memory                       | 19 |  |  |

|    |          | 3.3.3 Processor                            | 22 |  |  |

|    |          | 3.3.4 Peripheral Devices                   | 24 |  |  |

|    | 3.4      | User-level Control Protocol                | 25 |  |  |

|    | 5.1      | 3.4.1 Analysis of Requirements             | 25 |  |  |

|    |          | 3.4.2 The Virtualization-Fault Protocol    | 27 |  |  |

|    | 3.5      | Virtual Machine Communication              | 29 |  |  |

|    | 3.6      | Summary                                    | 30 |  |  |

|    | 5.0      | Summary                                    | 50 |  |  |

| 4  | Imp      | lementation                                | 33 |  |  |

|    | 4.1      | The IA-32 Processor Architecture           | 33 |  |  |

|    | 4.2      | Microkernel Extensions                     | 35 |  |  |

|    |          | 4.2.1 VCPU Thread                          | 35 |  |  |

|   |      | 4.2.2 VM-Exit Handler                | 38 |

|---|------|--------------------------------------|----|

|   |      | 4.2.3 Virtualization Fault Protocol  | 38 |

|   |      | 4.2.4 Physical Memory Space          | 39 |

|   |      | 4.2.5 Shadow Page Table Management   | 10 |

|   |      | 4.2.6 Further Resources              | 15 |

|   | 4.3  | The User-Level Monitor               | 16 |

|   |      | 4.3.1 Architecture                   | 16 |

|   |      | 4.3.2 Virtual Machine Representation | 18 |

| 5 | Eval | luation                              | 51 |

| 6 | Con  | clusion                              | 53 |

|   | 6.1  | Contribution of This Work            | 53 |

|   | 6.2  | Suggestions for Future Work          | 54 |

| Α | Prop | bosed L4 API Extensions              | 55 |

|   | A.1  | SPACECONTROL                         | 56 |

|   | A.2  | EXCHANGEREGISTERS                    | 57 |

|   | A.3  | Virtualization Fault Protocol        | 58 |

|   |      | A.3.1 Fault Message                  | 58 |

|   |      | A.3.2 Reply Message                  | 58 |

|   |      | A.3.3 Thread-Startup Protocol        | 51 |

|   | A.4  | MSR-Fpage                            | 52 |

# Chapter 1

# Introduction

For the last 40 years the complexity of computer hardware increased exponentially driven by Moore's famous law [70] constantly opening fields where computer systems become attractive. Unfortunately, software systems do not keep up with this rapid evolvement resulting in increased pressure on software systems [29] to adapt to these new hardware features and efficiently utilize them. This holds especially for operating systems; they execute directly on the bare hardware to manage and abstract hardware specifics behind a convenient, portable interface which user applications rely on. This thesis combines two approaches which address the stated problem from two different directions.

*Virtual Machines* first introduced by IBM in the 1960s were invented to provide multiple users a seemingly separate, computing system to overcome the limits of former single-user operating systems. In the last 40 years, virtual machines have matured in providing a faithful illusion of a complete machine platform; they now allow legacy reuse of a complete software stack; presenting an attractive approach to solve a variety of problems in dissimilar contexts such as exploiting new hardware features [15], device driver reuse [57], workload consolidation [25] and migration [20], secure computing [69].

*Component-based operating systems* increase flexibility of system software construction by separating the operating system into isolated components. The base of the system is a microkernel. It only implements the minimal necessary concepts such as computation, isolation, and communication to establish independence and integrity between different subsystems. The goal is to allow construction arbitrary systems on top. Microkernel-based systems allow stepwise innovation in OS technology to cope with the ever-increasing complexity of operating systems.

# **1.1 The Problem**

Systems which are based on only one of the both approaches, either the microkernel system, or the virtual machine system are overly restrictive and do not achieve the required flexibility.

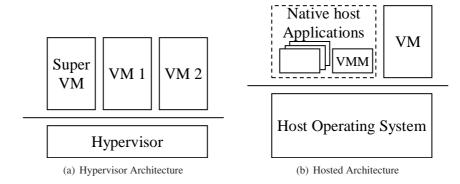

Systems solely based on the virtual machine abstraction, such as the hypervisorbased approach (Figure 1.1(a)) affect the whole system. A small, privileged hypervisor provides a reliable system base. It implements only a single interface, the virtual machine. The virtual machines are isolated from each other and securely executed using

Figure 1.1: Virtualization Architectures. Missing: The different interfaces provided by the different approaches.

the host machine's resources. The virtual machine as a faithful duplicate of a real machine is often too coarse grained to represent small software components efficiently. This even holds for the virtual machine management logic, which is run in a privileged component, the *super VM*. The super VM often runs a commodity operating system to implement services such as the emulation of the virtual machine environment of the other VMs. Faults in its implementation [19] can thereby affect other virtual machine environment.

To overcome the construction problems of the virtual machine management logic the *host-based* approach (Figure 1.1(b)) integrates the privileged hypervisor into a host operating system, which directly executes on the physical machine. The host operating system services can be used to implement the virtual machine monitor as an in-kernel module or a user-level application; this avoids the second costly world switch into the super-VM. However, this model has serious drawbacks, too. The host operating system greatly increases the privileged part, and thus the trusted computing base of the system [26, 78]. The reliability and secure isolation of virtual machines is only as hard as the general security of the host operating system. Additionally, running the virtual machine monitor on top of the host operating system increases overhead drastically [26].

The virtual machines strongest point becomes also its weakest: focusing on reuse and isolation they do not offer a core abstraction for communication with the system surrounding the virtual machine. The communication is often emulated via special devices which are part of the platform provided to the guest. It significantly increases the necessary trusted computing base.

On the other hand we presented microkernels. Microkernels are designed to form a flexible system base. Like all other operating systems they define a convenient interface to their user-level applications. This interface is close, but not equal to the hardware platform, preventing full software reuse – requiring porting.

# 1.2 Approach

In this thesis, we unify the virtual machine- and the microkernel environment in one system. We present a new scheme to construct virtual machine systems: Based on the

# 1.2. APPROACH

concepts of microkernels we construct whole-system virtual machine systems [81] to overcome the deficits of a solely hosted or hypervisor-based approach.

Our approach separates the virtual machine monitor into a necessarily privileged part, called the hypervisor, and an unprivileged part, the user-level monitor. Our approach is based on the thesis that: *hypervisors and microkernels are similar enough to justify integration of both.* The resulting system comprises a microkernel that also provides support for virtual machines and a microkernel-based system on top which includes components for maintaining the virtual machines. Such a system combines the best of both worlds: Virtual machines provide strongly isolated containers with a stable, compatible interface, the hardware platform API for legacy reuse, whereas the microkernel approach enables construction of arbitrary, well-structured systems.

Our design is based on a particular microkernel, the L4 microkernel. The resulting microkernel has only marginally increased complexity caused by the mechanism to support user-level management of the virtual machine, the protocol to communicate virtualization critical events, and the enhanced execution context handling required by the world switches from/to virtual machines. The virtual machine representation in L4 is highly integrated, introducing only minimal changes to the microkernel API. Like all other application workload the virtual machine is described by an L4 address space, which represents the isolation domain, holding all accessible physical resources. L4 threads embody the processor of the virtual machine directly executing the virtual machine's instruction on the physical processor. The communication of virtualization critical events is completely via synchronous IPC; it models the fault like behavior.

The user-level monitor application uses the IPC based virtualization-fault protocol to control the virtual machine. Being a native L4 application, the monitor can use L4's usual mechanisms to control the virtual machine environment. Guest physical memory is provided by L4's mapping mechanism; execution of the virtual machine underlies the usual thread scheduling provided by L4.

We demonstrate the feasibility of our approach by integrating support for full virtualization of the x86 architecture using Intel's virtualization technology. The required changes to the L4 microkernel did not negatively affect the performance of native L4 applications; thus independence is sustained. Especially the inter-process communication mechanism need no modifications. Only minimal overhead is introduced by the unavoidable hardware world switch for entering and exiting the virtual machine.

# Outline

This thesis is structured as follows:

### Chapter 2:

In the background chapter we give an overview of virtualization and microkernel-based systems. We analyse the requirements of virtualization, describing different virtualization systems and discuss their approaches and resulting system architectures. Further, we introduce the idea of microkernel-based systems describing its goals and concepts and the resulting system architecture. We focus on a particular microkernel, the L4 Microkernel.

### Chapter 3:

In the design chapter we present our approach of integrating virtualization features into the L4 microkernel. We present our L4-based virtualization system architecture focusing on the kernel representation of a virtual machine using microkernel concepts.

# Chapter 4:

In the implementation chapter we offer an overview of our prototype implementation of the microkernel extensions and a user-level virtual machine monitor application.

# Chapter 5:

In this chapter we present the evaluation of our prototype implementation.

# Chapter 6:

Finally includes a summary and gives suggestions for future work.

# **Chapter 2**

# **Background & Related Work**

This thesis brings together two research areas: virtual machines and microkernel-based systems. In Section 2.1 we discuss the general problem of virtualization by reviewing previous work: on the theory of virtualization, the requirements of virtualization, and different virtualization approaches including their resulting architectures. Section 2.2 describes the state of the art in microkernel-based systems laying the ground for many design decisions. We briefly introduce the L4 microkernel paying special importance to virtualization critical mechanisms, such as the representation of hardware mechanisms.

# 2.1 Virtual Machine Environments

Virtual machine (VM) systems are a major development in computer system designs. By providing a duplicate of one or more computer systems, virtual machines extended computer systems from multi-access, multi-programming, multi-processing to multi-environment architectures. Concurrency, previously only available at a higher level becomes available at the lowest level — the system-level. Virtual machines adopt the common theme of adding an layer of indirection to increase the flexibility.

The term *Virtual Machine* was introduced by IBM in the 1960s; IBM used virtual machines to provide multi-user systems by securely multiplexing several instances of a single-user operating system; each OS running in a virtualized duplicate of the real machine [21]. In the last 40 years the virtual machine technique has matured in providing the illusion of an isolated and exclusive hardware platform to its guest's software stack. Virtual machines represent an attractive approach to solve a variety of problems in quite different contexts:

- Exploiting new hardware features without requiring changes to the software stack [15, 16]

- Improved testing of system software [54]

- Providing a high degree of reliability and security [13, 17, 30, 31, 44, 45, 69, 79]

- Running multiple, different software stacks concurrently on one physical machine e.g. to achieve consolidation or operating system diversity [25,96]

- Running virtual configurations which are different from the physical system to offer services like migration and ubiquitous computing [17, 20]

# 2.1.1 Theory of Virtualization

A Virtual Machine as defined by Goldberg [33] is an "efficient hardware-software duplicate of a real machine". The idea of virtual machines is to create the illusion of a physical machine at the lowest level, the platform API. Thus, communication between the guest (operating) system executing inside the VM and the virtual machine environment is completely defined by the behavior of the hardware interface.

The virtual machine monitor (VMM) provides the illusion of the VM's environment using the resources of the host system. It has full control of the virtual machine and can establish full isolation or controlled sharing of resources between the VM, itself, and the rest of the system. The environment of the VM includes all resources of a physical machine: the processor, memory, interrupt lines, IO ports and thus devices. The virtual machine monitor has three characteristics [74]:

- Equivalence. The guest running in the virtual machine expects to execute on a physical machine. In order to execute properly the environment provided by the VMM, the virtual machine, needs to represent all aspects of a physical machine. Only the exact timing behavior is impossible to achieve multiple virtual machines execute concurrently, and the VMM itself needs some time to create and maintain the virtual machine's environment.

- **Resource Control.** The VMM must be in control of the physical system. (i) No virtual machine is allowed to directly access a physical resource not explicitly allocated to it. (ii) The virtual machine monitor needs to be able to transparently regain control of a previously allocated resource.

- Efficiency. The virtual machine provides the same hardware platform as the host machine. Efficiency can be achieved by securely using physical resources of the host whenever possible. This is especially important for the virtual machine processor. A "statistically dominant subset of the virtual processor's instructions needs to be executed directly on the real processor" [74].

#### Virtualization of System Resources

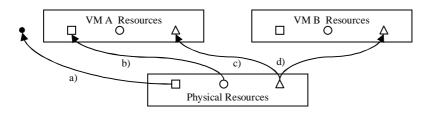

To create the illusion of an exclusively available physical machine all machine components need to be virtualized. The virtualized components must follow the stated characteristics of equivalence, controllability, and efficiency. Depending on their type resources can be virtualized in several ways [34]; Figure 2.1 depicts an overview:

A virtualized resource is represented by a *renamed* physical resource. Renaming enables different objects of the same resource class to represent each other. For example, renaming of physical memory can be provided by virtual memory. Different physical memory frames can be used to represent the same page frames in different virtual machines.

If a physical resource is completely preemptible one instance of a physical resource can be *multiplexed* between different virtual machines; for example, multiplexing of a processor register between different threads. A special case of multiplexing is when the resource is exclusively assigned to one user, here the state need not necessarily preemptible.

If a resource can not be renamed or securely multiplexed the resource needs to be *emulated*. Emulation of resources is usually done by trapping instructions which access these resources. The effect on the virtual machine environment is then emulated in software.

Figure 2.1: Resources of a virtual machine can be provided in several ways. Depending on the characteristics of a given resource it can be: (a) emulated, (b) remapped, (c) mapped, and (d) multiplexed.

### **The Virtual Processor**

The physical processor is the key to the virtualizability of the system. It must provide trap semantics that let a VMM safely, transparently, and directly use the real processor to execute the virtual machine. With these traps on virtualization critical conditions the VMM can use direct execution to create the illusion of a normal physical machine for the software running inside the virtual machine. These traps include external events, related to the physical machine such as interrupts, which must be sheltered from the virtual machine and be delivered to the VMM, and internal events such as the execution of *sensitive* instructions. When the virtual machine executes directly on the physical processor, some instructions – instructions which leak the state of the physical machine uncontrolled into the virtual machine – can not be issued; these instructions are called *sensitive*. Sensitive instructions must be prevented from being executed directly. If all critical instructions are trap-able, the processor is called *fully-virtualizable*.

# 2.1.2 The Virtual Machine Monitor

The virtual machine monitor functionality can be divided into several modules [74]. The *dispatcher* is the first module. It starts the VMM and initializes its environment. The dispatcher represents the entry-points for the different traps of the physical processor. The dispatcher therefore implements secure multiplexing of the virtual machines. The *allocator* manages the physical resources. It keeps track of the resource usage to guarantee controlled isolation. The *interpreters* are a set of routines which emulate the behavior of the trapped, sensitive instructions.

#### Architecture

In the *hosted* architecture the virtual machine monitor runs on top of a host operating system. It can use the host operating system's services to implement the virtual machines. The monitor can reuse the host operating system's abstraction and services such as scheduling and resource allocation to implement the virtual machines. On the other hand the monitor may loose full control of the host's hardware to the host operating system; flaws in the host operating system undermine the security of the complete virtual machine system [78]. To minimize the side effects of software not directly related to the virtual machines, the *hypervisor* based architecture minimizes the privileged code running directly on the physical machine. The privileged hypervisor implements only basic scheduling and isolation mechanisms of the dispatcher module. The other components are located in a *super*-VM located on top of the hypervisor. This privileged

virtual machine often contains a classic monolithic OS which includes the device driver emulation and VM management interface.

# 2.1.3 Selected Virtualization Environments

Tons of virtual machine systems have been developed each for its own special purpose. We classify these approaches into para- and full-virtualization systems and discuss the various approaches regarding their special goals.

#### **Para-Virtualization: Environments**

Para-virtualization systems [95] require source code access to the guest system to change it. Para-virtualization does not have the goal to provide an exact duplicate of the platform API. It follows the opposite approach: each guest is ported towards the virtualization system by replacing virtualization critical sensitive operations with high-level hypercalls to the VMM. These changes are often guest specific; para-virtualization requires intimate knowledge of the guest system resulting in high engineering effort [56]. Depending on the required characteristics research found various approaches. Having knowledge of the guest operating system's behavior hypercalls can even be delayed and batched until an unavoidable call to the VMM is necessary. This is used, for example, in the Xen hypervisor [25]. This reduces the number of domain switches and thus increases performance. Stepwise introduction of special hypercalls, the approach presented in [67], removes performance bottlenecks. A host based para-virtualization environment is User Mode Linux, it runs a modified Linux on top of the Linux operating system [24].

VMI [91] provides a generic para-virtualization interface which still requires porting of the guest. It focuses on the unification of the interface between the VMM and the guest for x86 based systems. The OS implementors simply change their operating system to call specific VMI routines stored in a ROM to make their system virtualization friendly. The routine transparently handles virtualization. It allows to switch between different VMMs implementing the VMI interface and native operation.

### **Full-Virtualization: Environments**

Full virtualization environments do not require source code access to the guest; they focus on providing a faithful illusion of the platform API. Modification of the guest's behavior is only possible by using special device drivers for a specific guests, e.g. to provide custom high performance devices such as network cards [52], or to reclaim memory using memory balloons [94]. Prominent full-virtualization environments are the host-based VMware Workstation and the hypervisor-based VMware ESX server [92]. Virtual machines core functionality is to provide an isolated environment.

#### **Emulation**, Simulation

On processors not fully-virtualizable sensitive instructions must be prevented to appear in the VM's instruction stream. The most relevant technique is *para-virtualiza-tion* [25, 56, 96]; it needs source-code availability of the guest software to patch the sensitive instructions with fix-ups. *Binary rewriting techniques* [7, 23, 80] instead use complex trapping of memory references to transparently change the guest's instructions. *Whole-system simulation* such as Simics [90], QEMU [12], and Bochs [55]

interpret the complete virtual instruction set, such approaches, although very powerful impose huge performance hit and thus violate Golberg's efficiency requirement [35]. In this thesis we focus on fully-virtualizable processors.

# 2.2 The L4 Microkernel

The L4 microkernel [63] is a second generation microkernel originally developed by Jochen Liedtke at GMD, IBM, and Karlsruhe University. Various versions exist at Karlsruhe University, UNSW/NICTA Sydney, and Dresden University of Technology [83].

# 2.2.1 The Microkernel Argument

In contrast to monolithic systems, the microkernel-based approach implements operating system functionality like scheduling policies, network services or device drivers into dedicated *user-level* servers. To isolate them these servers are located in different address spaces and provide their services by inter-process communication. This construction principle is very flexible; the system services can be replaced, or run sideby-side like normal applications, allowing coexistence of different resource policies on one system [62] specialized for different applications [53,65]. The system base forms a microkernel. It implements system-wide features like isolation, resource management, communication, and integrity. The goal of a microkernel is to be policy free and to provide system construction principles. The microkernel is tiny and thus can be made secure [42, 86]. Beginning with Mach's user-level pagers [77, 97]; current second generation kernels provide even more complete resource management in userlevel components [40, 62]. The most critical kernel mechanism is IPC; it is master to the functionality and flexibility of the microkernel [59, 64] and the component system on top [14, 32].

# 2.2.2 Abstractions

**Threads** are the abstraction of an activity. CPU time is multiplexed between threads bound to the same processor. An L4 thread is represented by its register state (processor registers and virtual registers), a unique global identifier, and an associated address space.

**Address spaces** provide the abstraction for protection and isolation; resource permissions are bound to an address space. L4 address spaces are no first class object; they are indirectly identified via a thread associated to this particular space. All threads in an address space have the same rights and can freely manipulate each other.

# 2.2.3 Primitives

**Inter process communication (IPC)** is the mechanism for data transfer and controlled execution transfer between threads. Message transfers are synchronous and involve exactly two threads. Both sender and receiver have to agree on the format of the message. IPC is the master to the microkernel design [59]. **Resource Delegation** is the mechanism for controlled transfer of resource permissions between address spaces. Access to a resource is granted by transferring a *map* or *grant* item in an IPC message, and thus allows user-level management of address spaces. Mapping requires mutual agreement of the sender and receiver thread. Map duplicates the resource permissions from the sender's into the receiver's address space; grant moves the permission. The receiver's permissions can only be a subset of the sender's permissions. Mapping can be applied recursively. Revocation of resource rights is done asynchronously through the *unmap* primitive and does not require explicit consent from the receiver of the mapping.

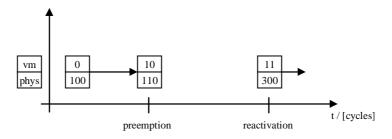

**Scheduling.** L4 has an in-kernel round-robin *scheduler* that allocates time to threads according to their priority and time-slice length. If the time slice of a thread expires, L4 preempts the thread and schedules the next runnable thread.

**Protocols.** Hardware-generated events such as *exceptions* and *interrupts* are translated into kernel-generated IPC messages. On an hardware interrupt, the kernel synthesizes a message to a thread that is registered as the handler for that interrupt. The sender appears to be a thread with a special per-interrupt thread identifier. Hardware exceptions are transparent to the faulting thread; the kernel preserves the thread's context. The hardware exceptions are mapped onto an IPC based fault protocol. In the name of the faulting thread, the kernel synthesizes a message with information about the cause of the fault and sends it to the faulting thread's exception handler. The faulting thread is automatically set into a blocking IPC receive operation, waiting for a reply from the exception handler to resume execution. On a page fault exception, the fault message is sent to the page of the thread, expecting a memory mapping in the reply. The special treatment of the page fault exception has historical reasons.

These protocols allow easy virtualization of physical resources, e.g., paged virtual memory [9, 40]: Under memory pressure, the provider of a page unmaps it from the address space it was mapped to. If a thread now accesses the removed page, a page-fault IPC is sent so that the pager can transparently re-establish the mapping and resume the faulting thread.

# 2.3 Microkernels and Virtual Machines

There already exists related work which integrates the fields of virtual machines and microkernels. In [39] and [43] the authors argue that microkernels and virtual machines, although their definition is quite different, follow similar goals. The work presented in [68] reasons towards a microkernel-based virtual machine systems for high performance computing.

**Extended Virtual Machine Monitor.** The work of Hohmuth et . al [46] explores the design space of hybrid virtual machine/microkernel systems with the goal to minimize the trusted computing base (TCB) required to implement the virtual machine environment. It is found that a VMM extended by mechanisms for memory sharing and communication can reach a very small TCB.

**Para-virtualization.** The L4 microkernel already serves as a host for virtual machines. The L4Linux [41] system, is a para-virtualized Linux kernel, ported to the L4's

# 2.4. SUMMARY

API interface. It achieves near native performance.

The L4Ka::Virtualization environment [85] also support the L4 microkernel, as a host. The authors separated the VMM into an isolation critical resource monitor and an uncritical in-place component. The in-place component is co-located to the guest, it can use detailed knowledge of the guest to create the illusion of the virtual machine environment. It uses a technique called after-burning to replace sensitive instructions of the guest with function calls to the in-place component's interpreters which avoids hypercalls. Allocation of physical resources that can not completely handled inside the in-place monitor are translated to resource monitor requests. This indirection allows for (i) guest specific optimizations in the in-place monitor and (ii) host system diversity. The environment supports the L4 microkernel [84] and the Xen hypervisor [25] as a host.

The Spine system [37] forms a reliable system base for an intrusion recovery system. It supports detection and recovery from kernel-level and user-level root-kits. The authors choose a microkernel, the L4 microkernel as the base hypervisor component. The authors argue that only a microkernel achieves the correctness, isolation and performance requirements. The microkernel was preferred over a virtual machine approach because the authors wanted a simple architecture that does not sacrifice performance and support for multiple operating systems. As guest operating systems, to prove recovery services, it uses para-virtualized L4Linux instances.

**Fluke.** The Fluke system developed by Bryan Ford et al. [28] is a software-based virtualizable architecture. It combines the concepts of microkernels and virtual machines to increase operating system extensibility. The operating system functionality is decomposed "vertically" into layers. In these layers, called *nesters*, the environment, provided to the application can be stepwise refined; for example a *demand paging nester* adds anonymous memory, or a *checkpoint nester* allows defined restart of the application after a system failure. The application environment consists of the hierarchy of nesters it runs on. Thus the application environment only includes the required operating system services.

The prototype system implementation is based on the x86 architecture – on which the fluke microkernel runs. Fluke provides a well defined subset of the x86 architecture to the nesters and applications on top to avoid the trapping of traditional virtual machine systems. Additionally, the fluke kernel adds a low-level interface including thread, address space and IPC mechanisms to the execution environment allowing convenient system construction. To overcome the exponential overhead of virtual machine stacking, the services of Fluke's microkernel are designed to support recursive systems: A system component has full access to all its children. For example recursively defined memory management through remapping, which is based on L4's model. All system services are based on capabilities, which allows to short-circuit the hierarchy of nesters when appropriate.

# 2.4 Summary

In this chapter we presented related work on virtual machine systems. The virtual machine abstraction represents an isolated duplicate of a physical machine. A virtual machine has three properties: equivalence, resource control and efficiency.

We showed that previous approaches to support virtual machines suffer from at least one of the following deficiencies:

- Para-virtualization systems require porting of at least the guest operating system towards the host system environment. Thus depend on source code access preventing full legacy reuse.

- Hypervisor-based VMMs only allow to run workload embedded in virtual machines. The virtual machine abstraction is insufficient as a general abstraction to construct system services running besides the virtual machines. It is often to coarse grained, preventing fine isolation and efficient interaction between system components. This results in compromises which may harm achievable isolation.

- Host-based virtual machine monitors attach their services onto a host operating system which may cause loss of full control of the host services. The host operating system causes a significant performance overhead. It further affects reliability, being dependent on the host system services, the VMM can only be as reliable as the complex and huge host operating system.

To overcome these deficiencies this thesis proposes the usage of a microkernelbased approach to construct a virtual machine system. Microkernels provide a minimal set of flexible abstractions to construct systems on top; they offer abstractions to express isolation and execution, and mechanisms to control usage of physical resources from user-level. Microkernels and virtual machine systems share a common set of goals such as isolation and resource control. Microkernels and virtual machines thus seem candidates for a tight integration to overcome the deficiencies of both, namely lightweight subsystems and reuse.

# **Chapter 3**

# Design

In this chapter, we present a novel approach for the construction of virtual machine systems. Our approach addresses the shortcomings in flexibility of current virtualization system architectures which are either based on a hypervisor or a host operating system. Both approaches have significant drawbacks, harming the virtual machine's main design goals: isolation and robustness. We propose to use microkernel principles to construct the virtual machine system. In the related work chapter we already showed that the microkernel-based approach and the virtual machine systems share a common set of goals such as isolation, resource control, and system integrity, to justify a tight integration of both. The microkernel provides a minimal set of flexible abstractions and mechanisms to construct arbitrary systems on top. We show that modern second generation microkernels already offer the necessary concepts to construct virtual machine environments through their minimal interface. We present a design which uses the concepts of the L4 microkernel to construct a virtual machine system. The resulting system comprises of a microkernel that also provides support for virtual machines and a microkernel-based system on top which includes components for maintaining the virtual machines. It combines the best of both worlds: Virtual machines provide strongly isolated containers with a stable environment, based on the platform API; whereas the microkernel approach enables construction of arbitrary, well-structured systems. The microkernel based approach can be seen as a fusion of the benefits of the hypervisor and the hosted virtual machine architecture.

This chapter is organized as follows: In Section 3.1, we first state our thesis goals and then point out a set of requirements and goals that should apply to our solution. These requirements induce our general architecture. In Section 3.2 we roughly describe the basic architecture of our virtual machine system and the microkernel's view of the VM. In subsequent sections we refine our design by describing how the virtual machine's resources are virtualized using L4's concepts.

# 3.1 Design Goals

The goal of our thesis is to construct a virtual machine system which is based on the principles of microkernels. The base of our system is an extended version of the L4 microkernel. This decision is based on the thesis that a microkernel provides a more flexible set of abstractions than current virtual machine monitors. The microkernel has to provide support for virtual machines as well as for native microkernel applications.

A valid solution must comply to the microkernel principle: aiming for a minimal, flexible system base which allows construction of arbitrary systems on top [60, 62]. Our solution has to follow this approach and use the microkernel construction principle to build the virtual machine system. Only the necessary privileged mechanisms of the virtual machine monitor are allowed to reside in the privileged kernel. The criteria is functionality: A primitive is only allowed in the microkernel if implementation outside the kernel would prevent the system from being usable. The virtual machine system logic is located in components residing on top of the microkernel.

We define following requirements and goals our approach should achieve:

- **Preserve Native Execution Environment.** Virtualization support is an extension of the microkernel functionality. Our solution has to sustain the core functionality of the microkernel; it should minimize the affect on the service quality of the other system components. Especially the performance of the fundamental mechanism of inter-process communication (IPC); IPC is master to achieve modularity, flexibility, security and scalability [59]. The goal of our design is to reduce the impact to a minimum.

- **Minimal Extensions.** The required microkernel extensions have to be reduced to a minimum [61]. To achieve minimal extensions we require our solution to reuse already provided microkernel abstractions and mechanisms whenever possible; reuse increases efficiency and homogeneity of the overall system. Our goal is to describe the virtual machine concepts via microkernel primitives; we do not want the resulting system to be a co-location of a microkernel and virtual machine hypervisor.

- Architecture Independence. The representation of the virtual machine and the mechanisms to manipulate and control its state have to be flexible. Especially they must not rely on specifics of a certain architecture. Following the microkernel principle we want to represent the virtual machine, using policy free abstractions and mechanisms [63]. This allows to apply our approach to other architectures than our target architecture for the implementation. For example, the mechanisms should hide the specifics of different hardware virtualization techniques (like Intel VT-x and AMD Pacifica).

# 3.2 Proposed Scheme

In this section we give an overview of our microkernel-based virtualization system. First we divide the virtual machine system into components. After that we give an overview of the microkernel's representation of a virtual machine. In the following chapters we refine the representation by mapping the resources which form a virtual machine onto the concepts offered by the L4 microkernel.

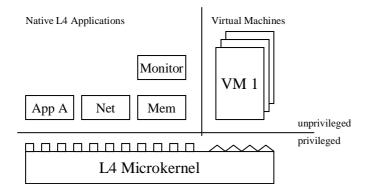

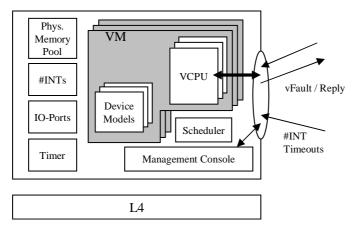

# **3.2.1** System Architecture

Our system is based on a microkernel. The microkernel approach gives a minimal system base, like in hypervisor-based architectures. But unlike hypervisors microkernels additionally provide system construction primitives; allowing to build arbitrary systems on top – including virtual machine environments. In our approach we divide the

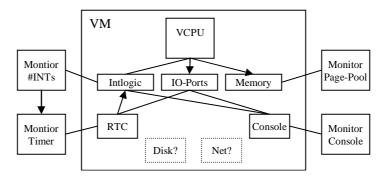

virtual machine monitor into a necessary privileged part, represented by the microkernel, and an unprivileged part, the user-level monitor application. The resulting virtual machine system consists of three components:

- **Virtual Machine:** The *virtual machine* is represented like all other user-level applications using L4 abstractions. It is a faithful duplicate of the physical machine platform.

- **Monitor:** The *monitor* defines and maintains the virtual machine environment. It implements the allocator and the interpreters of a conventional VMM architecture: It guarantees isolation by securely controlling the VM's access to physical resources and implements all complex aspects of virtualization, such as device emulation. As a normal L4 application, the monitor can interact with services offered by other user-level components to maintain the environment of the virtual machine, for example disk storage or network connectivity [32].

- **Microkernel:** The *microkernel* provides the execution environment for the virtual machine, the monitor, and the rest of the system. It ensures host-wide constraints such as integrity, and controlled execution of all system components. To securely execute the different components the microkernel offers abstractions for execution and isolation in which all system components are described including the virtual machines. For our virtual machine subsystem the microkernel implements the dispatcher module of the conventional VMM architecture. It uses hardware virtualization techniques where necessary [87] to run the virtual machine. The microkernel catches virtualization critical hardware events and either handles them transparently or dispatches them to the VM's registered monitor application.

Figure 3.1: Native microkernel applications including the unprivileged part of the virtual machine monitor run side-by-side with virtual machines.

Through the remainder of this chapter we stepwise refine our design and show the virtual machine representation in the L4 microkernel.

# 3.2.2 Virtual Machine Representation

In this section we give an overview of our virtual machine representation in our microkernel-based virtualization system. The focus of this thesis is the description of a virtual machine using L4 microkernel concepts including the interface which grants the user-level monitor full control of the VM's resources and execution.

A virtual machine is a hardware-software duplicate of a physical machine system. It includes all platform resources: the processor, physical/virtual memory and devices. In our system the virtual machine representation regards the requirements of three system components:

- 1. The guest running in the virtual machine requires an efficient, faithful duplicate of the physical machine system.

- 2. The monitor demands full control of the virtual machine, especially the allocated physical resources and their execution.

- 3. The microkernel needs a representation of the virtual machine's resources to enforce system-wide constraints such as isolation and integrity.

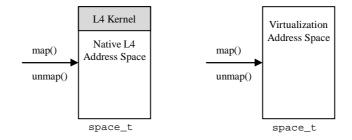

The L4 microkernel abstracts a virtual machine using an L4 address space. This space holds all resources directly accessible to the virtual machine. It allows L4 and the user-level monitor to enforce strict isolation. The L4 microkernel takes care that the virtual machine can only access the resources with its permissions, thereby establishing isolation and independence – core concepts of a microkernel [60].

L4 normally exports an *extended machine* interface to the user-level applications. This extended machine is similar but not identical to the underlying hardware; for instance L4 provides system calls and installs itself into each virtual address space. Native applications are aware of this changes and developed towards L4's extended machine interface. In a virtual machine environment this is impossible as the guest running in the virtual machine expects an environment which is a faithful duplicate of a real machine. For the virtual machine we introduced a new address space mode, the virtualization mode. In this mode, code executing does not experience L4's extended machine interface but the behavior of the platform API.

**Resources.** At the time of creation the virtual machine, its address space is completely empty and holds no permission to any physical resources. This establishes strong isolation of the virtual machine; the virtual machine can only operate on resources explicitly allocated to it. The monitor application can then selectively populate the virtual machine with resources, thereby defining the VM's environment.

Depending on the type of resource L4 already provides the required mechanisms of renaming, multiplexing and emulation of resources. In our virtual machine system resources can be divided into several groups:

• **Memory.** Resources with semantics like memory such as physical memory and IO ports can be controlled using L4's resource mapping mechanisms. The user-level monitor uses the already available L4 mechanisms of map/grant and unmap to fully control the access of physical resources in the virtual machine [9, 40].

The virtualization of memory-based resources is detailed in the Section 3.3.1 for physical memory and Section 3.3.2 for virtual memory.

• **Processor.** The most critical resource is the processor as virtualization is processorcentric [74]. The VM's processor (VCPU) is fundamental to the performance of the virtual machine. In our L4 based virtual machine system, we represent the VCPU with an L4 thread. It allows L4 to securely multiplex the VCPU onto the physical processors like all other threads in the system. For virtual machines we extend the thread abstraction to hold the complete processor state to handle the world-switch into a virtual machine.

For instance, the monitor application can use L4's thread manipulation primitives such as: create, delete, start and stop to control the execution, which is detailed in Section 3.3.3.

• **Peripheral Devices.** From the view of virtualization peripheral devices are a combination of memory, IO-ports and interrupts. The virtual machine can have either direct physical access as already supported for native L4 applications, or the device can be emulated in software in the basis of instruction faults.

In Section 3.3.4 we detail device related specifics.

The user-level monitor can freely define which physical resources are available to the virtual machine and thereby trade the size of a virtual machine with the efficiency; as physical resources avoid time-consuming emulation. In Section 3.3 we refine resource control and discuss the representation of resources for our virtual machine system.

**User-Level Control Protocol.** Virtualization is processor-centric, the user-level monitor needs access to the VCPU's state to emulate critical instruction and to maintain the virtual machine environment. From the viewpoint of L4, emulation is a matter of trapping. We introduce a new IPC-based fault protocol to grant the monitor full, transparent access to the VCPU to efficiently control the virtual machine's behavior. It dispatches virtualization critical events to the virtual machine's registered monitor. Access to a critical, non-present resource inside the virtual machine generates a trap which causes the virtualizable processor to leave the guest-mode and reenter the privileged-mode into the L4 microkernel. L4 then notifies that event to the VM's monitor application, to handle the fault. This protocol further allows the monitor application to inject virtual events from the device emulation into the virtual processor. It is detailed in Section 3.4.

The virtual machine representation in L4 needs no substantial extensions; L4 already provides the required primitives to manage virtual machines.

# **3.3** Virtual Machine Resources

In the following sections we present the virtualization of the virtual machine's resources in more detail.

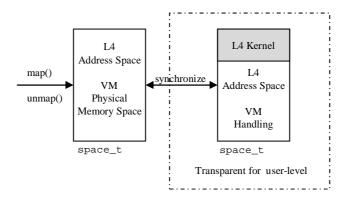

# 3.3.1 Physical Memory

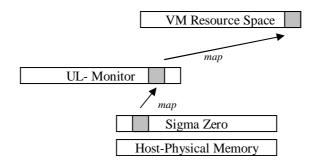

In this section we discuss the representation of physical memory in the L4 based virtual machine environment. A virtual machine can not have direct access to host physical memory; it would circumvent protection because on most hardware architectures physical memory access is uncontrolled – even on fully virtualizable processors. To virtualize physical memory virtual memory can be used [22]. We follow the approaches presented in [15,94] and use virtual memory to establish a layer of indirection which allows to fully control the accessible physical memory of a virtual machine. Virtual memory allows remapping of physical machine memory to give each VM the illusion

of a chunk of physical memory starting at address zero. Virtual memory is supported by hardware and thus very efficient.

In L4 an virtual memory space is represented by an address space. We use an L4 address space to represent the virtual machine's physical memory space. The monitor populates this space by using L4 map messages. It maps or grants parts of its own address space to the virtual machine's space.

Being the L4 pager of the virtual machine the user-level monitor can use L4's userlevel paging to completely control the management of the physical memory of a virtual machine. Through the page-fault protocol the monitor is notified on physical memory faults of the virtual machine. By mapping and unmapping the user-level monitor can provide memory resources at arbitrary locations and even with decreased rights, thereby allowing full control of the physical memory [40,60]. L4's mapping an unmapping mechanisms are very flexible. For virtual machines they can be used to establish controlled sharing such as content-based physical memory sharing or copy-on-write between different virtual machines [15,94].

For efficiency reasons, L4 does not offer the complete architecturally defined virtual address space to user level; the kernel keeps part of it for its own purposes. There is, however, no conceptual limitation in L4's mapping mechanism that would prevent managing the whole address space. A guest may require the physical complete address space of the virtual machine, and hardware support for virtualization makes it easy to provide the full address space.

The L4 API defines two mandatory objects in each address space: the kernel interface page and the user thread control block (UTCB) area. Their location is determined by the creator of the address space. Being part of the L4 virtual address space, they will appear as objects in the VM's physical address space. The monitor can freely define their position and thereby effectively hide them from the guest; for example by placing these objects in a unused region of the VM's physical address space. For the virtual machine environment, these objects can optionally removed from the VM's address spaces. To not preclude later optimizations such as efficient inter virtual machine communication (Section 3.5) both objects can still be mapped into the VM's space.

Figure 3.2: Physical memory hierarchy: The user-level monitor uses the virtual memory to provide the virtual machine with "virtualized" physical memory. L4 exports machine memory via the sigma zero address space. The monitor can request memory mappings to its own address space and pass it to the virtual machine.

### **3.3.2** Virtual Memory

We use L4's virtual memory management concepts to provide the VM's physical address space. However, the guest operating system in the VM usually wants to create virtual memory itself. To maintain the illusion of access to virtual memory, the virtual machine system must resolve a guest-virtual address into a host-physical address [94]. This translation consists of two stages. The first stage translates the guest-virtual address to a guest-physical address via page-tables maintained by the guest operating system located in guest-physical memory. The second stage is determined by the monitor's mapping of guest-physical addresses to host-physical addresses to enforce the resource constraints of the monitor; they overrule the requests of the guest. For example, this indirection can be used to transparently share physical memory of the machine as described in the previous section.

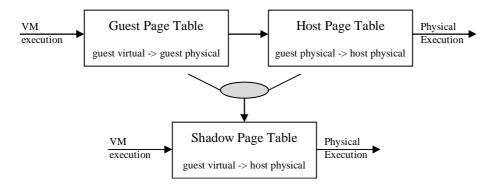

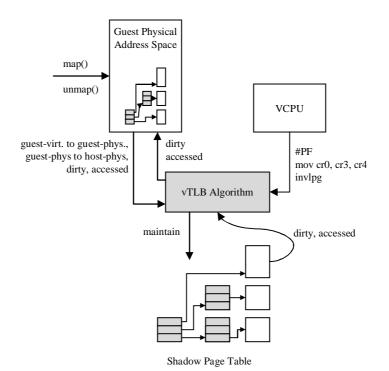

Most hardware lacks support for such a two-tiered memory translation, called nested paging. For efficient execution on the physical processor, both stages have to be merged into a single translation, the shadow page-table, which directly translates a guest-virtual into host-physical addresses. The shadow page-table can also be seen as a virtual TLB (vTLB) as it caches guest-virtual to host-physical translations. Figure 3.3 gives an overview of the shared page-table mechanism.

Figure 3.3: The shadow page-table is a fusion of two page-tables. Step one is defined by the guest operating system, located in guest physical memory. Guest physical memory is provided by virtual memory of the host system, which itself is implemented using a page-table. The shadow page-table is a combination of both in a hardware understandable form, to allow physical execution.

In our microkernel-based virtualization system, the generation of the shadow pagetable involves all three components of our system architecture. (i) The microkernel needs to enforce isolation and independence between the different L4 address spaces holding the applications and virtual machines. (ii) The monitor application requires full control of the physical resources occupied by the VM. (iii) The guest operating system, needs to create arbitrary virtual address spaces onto its guest-physical memory. We found two different approaches to maintain guest-virtual memory which we discuss next.

#### **Approach 1: User-Level Management**

One way to establish the guest-virtual to host-physical translation is to represent the VM's virtual address spaces as an L4 address space, described by the contents of the

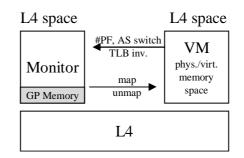

shadow page-table. The monitor directly constructs the shadow page-table using L4's map and unmap operations. VM-internal translation faults are propagated to the monitor which then walks the guest operating system's page-table to find the guest-physical address. It then maps pages from its own address space directly into the L4 address space representing the virtual machine, or injects the page-faults into the virtual machine as depicted in Figure 3.4. Page-fault injections accord page-faults which would occur when the guest executes on a physical machine.

Figure 3.4: User-Level vTLB Management: The user-level monitor L4 application uses L4's mapping mechanism to create the guest virtual address space. Virtual Memory related events in the VM are notified to the monitor application.

This approach allows the monitor application to fully control the guest virtual address spaces. The monitor can use a-priori knowledge of the guest operating system to optimize the virtual address space management. For example by avoiding address space flushes or establishing virtualization-aware drivers into the guest to reduce virtualization overhead.

However, this approach has several serious drawbacks:

- L4's mapping mechanisms abstracts from the underlying hardware page-table. To allow user-level management of address spaces it includes access rights such as read, write and execute, but it does not expose additional processor architecture specific parameters such as the distinction between user- and kernelaccessible memory. Their introduction would require architecture specific extensions of L4's mapping mechanism and these features would have to be disabled for all but VM-address spaces.

- L4 threads are associated with exactly one L4 address space. As a result, only the currently active guest virtual address space can be described by the L4 address space. An address space switch in the VM requires a complete flush and repopulation of the L4 address space of the virtual machine via memory mappings by the monitor. Introducing threadless address spaces, which are needed to represent currently inactive guest virtual address spaces, into the L4 microkernel would incur major API changes; for example the introduction of address space identifiers.

- Updates to the virtual TLB are very frequent operations, efficiency of the vTLB is paramount to the virtual machine's overall performance. We consider the cost of two address space switches and a map operation for every vTLB update too expensive.

Figure 3.5: In-Kernel vTLB Management: The L4 microkernel handles virtual memory related virtualization events transparently. Only events which are caused by nonavailable or insufficient rights to physical resources are signaled to the user-level monitor application.

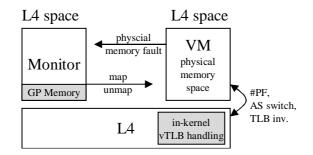

### **Approach 2: In-kernel Management**

The problems of the first approach can be avoided by emulating guest-virtual address spaces transparently inside the L4 microkernel. The VM's physical address space is represented by an L4 address space which is maintained by the monitor. It holds all physical resources of the virtual machine, including the physical memory. The approach is shown in figure 3.5.

The L4 microkernel catches page-faults on guest virtual memory. It walks the guest page-table to resolve the fault. The user-level monitor is only notified if the L4 microkernel detects that the fault is caused by non-present, or insufficient rights on the guest physical memory.

Of course, this approach has some disadvantages, too:

- In-kernel shadow page-table management can perform only very limited optimizations. Without introducing awkward configuration protocols, optimizations based on the knowledge of a specific guest's behavior are not possible.

- The complexity of shadow page-table management is rather high: The vTLB algorithm needs to walk the VM's guest physical memory, which may cause inkernel page-faults (that can be handled like faults during an string IPC handling). Furthermore, L4 uses one page-table format, while the guest operating system may use one of many, increasing complexity of the L4 page-table walker for the guest page-table.

#### **Taken Approach**

The authors of [7, 72] already identified the shadow page-table management of major importance for the overall performance of virtual machines. We expect *upcoming hardware* to natively support nested paging which will remove the need for shadow page-tables altogether [8]. Therefore, we prefer in-kernel vTLB management as a temporary, clean solution at the API level: If hardware support is present, L4 simply uses it without any further changes at the API level.

### 3.3.3 Processor

The virtual machine's processor (VCPU) is critical for the efficiency of the virtual machine [74]. Similar to other systems we use a thread to represent a virtual machine's processor [24, 26, 56]. The L4 thread abstraction represents a timeslice of the multiplexed physical processors. The execution of the VCPU can be controlled like all other threads in the L4 system. Like all other threads in L4, the VCPU is scheduled based on its timeslice and priority.

Currently L4's extended machine only exports the user accessible general purpose registers to the user-level applications. For the virtual machine we extended the thread abstraction to include the complete physical register set. To securely multiplex its threads, L4 maintains the processor context inside the microkernel. While executing the VCPU directly on the physical processor the fully virtualizable processor architecture helps to retain isolation and control as described in Section 2.1.1. The user-level monitor needs access to the VCPU context in two cases which we examine next.

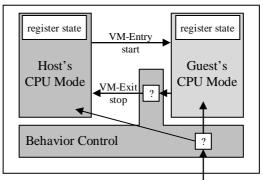

External Events: #INT, #NMI, #PF

Figure 3.6: A virtualizable processor consists of two execution contexts. The Host mode is active while the VMM runs. It configures the behavior control to securely execute the VM in the guest's mode.

# Handling of Critical Instructions

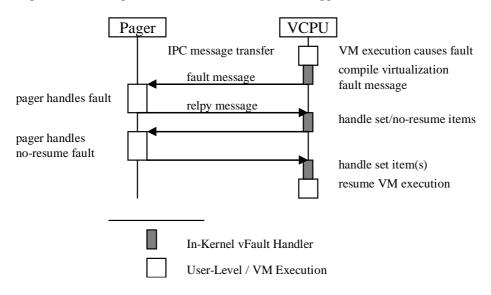

To emulate the virtual machine resources such as privileged registers or devices, the monitor needs to emulate the instructions accessing these resources. Fully virtualizable hardware allows to generate traps on these instructions, which cause an exit out of the virtual machine into the privileged part of the virtual machine monitor (here the L4 microkernel). L4 already provides an abstraction for these hardware exceptions: the IPC-based exception protocol. In the name of the faulting thread, L4 synthesizes a fault message to the associated user-level handler. The message contains the reason of the fault and a static subset of the user-visible CPU state. The handler resolves the fault by emulating the behavior of the faulting instruction, and sends a reply message back to resume the thread. This message contains the new CPU register state, to be established before resuming the thread.

For virtualization, exporting a static set of registers is too inflexible: the overall VCPU state is much lager, but the relevant state is small and depends on the exact fault reason. The authors of [18, 52] showed that emulation of critical instructions is a frequent operation and has strong influence on the virtual machine performance. Similar

# 22

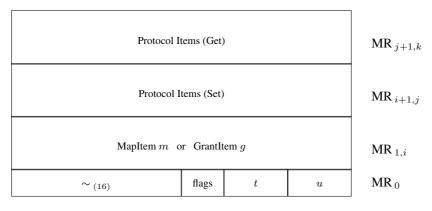

to the exception protocol, we propose a *virtualization fault protocol*. For each virtualization fault reason, an (architecturally) predefined part of the VCPU state is transfered in the fault message. In the rare case that the monitor requires more or different state than was sent in the fault message, the virtualization fault protocol provides the *get item*. This item contains a request for additional VCPU state; it causes the VCPU to immediately generate another virtualization fault without resuming execution of the VCPU. Thus the monitor can iteratively access the complete VCPU register state. The exact description of the virtualization fault protocol is described later in Section 3.4.

#### **Asynchronous Execution Control**

When emulating the behavior of active devices the monitor must be able to asynchronously modify a VCPU's state, for instance, to inject virtual device interrupts. L4 already provides a way to asynchronously manipulate another thread through the EX-CHANGEREGISTERS system call. EXCHANGEREGISTERS allows for native threads certain thread state to be read or written; but only within the same address space. Access to the complete register state has to be emulated by user-level protocols, for example, by inserting a helper thread into the destination address space, reachable via IPC, to do EXCHANGEREGISTERS locally. Inserting an L4 thread transparently into the virtual machine's address space is a major intrusion. The thread needs stub code for its protocol logic mapped into the VM's virtual address space, it needs the ability to invoke IPC, and its presence must not induce any side-effects in the guest.

To avoid introduction of an additional thread, the monitor can delay asynchronous events and piggyback them on the next synchronous virtualization fault reply. However, this is no general solution, because it may delay asynchronous events for too long – yet, it is an efficient optimization for high workload situations. As a minimally invasive method to asynchronously access the VCPU state, we favor the extension of EX-CHANGEREGISTERS across address space boundaries, a possibility to asynchronously force a virtualization event. We decided to map the asynchronous access onto the synchronous virtualization fault protocol. The extensions allow the monitor the force the VCPU to sent a virtualization fault. This avoids the introduction of two access formats, and the management of in-kernel message buffers. In-kernel buffers would be needed to store the event until the VCPU is ready to receive it, at a later point in time. The extensions of EXCHANGEREGISTERS include:

- An *immediate fault* causes the VCPU to immediately raise a virtualization fault. The monitor can use this to unconditionally inject events such as non-maskable interrupts or exceptions, or to inspect the VM's state, e.g., for debugging or introspection purposes.

- The *delayed fault* provides an efficient way to find the next point in time the VCPU is ready to receive certain events. This is necessary because the VCPU can not always inject hardware events immediately into the guest, for instance, interrupts when the guest operating system has interrupts disabled. The delayed faults cause the VCPU to raise a virtualization fault when the VCPU is ready to deliver such events the next time the guest is able to receive interrupts. The monitor can use the later virtualization fault to inject pending virtual interrupts [50].

Allowing a thread's pager and exception handler to invoke EXCHANGEREGISTERS does not introduce any security issues, as a pager is already a strongly trusted compo-

nent for the virtual machine. Apart from the VCPU register state, the monitor may need to access the VM's memory, e.g. to inspect the guest's page-tables. Accessing guest physical memory is not problematic for the monitor since it provided the memory from its own address space or knows the providing component.

# **3.3.4** Peripheral Devices

Peripheral devices are represented as a combination of physical memory, IO memory, and associated interrupt lines on the level of the processor interface.

#### **Memory Mapped Devices**

Memory mapped-devices are located in the guest physical address space. They are accessed by normal load/store operations, which cannot be trapped even by fully virtualizable hardware. Instead, access to memory-mapped devices can be tracked by page-faults on memory which represents the devices. It is sufficient because memory-mapped devices are aligned on the size of page-frames [75]. These page-faults should not be satisfied with a mapping but trigger an emulation of the accessing instruction to trap on further device accesses. Therefore, page-faults should also use the virtualization fault protocol. Unifying page-faults and exception handling is already under discussion in the L4 community for other reasons such as orthogonality of concepts.

# **IO Port Space**

On some architectures, such as IA-32, there exists an additional address space, the IO port space. In L4 these device ports are part of the L4 address space abstraction. Special port mappings allow the management of permissions of an address space to the physical IO ports [60,82]. For the virtual machine we use the IO port space to control the VM's permissions to the physical machine's ports. Non-sufficient permissions cause a special virtualization fault message to the user-level monitor, which can use the fault to emulate the associated device in software.

#### Interrupts

A virtual machine system has to cope with two types of interrupts: (i) physical interrupts coming from a real hardware device and (ii) virtual interrupts, which are created by a software device model representing an emulated device.

The L4 microkernel abstracts processor interrupt lines by special kernel threads. Interrupt events are abstracted by kernel generated IPC messages from the matching kernel thread to one associated handler thread.

In our virtual machine system the user-level monitor can use L4's interrupt IPC mechanism to receive interrupts of physical devices. Using the EXCHANGEREGIS-TERS system call with delayed faults, as described in Section 3.3.3, the monitor can then inject the physical interrupts and the synthesized virtual interrupts into the virtual machine. Direct delivery of physical interrupts into the VM is not possible as this would require the introduction of an second in-kernel mechanism to buffer interrupt events to deliver them into the VCPU when it is ready to receive the events. Another issue here is that L4 immediately masks interrupt lines when an interrupt appears. The interrupt line is unmasked when the associated handler notifies the kernel that is ready to receive another interrupt via an acknowledge IPC. For the VCPU thread this protocol can not be used as the required information to emulate this behavior is only available in the interrupt device emulation model of the user-level monitor.

# DMA

Using direct memory access in the virtual machine raises isolation issues [57]. To sustain full isolation and control, direct access to DMA-able devices for the virtual machine must be prevented; for example, by emulating the device in the user-level monitor application.

But none the less, it is possible to grant a virtual machine access to a DMA device. Here the user-level monitor who must have access rights to the device, grants access to the virtual machine. It must take care to establish the required degree of isolation by interposing the configuration of the DMA device. The L4 microkernel needs no further mechanisms to support DMA in the virtual machine as a DMA device can be controlled from the user-level monitor like every other device by controlling its physical memory, interrupt lines, and IO ports.

Trapping creates massive overhead which can be reduced by injection of virtualization aware device-drivers into the guest operating system [52]. Upcoming hardware support in the name of IO-MMU [49] or completely virtualizable devices [76] already attack this problem and may need kernel level support.

# 3.4 User-level Control Protocol

In this section we discuss the design of the communication protocol required to control the virtual machine environment from the user-level monitor.

# 3.4.1 Analysis of Requirements

The Monitor requires a protocol to (i) access the VCPU's register state, (ii) emulate resources of the VM, (iii) manipulate the VCPU's state and, at last, (iv) to signal certain events of the platform into the VCPU. The microkernel must implement a service which notifies the VCPU's monitor on behalf of the VCPU. The authors of [18, 52] showed that this communication is critical for the virtual machine system performance. Next we describe critical parameters of the control protocol.

**Execution Transfer.** The required communication mechanism between the VCPU thread and the user-level monitor has RPC semantics. Asynchronous events such as the delivery of interrupts are mapped on the synchronous protocol as described in Section 3.3.3. On a VM-Exit caused by an access to an emulated resource, the physical processor traps, L4 preempts the VCPU thread and notifies the user-level monitor. The VCPU needs to be suspended until the monitor notifies that the effect of the critical instruction has been completely emulated. For optimal efficiency L4 has to transfer execution directly to the user-level monitor – to donate the VCPU's time slice to the monitor.

**State Transfer.** On a VM-Exit the user-level monitor needs a certain subset of the VCPU register context to handle the fault. The author of [38] shows that most performant message transfer heavily depends on the details of the message and the target

architecture. In the following we discuss the communication schemes in the context of our requirements.

With *shared memory* the user-level monitor and the L4 microkernel have a mapping of the same physical memory allowing to transfer big messages without any copy overhead. In our scenario shared memory has a lot of disadvantages [36]. Shared memory softens the strict separation between the kernel and the user-level monitor. Zero copy transfers requires that the user-level monitor gets full access to the machine representation of the VCPU state. On some architectures this is not possible because the machine representation mixes safety critical state with uncritical state required by the user-level monitor.

In contrast to shared memory, *IPC messages* hide the kernel representation of the VCPU. IPC strictly separates the kernel from the user implementation allowing flexibility. As mentioned before, IPC is L4's core primitive and thus highly optimized [59]; it does not necessarily increase transfer overhead by message copying. L4's IPC is synchronous and allows to establish an RPC protocol. Also virtualization messages are usually very small [7], requiring only minimal copying overhead. Thus our communication scheme is solely based on IPC messages.

**Resource Population.** IPC messages allow to map resources in L4. IPC messages to VCPU threads allow to the user-level monitor to populate the physical memory into the virtual machine.

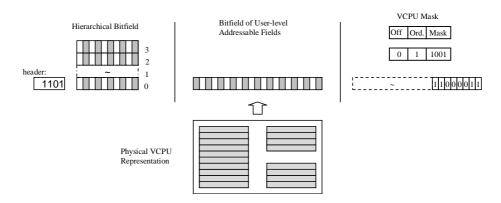

Accessing State. Our communication protocol is based on IPC messages. To reduce the copy overhead only the necessarily required state should be transfered between the user-level monitor and the in-kernel VCPU representation. As discussed in Section 3.3.3 the necessary state heavily depends on the architecture an the exact reason of the fault. We identified four cases which must be regarded by our protocol:

- 1. Some faults have a static behavior and thus require an architecturally predefined subset of the VCPU's state (for example the rdtsc instruction of the IA-32 processor). This state can be contained directly in the fault notification IPC.

- 2. Some faults have a dynamic behavior. For optimal performance the monitor may need to change the state contained in the fault message during the lifetime of a virtual machine.

- 3. Faults may have rare corner cases which require much more information to resolve them. To avoid performance overhead for treatment of these rare cases, the protocol needs am mechanism to gather additional state without resuming the VCPU. This mechanism can also be used to fetch additional state, for example, if the complete state does not fit into one IPC message.

- 4. The resume IPC notification holds VCPU state which is installed before the VCPU thread is resumed.

Addressing State. To identify the involved VCPU registers of a fault message or a VCPU state update the protocol needs to name the addressed VCPU registers. Only the registers which do not have side-effects to the host operation are user-accessible. We give each user-accessible VCPU register an unique index. Only through these indices the user-level monitor can name the registers. All addressable registers are uncritical,

26

# 3.4. USER-LEVEL CONTROL PROTOCOL

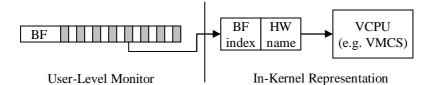

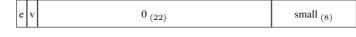

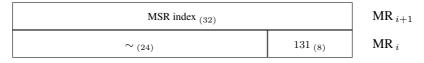

Figure 3.7: The kernel exports the user-level accessible registers via a bit-field. The user-level monitor can use only the bit-field indices to address the VCPU state. The kernel translates the indices into a hardware-usable form by a simple lookup table.