System Architecture Group

Department of Computer Science

### Design and Implementation of a Microkernel-Based Operating System for NUMA Machines

Philipp Kupferschmied

Diplomarbeit

Verantwortlicher Betreuer: Prof. Dr. Frank Bellosa Betreuender Mitarbeiter: Dipl.-Inf. Jan Stöß

| Hiermit erkläre ich, die vorliegende Arbeit selbstständig verfasst und keine anderen als die angegebenen Literaturhilfsmittel verwendet zu haben. |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| I hereby declare that this thesis is a work of my own, and that only cited sources have been used.                                                |

| Karlsruhe, den 20.03.2008                                                                                                                         |

| District Konformalisated                                                                                                                          |

| Philipp Kupferschmied                                                                                                                             |

|                                                                                                                                                   |

|                                                                                                                                                   |

#### Abstract

Systeme mit uneinheitlichen Speicherzugriffszeiten sind die konsequente Weiterentwicklung klassischer Mehrprozessorarchitekturen. Anstelle alle Prozessoren mittels eines gemeinsamen Speicherbusses an einen gemeinsamen Hauptspeicher anzubinden, ist jede CPU über einen eigenen Speichercontroller und -bus an eigenen, lokalen Speicher angebunden. Auf diesen lokalen Speicher kann die CPU schnell zugreifen, wohingegen Zugriffe auf entfernten Speicher, also Speicher anderer CPUs, länger dauern. Dieser Ansatz hilft, die begrenzte Skalierbarkeit klassischer SMP-Architekturen zu überwinden, bei denen Speichercontroller und -bus mit steigender CPU-Zahl zum Flaschenhals werden. Die unterschiedlichen Speicherzugriffszeiten stellen eine zusätzliche Herausforderung sowohl für Betriebssystementwickler als auch für Anwendungsentwickler dar. Um bestmögliche Leistung zu erreichen, sollten Daten immer möglichst nah an der auf sie zugreifen CPU gehalten werden. Migration und Replikation sind wichtige Mechanismen zur Verbesserung der Lokalität, aber es hängt von vielen Faktoren ab, welcher der beiden Mechanismen vorzuziehen ist oder ob sie überhaupt anwendbar sind. Diese Faktoren sind unter anderem die Zugriffshäufigkeit, das Verhältnis zwischen Leseund Schreibzugriffen und der Grad, zu dem das betroffene Objekt gemeinsam (also von mehreren CPUs gleichzeitig) genutzt wird. In dieser Arbeit stellen wir ein auf NUMA-Hardware optimiertes Betriebssystem vor, das auf dem L4 Mikrokern basiert. Es werden sowohl notwendige Modifikationen am Kern selbst als auch der Aufbau der im Userlevel realisierten Systemdienste vorgestellt. Insbesondere stellen wir ein Konzept vor, das die Replikation von Seitentabellen erlaubt und die notwendige Synchronisation vollständig im Userlevel durchführt.

#### **Abstract**

Systems with non-uniform memory access characteristics are the consequent evolution of "classical" SMP systems. Instead of all CPUs being connected to a single shared memory via a single memory bus, each CPU is assigned its own "local" memory, which it can access directly and thus fast. Access to memory of others CPUs is possible, but is slower than local access. This model overcomes the scalability problems of classical SMP architectures, where the memory controller and bus become a bottleneck with an increasing number of CPUs in the system. However, the non-uniform access latencies pose new challenges to both operating system and application developers. Data should be kept local to the accessing CPU wherever possible. Migration and replication can be used to improve data locality, but the choice for the right mechanism depends on many factors like access frequency, read-to-write ratio, and the degree of sharing of an object. In this thesis, we propose a design for a NUMA-aware operating system based on the L4 microkernel. We discuss necessary modifications to the kernel and present a design for user-level operating system services and applications. We present a concept that allows for replication of page tables with synchronization performed entirely at user-level.

# Contents

| 1 | Intr | oduction                                   | 1 |

|---|------|--------------------------------------------|---|

|   | 1.1  | Problem Definition                         | 2 |

|   | 1.2  | Organization of the Document               | 3 |

| 2 | Bac  | 8                                          | 5 |

|   | 2.1  | 1 0 1                                      | 5 |

|   |      | 2.1.1 The L4 Microkernel                   | _ |

|   | 2.2  |                                            | 9 |

|   |      | 2.2.1 Memory Management for NUMA Systems   |   |

|   |      | 2.2.2 Microkernels and NUMA architectures  | 3 |

|   | 2.3  | Synchronization                            | 4 |

| 3 | Des  | ign 1'                                     | 7 |

|   | 3.1  | System Architecture Overview               | 8 |

|   |      | 3.1.1 Pager/Memory Manager                 | 9 |

|   |      | 3.1.2 Load Balancer                        | 0 |

|   | 3.2  | Node-Local User-Level Data                 | 0 |

|   |      | 3.2.1 A First Approach                     | 0 |

|   |      | 3.2.2 In-Kernel Replication of Page Tables | 1 |

|   |      | 3.2.3 Using Different Address Spaces       | 3 |

|   | 3.3  | Kernel Objects                             | 7 |

|   |      | 3.3.1 Page Tables                          | 7 |

|   |      | 3.3.2 Thread Control Blocks                | 8 |

|   |      | 3.3.3 Mapping Database                     | 1 |

| 4 | Imp  | lementation 3                              | 3 |

|   | _    | Kernel Objects                             | 3 |

|   |      | 4.1.1 A NUMA-Aware Kernel Memory Allocator | 4 |

|   |      | 4.1.2 Address Spaces                       | 5 |

|   |      | 4.1.3 Replication of Kernel Code           | 7 |

|   |      | 4.1.4 TCB Migration                        | 7 |

|   | 4 2  | User-Level Services 3                      | Q |

vi *CONTENTS*

|   | 4.2.1 User-Level Pagers                 | 38 |

|---|-----------------------------------------|----|

|   | 4.2.2 System Call Servers               | 45 |

|   | 4.2.3 Application Startup               |    |

|   | 4.2.4 Thread Migration                  |    |

|   | 4.2.5 Local and Global Mappings         |    |

|   | 4.2.6 Static and Dynamic Page Placement |    |

| 5 | Evaluation                              | 51 |

|   | 5.1 Evaluation Environment              | 51 |

|   | 5.2 NUMA Memory Latencies               | 51 |

|   | 5.3 TCB Migration and Code Replication  |    |

|   | 5.4 User-Level Architecture             |    |

|   | 5.4.1 Establishment of Mappings         |    |

|   | 5.4.2 Revocation of Mappings            |    |

| 6 | Conclusion                              | 67 |

|   | 6.1. Suggestions for Future Work        | 68 |

# CHAPTER 1

Introduction

Systems with non-uniform memory access (NUMA) characteristics are the consequent evolution of classical symmetric multiprocessor (SMP) systems. On SMP systems, all processors are connected to main memory with a single memory bus and a single memory controller. Thus, the entire memory can be accessed with the same latency by all processors. However, with an increasing number of CPUs in the system, the memory bus becomes a scalability bottleneck. In contrast, on NUMA systems, each CPU (or group of CPUs) has its own, local memory, to which it is connected via its own memory controller and memory bus. The combination of CPU(s), memory controller/bus, and local memory is called a node. Node-local memory can be accessed fast, while accesses to memory of other nodes can be significantly slower. However, NUMA systems still provide a contiguous physical address space. An operating system or application developed without regard for the NUMAness of the hardware will run without modifications, but might perform poorly. NUMA-systems have become popular for UNIX-based servers in the mid 1990s. Nowadays, NUMA systems are likely to become popular as well for smaller servers and workstations. For example, the AMD Opteron, a widely used x86-compatible CPU in small servers and even desktop systems, is NUMA-capable: Each CPU has its own built-in memory management logic, and can directly access a subset of the machine's main memory. It is thus not surprising that both recent versions of Microsoft Windows and Linux provide mechanisms for exploiting NUMA capabilities of the hardware [3].

Windows and Linux are, like most other operating systems used nowadays, based on monolithic kernels. All system services and most of the device drivers are linked to a single, huge kernel binary. This approach provides no isolation between components, an error in one component can thus affect the entire kernel. With increasing size and complexity of operating systems, the probability for errors increases, while finding and fixing these errors becomes more difficult. Microkernels promise a way of overcoming these problems. Instead of having a single kernel image, there is only a small, privileged code base, the microkernel. System services and device drivers run as user-level applications within their own protection do-

mains. A microkernel must therefore provide a high degree of flexibility to allow for the construction of arbitrary systems on top.

#### 1.1 Problem Definition

To exploit the capabilities of NUMA systems, operating system and application programmers must address efficient code and data placement. Even on systems with a low remote-to-local access ratio, the performance benefits of a better memory placement can be quite high [35]. It is therefore important that the operating system itself places its own data in an "efficient" way, and that application programmers have a possibility to influence memory placement of their applications. Common solutions to provide better locality are migration and replication. Migration means that data is moved to the node from where it is accessed most frequently. Replication means that multiple copies of an object are created and placed on different nodes. The choice when and where to migrate data is not an easy one, as one has to decide when the costs for remote memory accesses outweigh the costs for migration (i.e. copying the data and updating references). In case of replication, synchronization overhead can eliminate performance advantages of local accesses, making replication only suitable for data that is more frequently read than written. Our work focuses on microkernel-based operating systems. In addition to the afore mentioned requirements, there are some microkernel-specific additional problems. A microkernel should be kept "small", with "small" referring not primarily to its code size, but meaning that the microkernel should only consist of what is absolutely necessary for correct system operation. In particular, the kernel must be kept policy-free to allow for the construction of arbitrary operating systems on top. Therefore, policies regarding migration and replication of memory or processes are to be implemented at user-level. The microkernel should not make any assumptions on memory or process placement, nor should it influence or limit the user-level policies. Additionally, in-kernel synchronization primitives should be avoided when possible. The choice for the best synchronization primitive depends on access and sharing patterns of the data that is "protected" by the synchronization primitive, but in case of NUMA hardware also on the ratio of remote to local latency. A static synchronization primitive within the microkernel thus would limit the kernel's flexibility and contradict the principle of keeping the kernel free of policies. Finally, also applications running on top of the operating system must be able to exploit the hardware characteristics of a NUMA system. The operating system must offer an API that allows applications to influence both memory and thread placement, or it must automatically choose a "good" memory placement for applications. Hence, we have to tackle the following problems:

- 1. All data structures used by the microkernel must be revised in order to find out if they can be replicated or migrated.

- 2. The kernel must be kept minimal. We therefore need to find out which NUMA-specific changes to the kernel are absolutely necessary and which can be handled at user-level.

3. Applications must be given the possibility to exploit the NUMA-capabilities of the hardware.

In the following chapters, we present our design and implementation of a NUMA-aware, microkernel-based operating system. Our work focuses on the L4 microkernel, which was not designed with a special regard to NUMA architectures.

### 1.2 Organization of the Document

This thesis is organized as follows: In Chapter 2, we describe both microkernel-based systems and multiprocessor architectures, with the focus on NUMA architectures. We present related work regarding different aspects of NUMA-aware operating systems. In Chapter 3, we start with an overview of our proposed system architecture for a microkernel-based NUMA-aware operating system. We then go into detail and have a closer look both on the requirements the microkernel must satisfy and on the operating system services we construct on top. Chapter 4 details our implementation. We describe the changes that were necessary to the L4 microkernel as well as the implementation of user-level operating system services. In Chapter 5, we analyze the performance of our implementation. We compare the results to the unmodified kernel. Chapter 6 concludes with a recapitulation of our work and with proposals for future work.

### Background and Related Work

### 2.1 Microkernel-Based Operating Systems

Most operating systems used nowadays are monolithic. That means that all OS services such as pager, scheduler, and device drivers run in a single protection domain. On the one hand, this greatly simplifies interaction between components: All data is directly accessible by all services, and a service can be requested with a simple (and cheap) function call. On the other hand, with increasing OS complexity, those systems get harder to debug. An error in one component can affect other components or even the entire system. Microkernel-based systems follow another approach: Instead of having all services running with the same privileges and within the same protection domain, the basic idea is to keep the privileged part of the operating system as small as possible. This leads to a system with only a small microkernel running with high privileges, while OS services are implemented as user-level applications (called servers), strictly isolated from each other. Ideally, the microkernel itself should be as flexible as possible, allowing for arbitrary operating systems to be constructed on top. This requires the microkernel to be policy-free.

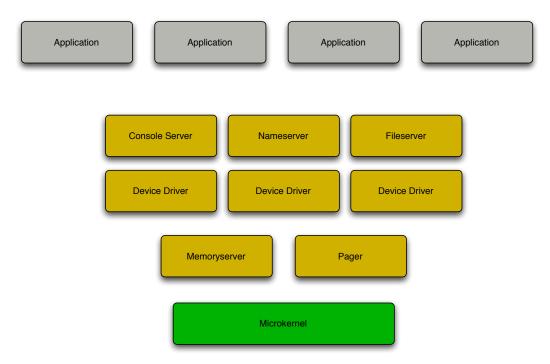

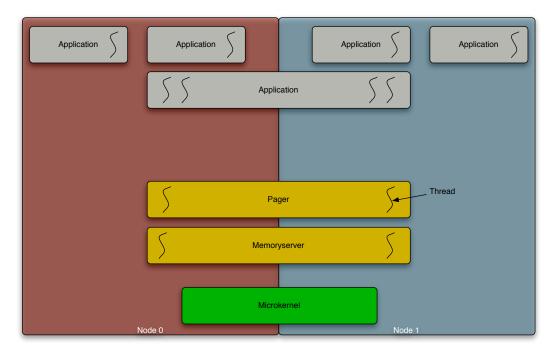

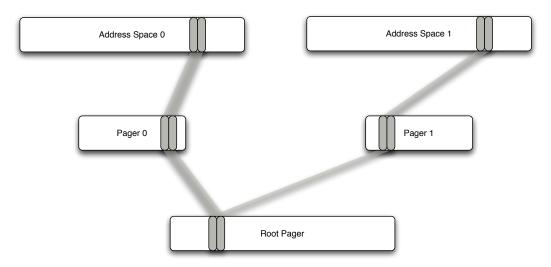

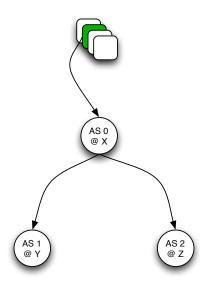

In contrast to the monolithic approach, interaction between components becomes much more complicated. Data of one component is no longer accessible by all others, unless it is explicitly shared. A service call is no longer a simple function call, but requires the crossing of protection domain boundaries. Both for sharing of data between address spaces and for invoking services across address space boundaries, the microkernel must provide a suitable mechanism. Figure 2.1 shows an example of a microkernel-based operating system. On top of the microkernel run several operating system services like a pager, a memory server, and several device drivers, each within its own protection domain. User applications request services provided by these servers. For example, when a page fault occurs in an application's address space, the kernel notifies the pager. The pager might then have to request a new page of physical memory from the memory server, which it can map into the application's address space (by using an appropriate mechanism

provided by the kernel) so that the application can resume execution.

In contrast to a monolithic operating system, management information is distributed amongst the microkernel and the user-level services. For example, a pager handling a page fault requires knowledge about the layout of the faulting task's address space, i.e. it must know which data to map at the address where the fault occurred and where that data can be found. The microkernel does not have or require this knowledge. In contrast, only the microkernel can directly modify the hardware page tables. A user-level pager (or any other user-level application) must not be permitted direct access to hardware page tables for security reasons. Consequently, the microkernel must offer an API that allows a pager to install new mappings in a secure manner.

Figure 2.1: Exemplary design of a microkernel-based operating system.

The microkernel approach promises several advantages: The absence of policies in the kernel allows for reuse of the microkernel for operating systems of very different kinds. The strict isolation of components improves system stability, as errors within one component ideally do not affect the rest of the system. Furthermore, components can easily be exchanged as long as their API remains the same.

#### 2.1.1 The L4 Microkernel

L4 is a microkernel of the second generation, originally developed by Jochen Liedtke [23–25]. Apart from some exceptions, it implements the afore mentioned absence of policies in the kernel. It offers two abstractions, threads and address spaces, where threads represent an entity of execution (and thus CPU time), and address spaces represent protection domains. Additionally, L4 offers two basic mechanisms, mapping and inter process communication (IPC).

#### Threads and Address Spaces

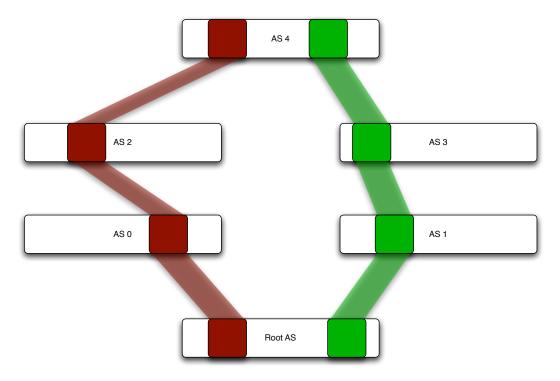

Threads and address spaces are the abstractions offered by L4. A thread is an entity of execution, identified by a unique thread ID. Threads are also the end points of L4's IPC (see below), i.e. a thread can send a message to another thread. Address spaces form protection domains, that is, data from one address space cannot be accessed from within another, unless it is explicitly shared. A thread always belongs to exactly one address space, but an address space can contain an arbitrary number of threads. Address spaces are identified implicitly by the thread IDs of their threads. Address spaces are populated by mapping memory into them. A thread running in an address space can map or grant any page of memory from its own address space to any other address space, as long as there exists a thread willing to receive mappings. This leads to a recursive model of address space construction, as shown in Figure 2.2. Originating from a root address space (called Sigma0), other address spaces are populated by mapping memory into them. This design also influences the behavior of unmapping memory from an address space (or restricting access rights): When a thread inside an address spaces decides to unmap a page, the page is removed from all address spaces it was mapped on to. The programmer has the choice if the page shall also be unmapped from the current address space (referred to as flush) or only from subsequent address spaces (referred to as unmap). For example, if a thread in address space 0 in Figure 2.2 performs an unmap on the red page, this page would be removed both from address space 2 and address space 4, but not from address space 0. In case of a flush, it would also be removed from address space 0.

Figure 2.2: Recursive construction of address spaces.

#### Interprocess Communication

L4 offers an IPC primitive that allows for efficient communication between threads. L4's IPC is synchronous, meaning that both sender and receiver must explicitly invoke an IPC operation and that they are blocked until the operation completes. The kernel thus does not need to buffer any message contents. A message can consist of both untyped and typed items. Typed items can be map items, grant items, or string items. Map and grant items allow for mapping/granting of memory from one address space to another. String items can be used to transfer larger message contents, i.e. to copy arbitrary amounts of data from one address space into another. To transfer message contents and to control IPC operations, each thread has a number of message registers (MRs) and buffer registers (BRs). MRs are used to transfer the contents of the message, BRs control the receiving of string items.

IPC is also possible for threads residing on different CPUs. In that case, interprocessor interrupts are used to synchronize CPUs, making cross-CPU IPC more expensive than IPC between two threads on the same CPU.

#### Page Fault, Exception, and Interrupt Handling

As stated before, L4 is policy-free. Arbitrary policies can be implemented on top. Therefore, also page fault, exception, and interrupt handling is delegated to user-level servers.

Page Faults Each L4 thread is assigned a pager thread, that is responsible for handling the thread's page faults. L4 makes no restrictions regarding the pager hierarchy, the only condition that must hold true is that each thread is assigned exactly one pager. When the hardware raises a page fault exception, the kernel checks in which address space the page fault occurred. If it is valid, the kernel sends an IPC message to the faulting thread's pager on behalf of the faulting thread. The message contains the virtual address the thread faulted on, the instruction pointer of the instruction that performed the access, and the kind of access it performed (read, write, or execute, if the hardware supports this). The pager's reply specifies the page of memory that shall be mapped to the address the thread faulted on. L4 offers fpages to specify memory that shall be mapped. Fpages are an abstraction of hardware memory pages. The smallest possible size of an fpage is the hardware page size offered by a specific machine, but fpages can also be larger than the largest page size the hardware supports. The kernel handles the pager's reply message transparently for the faulting thread by establishing the correct mapping and then discarding the reply message.

**Exceptions** Exceptions are handled in a way similar to page faults. A thread can be assigned an exception handler thread. When an exception occurs, L4 generates an exception message on behalf of the thread that raised the exception. This message contains the faulting instruction pointer as well as architecture specific exception words. The handler's reply contains the instruction pointer where the thread shall be resumed, and can optionally contain additional architecture specific words.

2.2. NUMA SYSTEMS 9

**Interrupts** On L4, hardware interrupts are regarded as hardware-implemented threads, and consequently identified by a thread ID. The interrupt handler for a hardware interrupt must be registered as the interrupt's pager. When the hardware raises an interrupt, the interrupt thread sends an IPC to it's handler (i.e. pager). The corresponding hardware interrupt is disabled until the handler replies with a reenable message.

#### **Basic System Services**

In addition to the microkernel itself, two servers are always created on system startup: Sigma0, which is the root pager and thus owns all available physical memory (including device memory), and a roottask. Sigma0 hands out physical memory to applications (either by the applications explicitly requesting the memory or by handling page faults). Yet, Sigma0 hands out each free physical page exactly once. This is for security reasons: At system startup, all memory is distributed amongst the operating system services that require it (e.g. pagers). If another process attempts to request memory from Sigma0 afterwards, the request will fail.

The roottask and all threads that are created in the roottask's address space later on are privileged in that they are allowed to execute certain L4 system calls, mainly for thread and address space creation and manipulation. Threads running outside the roottask's address space are not permitted to execute these system calls. Instead, a system call server thread running in the roottask's address space can be used as a wrapper for system calls, allowing to implement additional security policies at user-level.

With this initial configuration, it is possible to create all other necessary servers and thus bootstrap the entire system.

#### Performance Analysis

As seen in the previous paragraphs, even elementary system services like pagers, exception handlers, and interrupt handlers are implemented as user-level applications. A thread requesting a service offered by a server must use L4's IPC primitive to call that service. The most common case of IPC is communication between two threads in different address spaces, but on the same CPU. In that case, a single IPC send operation requires to change the privilege level (i.e. to enter the kernel), to switch address spaces, and to change the privilege level again (to leave the kernel and switch to the receiver thread). The same effort is needed for the reply. With hierarchical services, the required number of IPCs can increase dramatically. Although L4 is said to be one of the fastest microkernels currently available, one must keep IPC costs in mind when designing a system architecture. Long call chains should be avoided as well as communication across CPUs. Shared memory can be an alternative in some cases.

## 2.2 NUMA Systems

Multiprocessor systems in general are systems with more than one CPU (or CPU core). With symmetric multi-processing, all CPUs in the system are equal in that

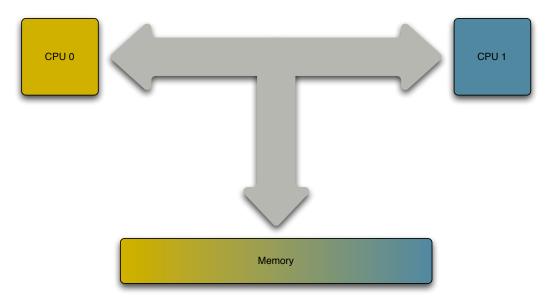

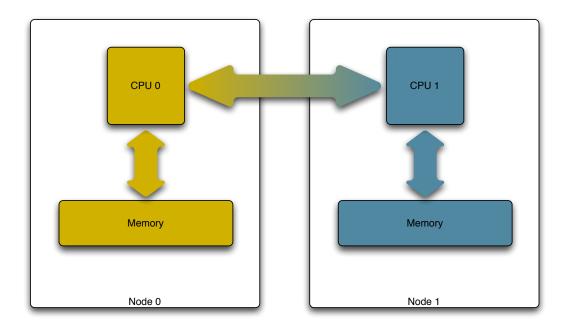

every CPU can execute every task. In a "classical" SMP system, all CPUs are connected to a single shared memory via a single memory controller and bus. This design ensures uniform access latencies for the entire memory, but the memory interconnect becomes a bottleneck with increasing number of CPUs. Parallel memory accesses of multiple CPUs must be serialized and thus limit scalability of SMP machines. Systems with a non-uniform memory architecture (NUMA) are very similar to SMP systems, but eliminate the single memory interconnect as a bottleneck. Instead of having all CPUs equally connected to main memory, the system is partitioned in so-called nodes, where each node consists of one or more CPUs (or cores) and an amount of node-local memory (together with a memory-controller). Nodes are connected via a fast local interconnect. This interconnect allows a CPU to access memory of another but the own node (so-called remote memory). However, remote accesses can be much more expensive than accesses to local memory. Costs depend on hardware and timing characteristics, but also on the distance (i.e. the number of hops) between the CPU performing the access and the memory that shall be accessed. Figure 2.3 and 2.4 show simple examples of an SMP- and a NUMA-system, respectively.

Figure 2.3: A "classical" SMP system with uniform memory access characteristics. Both CPUs are directly connected to a single shared memory.

Nowadays CPUs normally have a hierarchy of caches to reduce the number of code and data fetches from main memory. Caches pose additional challenges to multiprocessor system: If data in memory is altered by one CPU, there might still exist copies in another CPU's cache. These copies must be found and either be updated or invalidated. This cache coherence nowadays is commonly hardware-implemented. In case of NUMA systems, one also speaks of *ccNUMA* if cache coherence is ensured "automatically", i.e. in hardware. In this work, we do not deal with NUMA systems where cache coherence is ensured in software. Therefore, we use the terms NUMA and ccNUMA interchangeably.

While NUMA allows for better scalability with high numbers of CPUs, it also

Figure 2.4: A NUMA system consisting of two nodes, each with one CPU. Accesses to remote memory are passed over the interconnect between the CPUs.

makes system- and application programming more complicated. Operating systems and applications designed only with regard to SMP machines will also run on NUMA machines, but with performance penalties, especially on large-scaled machines with a high remote-to-local latency ratio.

#### 2.2.1 Memory Management for NUMA Systems

Optimizing data locality on NUMA systems is an important requirement to allow for good performance of both operating system and applications. Data locality means that data is placed on the node or near to the node where it is accessed from. There are two general possibilities: Manual placement, where the application programmer decides on which nodes memory is allocated and when and where to move it, and automated placement, where the operating system or a memory manager make these decisions at runtime, depending on the current system behavior. Both approaches have advantages and disadvantages, and combinations of both are possible.

Cox and Fowler implemented a coherent memory abstraction for NUMA systems, which hides most of the hardware's NUMA characteristics by transparently replicating and migrating pages [13]. The authors replicated page tables to allow for per-CPU mappings of replicated code and data. They state that replication of page tables does not limit scalability because a page table needs not contain all mappings of an address space, i.e. can be synchronized lazily when necessary. For shootdowns, the authors chose an approach that requires notification only of those processors that are using a mapping of the affected page. Additionally, only processors on which an affected address space is currently active need to be interrupted. Our approach for updating page tables is similar in that we also populate page

tables lazily. For unmaps, we are also able to determine a subset of all processors that must be notified. However, as our approach works entirely at user-level and uses only abstractions and mechanisms offered by the L4 microkernel, we are not able to tell which address space is currently active on a specific CPU.

Bolosky et al. [7,8] implemented several NUMA memory management policies and compared them to an off-line, optimal cost policy. Their results show that a good NUMA policy is of importance, as it can improve overall program performance by as much as 25% to 50%, and that different memory architectures can require different policies. They identified false sharing as a dominant factor that negatively affects application performance.

Sandhu et al. [34] argue that a hardware page is the wrong abstraction for managing shared data, because data sharing in applications does not occur at page granularity. Instead, they group locations of shared data that are accessed together and in the same way (read and/or write) to a so-called shared region. Cache and memory coherence is then enforced at region granularity. Yet, an application programmer must manually specify regions in the source code. Before data of a region is accessed, a process must explicitly request read or write access. Such a request not only performs locking, but also interacts with the system to enforce cache and memory coherence. While the authors state that their approach has several advantages over traditional NUMA memory management schemes (like reduced false sharing and reduced costs for maintaining consistency), the disadvantage of their approach is that it relies on information either given by the application programmer or by the compiler.

The authors of [27] showed that a simple first-touch allocation policy can lead to significant performance improvements both on systems with hardware and software coherent caches. To deal with the problem that one thread initializes data that is later used by another thread on another node, the authors introduced a "done with initialization" annotation, allowing a programmer to specify the point at which the operating system should begin with dynamic placement. An additional "phase change" annotation can be used to tell the operating system to reevaluate its placement decisions. More sophisticated migration and replication strategies (including some which require additional hardware support) did not lead to much improvement for the programs used for evaluation.

In [40], the authors developed an algorithm to decide whether a page of memory shall be migrated or not. Their approach requires information about cache misses or TLB misses, both on a per-page granularity. The hardware raises an interrupt when the number of misses exceeds a predefined threshold. Their approach achieved good results, however, the required hardware support is not available on most machines.

The authors of [32] implemented a user-level solution for dynamic page migration, loosely based on the afore mentioned approach. Their approach also requires reference counters per page, which are available on the SGI Origin2000 hardware they used.

The authors of [9] focused on building an x86-based NUMA system. However, special hardware was used to realize the interconnect between nodes and to allow for monitoring of memory accesses. The gathered information was not used for dynamic page migration/replication, but only for profiling purposes, allowing

2.2. NUMA SYSTEMS

an application programmer to find and eliminate performance bottlenecks and to manually optimize a program to improve data locality.

[26] suggests another approach. The authors used x86 performance counters to capture memory accesses and logged calls used for memory allocation during a first run of a program. From the collected information, a profile is generated, which can then be used to take better page-placement decisions when the program is run a second time.

The authors of [22] compared various policies for dynamic page replication and page migration. They derived the following conclusions from their observations: The performance of programs written for UMA architectures can be improved by applying dynamic page migration and replication, but normally does not achieve the performance of "hand-tuned" programs. They didn't find a single policy that could be considered as best for all kinds of programs that were used for benchmarking.

#### 2.2.2 Microkernels and NUMA architectures

IPC performance is of paramount importance for microkernel-based operating systems. Gamsa et al. optimized IPC for shared-memory multiprocessors [15]. Their design is based on protected procedure calls rather than on message passing. It preserves parallelism and avoids accesses to shared data and locking in the common case. A service call is always executed on the CPU of the caller, thus avoiding cross-CPU notifications. Although their implementation runs on a NUMA machine, the authors state that the non-uniform memory access time had no measurable effect on the IPC performance because their design avoids accesses to remote memory. In contrast, L4's IPC based on message passing allows for communication between threads on different CPUs (with considerably higher costs because of the required cross-CPU notifications). Our user-level design aims for minimizing the required number of cross-CPU IPCs and for preserving parallelism by explicitly replicating service threads per CPU. Yet, we cannot completely avoid cross-CPU IPC, but require it for unmapping memory.

The Raven kernel [33] is a microkernel tailored to shared memory multiprocessors. Many of its services are implemented at user-level, with the goal to minimize kernel invocations. However, the Raven kernel focuses on systems with a uniform memory architecture, not on NUMA systems.

Tornado [14] and its successor K42 [4] are both microkernel systems designed with a special regard towards NUMA machines. An object-oriented structure is used to reduce contention and to improve locality. Furthermore, Tornado introduces clustered objects, which allow multiple component objects to appear like a single object. K42 additionally allows hot-swapping of objects, i.e. to change implementations at runtime to better suit the current needs. Clustered objects are useful to replicate or migrate objects transparently for the client that uses the object. We did not require such a flexible abstraction for the changes to L4's kernel objects we made. However, although not explicitly designed as a clustered object, our abstraction of a task address space is comparable: While the task running within its task address space has the illusion of a single address space, different address spaces are used per node so that address space management information (e.g. page tables) is

replicated. These per-node address spaces are created and populated on demand. Disco [10] chooses a different approach. The authors argue that modifying existing operating systems to better support multiprocessor architectures (including, but not limited to NUMA machines) is a difficult and resource-intensive task. Instead, they introduce an additional layer between hardware and operating system, which acts like a virtual machine monitor, but with the goal to hide the hardware specifics (such as the non-uniform memory access latencies) from the guest operating systems. Multiple instances of unmodified (and non-optimized) operating systems can run on top on a single, scalable computer. Disco also implements page replication and migration to provide local memory to the virtual machines where possible. The guest operating systems running on top thus do not need to be aware of the NUMA characteristics of the underlying hardware. Cellular Disco [16] extends Disco's approach by turning a large-scale shared-memory multiprocessor into a virtual cluster, consisting of a number of different "cells". It allows for fault containment, i.e. faults in one cell do only affect virtual machines running in that cell, while still preserving the benefits of shared-memory multiprocessors by implementing dynamic resource sharing. Both for Disco and Cellular Disco, the virtual machine monitor introduced to abstract the hardware is comparable to a microkernel, as it is intended to be kept small, and its main purpose is to abstract the hardware. However, the (Cellular)Disco hypervisor is not required to be policy free. For example, Cellular Disco implements two separate CPU load-balancing policies and a gang scheduler.

VMWare's ESX Server is also NUMA-aware [41]: Each virtual machine running on top is assigned a home node, and the virtual machine is only scheduled on CPUs on this node. The hypervisor periodically checks load distribution and migrates virtual machines between nodes if appropriate. The virtual machine's memory is transparently migrated to the new node to avoid accesses to remote memory. Memory sharing between virtual machines is also realized on a per-node basis, again eliminating the need for remote accesses. Additionally, memory and processor utilization can also be controlled manually.

## 2.3 Synchronization

The performance of synchronization mechanisms is crucial for the overall system performance. It is therefore not surprising that synchronization mechanisms were and still are a popular research area. The authors of [11] compared remote invocation (i.e. message passing) with direct access to remote memory. They conclude that the choice between these two alternatives heavily depends on architectural features, mainly the costs for remote invocation, the costs for atomic operations (required for synchronization), and the ratio of remote to local memory access time. It is also influenced by cache characteristics. The authors argue that for every machine there exists a break-even point regarding the length of an operation above which remote invocation is favorable.

The microkernel-based *Hurricane* operating system combines several locking techniques to improve performance and scalability [38]. The authors implemented a hybrid approach, using coarse-grained locks when held only for a short period of time and fine-grained locks to protect data for longer periods of time. They used

15

distributed locks to allow processors to spin locally when waiting for a lock, thus reducing traffic on the inter-connection network. Hierarchical clustering [39] was used to allow for replication and migration of system data structures. Hierarchical clustering is a technique that partitions a multiprocessor system into clusters, each of which runs an independent copy of the microkernel. Data is replicated to clusters where possible.

MCS locks are a scalable implementation of spin locks, with a constant (i.e. independent of the number of CPUs competing for the lock) number of remote accesses per lock acquisition [31].

Uhlig invented dynamic locks [36, 37], allowing the lock granularity to be adjusted at runtime, depending on access and sharing patterns of the protected objects.

## CHAPTER 3

Design

Our design decisions are driven by two main requirements: preserving parallelism and locality of accesses. Preserving parallelism means that parallel, independent request must be handled in parallel by the operating system. This leads to better scalability, which is a general requirement for all multiprocessor systems. In this context, scalability means that system performance increases (optimally linear) with the number of CPUs in the system. Locality is of particular relevance on NUMA machines, meaning that data should be kept in local memory of the accessing node wherever possible.

For the sake of the following discussion, we define the abstract term of an *object*, which can refer to concrete data objects such as page tables or thread control blocks, but also to more abstract objects such as address spaces or threads. There exist several possibilities to satisfy the requirements for parallelism and locality, with none of them being perfect for all cases. Instead, it heavily depends on the access and sharing patterns of an object to decide which one to choose. The following paragraph discusses possible solutions to allow for preserving of parallelism and/or improving locality:

Replication of objects: Instead of having only a single instance of an object, one or more replicas are created. This has two advantages: First, contention can be reduced or avoided, thus preserving parallelism. Second, the replicas can be placed in local memory of all accessing nodes, making all accesses to the object local accesses. However, replication comes at some cost: If the replicated object is modified, all copies must be kept consistent by propagating the changes to all replicas. This makes replication feasible only for objects with a high read-to-write ratio, i.e. objects that are much more often read than written.

**Migration of objects:** In case of an object with a high number of write accesses, the overhead for synchronization of replicas is too high. In that case, instead of replicating the object, it can be a better choice to migrate it to the accessing node. Of course, migration also comes at some cost: The object has to be

18 CHAPTER 3. DESIGN

copied to the destination node's memory, the memory on the source node has to be freed, and references to the object might need to be updated. Furthermore, migration only makes sense if the object is accessed mainly by a single node. In case of multiple nodes accessing an object in parallel, pingpongeffects (i.e. the object being migrated between nodes all the time) must be avoided. In contrast to replication, migration only improves locality, but not scalability.

Pinning of data objects: If an object cannot be replicated because of frequent write accesses and cannot be migrated because it is accessed by different nodes simultaneously, the only remaining possibility is to keep a single instance of the object in local memory of one node. This solution of course neither preserves parallelism nor does it favor local accesses over remote accesses (the object is in remote memory for all but one node). It can, however, be useful if an object is known to be accessed mostly by a single node. Pinning thus can avoid accidental migration or unnecessary replication of such an object.

When an object can be accessed from different CPUs simultaneously, accesses must be serialized to avoid race conditions. Serialization can either be performed lock-based or message-based. The decision which is favorable depends on the access and sharing patterns of the data object as well as on the characteristics of the underlying hardware, mainly the costs of remote memory accesses and the costs of inter processor interrupts (IPIs). Uhlig suggests dynamic locking to adapt lock implementation and granularity at runtime, depending on the degree of sharing [36]. Yet, dynamic locks don't take hardware characteristics into account, which also affect the choice for an "optimal" synchronization mechanism. For example, on a machine with low IPI-costs, message based synchronization might be favorable over lock base synchronization, especially if the costs for remote accesses are high.

### 3.1 System Architecture Overview

A microkernel provides only a minimal abstraction of the underlying hardware and does not implement operating system services like pagers, file system handling, and so on. These services must be implemented as separate tasks, running at user-level. The implementation of these services must follow the afore mentioned principles: Preserving parallelism and locality of accesses. Therefore, each service must offer at least one thread per CPU that can handle incoming service requests. Each of these threads must work on local data where possible. In this way, parallelism is preserved, as independent, parallel requests to the same server can be handled in parallel. Furthermore, the amount of cross-CPU communication (which is far more expensive than communication between threads on the same CPU) is minimized, because a thread requesting a service can always call a server thread on the same CPU. Figure 3.1 shows a simple, microkernel-based operating system, running on a system with two nodes (and one CPU per node). In this example, two servers run on top of the microkernel: a memory server and a pager. Each of these servers consists of two threads, i.e. one per CPU. On top of the servers run different applications, both single-threaded applications (assigned to exactly one node at a time) and multi-threaded applications (that might be active on both nodes simultaneously). We now have a look at the required operating system servers.

Figure 3.1: Architecture of a microkernel-based operating system for NUMA hardware.

#### 3.1.1 Pager/Memory Manager

A pager and a memory manager are needed to satisfy an application's demand for memory. If a paged thread touches a region of virtual memory that is currently not mapped to physical memory, the pager must handle the resulting page fault in cooperation with the memory manager, most likely by mapping some memory into the thread's address space (if the thread performed an illegal access, the pager might initiate to kill that thread instead). In our design, a pager is responsible for paging all threads that run on the same CPU. If a thread migrates to another CPU, one pager must hand the thread over to the other. While this handoff itself is straightforward, there remains the open question of how the new pager gets the required information about the migrated thread's address space layout, i.e. which pages are currently mapped in, etc. If all pager threads run within the same address space (as shown in Figure 3.1), this is not a problem - in that case, management information for all address spaces is visible to all pager threads. However, there are some good reasons to place each pager thread into its own address space, which we will discuss later. In that case, data from one pager is not easily accessible by other pagers, but must instead be shared explicitly. It is either possible to copy the entire management information upon migration, or to query the originating pager on demand, i.e. when a page fault occurs. For both solutions, one has the choice between using IPC or shared memory. We discuss thread migration in more detail in Section 4.2.4.

20 CHAPTER 3. DESIGN

#### 3.1.2 Load Balancer

Load balancing is an important task in multiprocessor systems. If the load on one CPU becomes too high, threads or processes must be migrated to other CPUs with less load. For NUMA systems, CPUs in the system should not be treated equally when considering load balancing: It is generally favorable to migrate threads or tasks to another processor of the same node than to an arbitrary processor in the system, at least if the thread/task has large parts of its working set in local memory of the current node. To be able to model the system topology for load balancing decisions, we propose a design with one (potentially multi-threaded) load balancer per node, which is responsible only for surveying the load within its own node and to migrate threads between CPUs of its node. When the overall load of the node is too high, it can notify a master load balancer which keeps track of the load distribution of the entire system. This solution is similar to the scheduling domains of recent Linux versions, which are also used to model the system's topology to be able to take better scheduling/balancing decisions [6].

#### 3.2 Node-Local User-Level Data

Parallel applications consisting of multiple threads are a likely workload on a NUMA machine. With only a small number of CPUs per node, the application's threads must be distributed amongst nodes to execute the application in parallel. In that case, the application's address space is active on different nodes simultaneously. This scenario raises a number of questions to deal with:

- Where to place page management information both for the microkernel and for the user-level pagers? With L4's current implementation of address spaces, the layout of an address space is represented with a single kernel page table hierarchy which lies in physical memory of a specific node. If the corresponding address space is active on multiple nodes in parallel, page table accesses are remote accesses for all but one node, which contradicts the principle of locality. A similar problem arises for the address space information the userlevel pagers have to keep.

- How to provide node-local data for applications? An application should be given the possibility to allocate data on and migrate data to a specific node, either by offering an API that allows the application to influence memory allocation or by an OS subsystem that performs automated allocation, replication, and migration of memory.

In the following, we present different approaches to tackle these problems.

#### 3.2.1 A First Approach

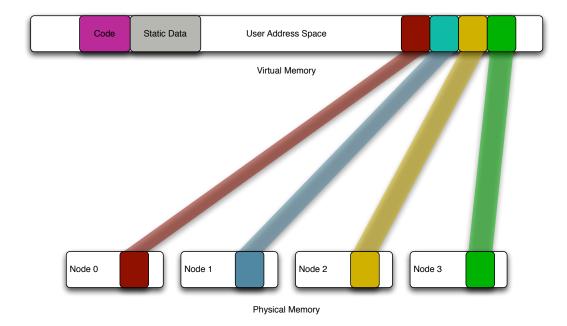

An application can create a designated region within its virtual address space which is partitioned into different areas, each backed by physical memory of a specific node, as depicted in Figure 3.2. Those areas can then be used as a "pool" of nodelocal data. All data that is important only or mostly on a specific node can be

Figure 3.2: Pools of memory from each node can be mapped to different locations within the application's virtual address space, allowing for dynamic allocation of node-local memory.

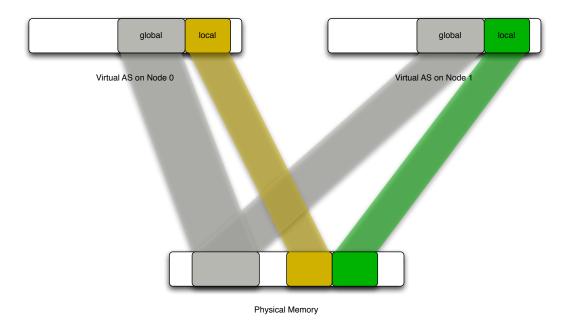

placed inside the corresponding node pool. Thread stacks can be allocated in the pool of the node the corresponding thread belongs to. However, this approach lacks some flexibility: Replication of the application's code is difficult: Unless relative addressing is used, code is expected at a specific virtual address and cannot easily be copied to different locations. To do this, relocation would have to be performed. More generally spoken, it is not possible to map the same range of virtual addresses to different physical addresses on every node, which is a fundamental requirement for dynamic page replication. Any form of node-local data thus requires indirection. A more flexible solution is desirable, which allows an address space layout as shown in Figure 3.3: While the gray, global region of the virtual address space is backed by the same physical memory on every node, the local regions are mapped to different physical memory on every node.

Additionally, while this first approach does not require any changes to L4 or the way L4's address spaces are used, it also leaves the question how to handle address space management information open.

#### 3.2.2 In-Kernel Replication of Page Tables

Instead of having a single page table hierarchy per address space, L4 could be modified to have a page table hierarchy for every node (or even for every CPU) in the system. These hierarchies can be placed in local memory of the node they belong to, thus improving data locality. Additionally, this approach allows for a flexible form of node-local data: As the replicated page table hierarchies need not necessarily be consistent, different mappings can be established for different nodes, allowing the same region of the virtual address space to be mapped to different physical locations, depending on the node on which the access is performed. This

22 CHAPTER 3. DESIGN

Figure 3.3: The local region of the virtual address space is mapped to different physical addresses on every node.

greatly simplifies code replication, because code can always be mapped to the "correct" virtual addresses, but backed by different physical memory on every node. As the kernel cannot know whether a newly established mapping shall be made global or local, changes to the API are necessary. With an additional bit in each map or grant item, the user can specify whether a mapping shall be made local or global, i.e. equally visible on all nodes. Global mappings must be propagated to all other page table replicas, i.e. synchronization must be performed. The choice for the right synchronization primitive is not a trivial one: If lock-based synchronization is used, one has the choice between different locking granularities (the possibilities range from locking of an entire page table hierarchy to locking of single entries) and lock implementations. Additionally, lock-based synchronization requires accessing remote memory to perform modifications. In contrast, message-based synchronization avoids or at least reduces both the need for locking and accesses to remote memory, but one has to take into account the costs for notifications across CPUs, i.e. inter processor interrupts. Hence, the decision which synchronization primitive is favorable does not only depend on the access and sharing patterns of the page table hierarchies, but is also influenced by the costs for IPIs and for remote accesses [11]. While locking granularity can be adjusted at runtime, depending on the access and sharing patterns [36], it is difficult to also take hardware characteristics into account. Manually modifying the kernel to suit the hardware platform it is designated to run on contradicts the idea of a minimal, flexibly useable microkernel. Additionally, propagating a newly established mapping to all page table replicas might be unnecessary, as it might never be accessed on all nodes. Thus, a lazy approach that performs synchronization only when and where necessary is preferable. In case of address space organization, there exists an alternative that avoids eager, explicit in-kernel synchronization of page table replicas, while still

providing the desired flexibility. We present this approach in the next section.

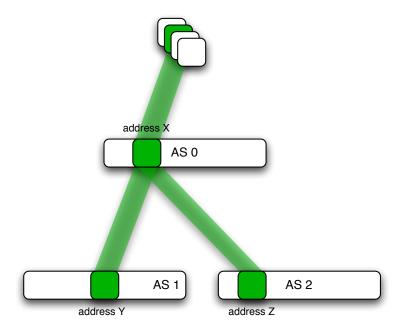

#### 3.2.3 Using Different Address Spaces

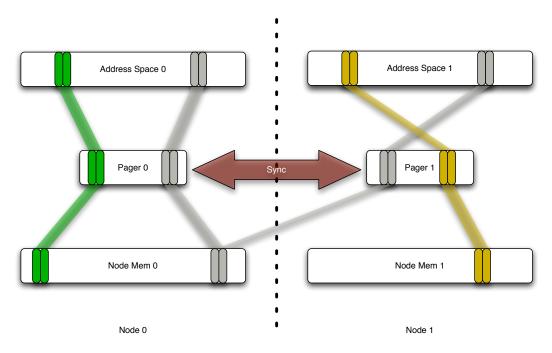

The approach we suggest can be realized entirely at user-level, without requiring changes to the kernel or the kernel API. Instead of explicitly replicating the page table hierarchy of an address space in the kernel, we use different, unmodified address spaces for each node. From the viewpoint of the kernel, these different address spaces are completely unrelated, the kernel thus does not perform any form of synchronization between them. Instead, synchronization is performed entirely at user-level between the pagers of the address spaces. Figure 3.4 shows an example with an application running on two nodes (each with one CPU). A different address space is used on each node, and each is managed by its own pager thread. Synchronization of the two address spaces is the pagers' task. As Figure 3.4 also shows, this approach allows both for node-local mappings (green) and global mappings (gray).

Figure 3.4: Per-node address spaces allow both for global and node-local mappings and avoid introducing an additional synchronization primitive in the microkernel.

The required synchronization between the pagers affects the way mappings are established and removed. While the pagers perform explicit synchronization at user-level, the kernel page tables are implicitly synchronized. In the following, we discuss how the usage of per-node address spaces affects both establishment and revocation of mappings.

24 CHAPTER 3. DESIGN

#### **Establishing Mappings**

Establishing a node-local mapping is straightforward: If a pager receives a page fault IPC on a virtual address where a node-local mapping is expected (e.g. an address where the application code lies), it can simply reply with a map item to map the correct physical memory. No form of synchronization is required. Establishing a global mapping is a more complex operation. When a pager is notified of a page fault on a virtual address that shall be global and for which no valid mapping exists yet, it also replies with the correct map item, but this time, the other pagers must be made aware of that newly established mapping. As for the in-kernel approach, there exists a multitude of synchronization possibilities between the pagers, which we discuss later. When the virtual address where the new mapping was established is accessed on another node, there will also occur a page fault because the kernel page tables of the address space on that node are not yet updated: From the viewpoint of the kernel, the different address spaces are completely unrelated. it does therefore not perform any form of synchronization. However, because of the synchronization between the pagers, this pager now knows what physical memory must be mapped to that address and can reply with the correct map item. Every pager must therefore be able to access and map all physical memory.

In conclusion, arbitrary synchronization strategies can be applied between the user-level pagers, while the synchronization of kernel page tables for the different address spaces works implicitly and lazily, as new global mappings are established on a page fault basis.

#### **Revoking Mappings**

In this section, when we talk about revocation of a mapping, this can mean both that the mapping is completely removed (i.e. the corresponding page(s) are unmapped) or that the access rights of the mapping are restricted (e.g. from readwrite to read-only). Revocation of global mappings is a more complex task than establishment of global mappings, as this time, the in-kernel page tables cannot be updated lazily. If a global mapping is revoked, this change must be made visible to all affected address spaces immediately. Otherwise, it can happen that the mapping can still be accessed in another address space. The recursive nature of L4's map and unmap operations allows for different approaches to tackle this problem. If a thread calls the *unmap* system call on a page within its address space, the page is unmapped from all address spaces to which it was mapped onward from the current address space. In Figure 3.4, if pager 0 would call *unmap* on one of the gray pages, this paged would be unmapped only from address space 0. To unmap a page from all affected address spaces, there exist various approaches:

1. The originating pager notifies all other pagers to call *unmap* for themselves. An IPC-based protocol can be used for this. The disadvantage of this solution is that the number of required IPCs scales linearly with the number of remote pagers that must be notified. This number is influenced by the number of tasks to which a page was mapped and by the parallelism of these tasks, i.e. on how many nodes a task is active simultaneously. The total number of nodes in the system is an upper bound for the required number of cross-CPU notifications.

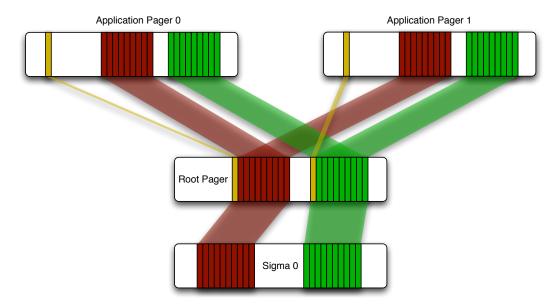

- 2. A root pager is used that donates memory to and revokes memory from the pagers running on top. In that case, the originating pager can call the root pager to perform the *unmap*, and the corresponding page will be unmapped from all address spaces it was mapped to, including the address spaces of the pagers. For example, if the root pager in Figure 3.5 calls *unmap* for one of the gray pages, this page will be removed from the application's address spaces (i.e. address space 0 and address space 1), but also from the address spaces of pager 0 and pager 1. In contrast to solution 1, only a single IPC call to the root pager is required. However, revoking the mapping also from the pagers' address spaces is an unwanted behavior.

- 3. The *unmap* system call is modified to allow a "directed unmap", i.e. allowing a pager to directly unmap memory from another but its own address space. Such a modification would impose great security problems, as a pager must not be permitted to unmap arbitrary pages it is not responsible for. One would have to introduce an additional security model into the kernel, e.g. by grouping pagers together that are allowed to unmap each other's memory. Even if this was done, there remain open questions. For example, a pager that wants to unmap a page handled by another pager would have to know at which virtual address this page is mapped in the other pager's address space. To revoke a global mapping from n address spaces, n calls to the directed unmap system call are needed, thus the costs for this solution also are in O(n).

From these three possibilities, we favor the first, but the second can be an alternative if the overhead of the first turns out to be too high. In Chapter 5, we discuss the expected costs and potential optimizations.

Figure 3.5: Recursive mapping hierarchy with a root pager donating memory to all other pagers.

26 CHAPTER 3. DESIGN

#### Synchronization between Pagers

Any changes made to a global mapping (including the creation of a new global mapping) by one pager must become visible in the other pager's data structures, too. The easiest solution for this is to let all pagers work on the same data structures by mapping them into every pager's address space. This, however, does not only require locking, but also contradicts the principle of locality, as the management information would be in remote memory for all pagers except for one. Additionally, a single instance of management information makes it difficult to store information about node-local mappings. As the pagers need the management information simultaneously and frequently, migration also is not an option. We therefore decided to replicate the information, so that each pager can work on its own data. Yet, the problem how these replicas are synchronized remains. As we stated in Section 3.2.3, in case of revocation of a mapping, changes must be propagated to other pagers eagerly. This requires an eager, push-based approach, i.e. the originating pager must notify all other pagers to revoke the mapping and to update their management information. Therefore, an IPC-based solution is favorable: The originating pager calls an appropriate function of the other pagers, triggering remote revocation of the mapping. In the opposite case, if a new, global mapping is established by one pager, other pagers will still suffer a page fault on the corresponding virtual addresses afterwards, allowing synchronization of pager management information to be performed lazily. Alternatively, the originating pager (i.e. the one that established the new mapping) can also eagerly update the other pagers' data structures. The disadvantage of the eager approach is that it might cause unnecessary updates, in case the newly established mapping will not be accessed on all nodes. With a lazy approach, a pager receiving a page fault at a virtual address that is not explicitly marked as local must query all other pagers to find out if there already exists a valid, global mapping. This solution scales bad, as the costs grew linearly with the number of pagers (and thus CPUs or nodes) in the system. We decided to use a combination of eager and lazy propagation to avoid the necessity of querying all other pagers: One of the pagers is designated as a "master pager". Whenever one of the other pagers establishes a new mapping, it eagerly notifies the master pager of the changes. Upon a page fault on a global mapping, a pager now only needs to query the master pager to find if there already exists a valid mapping. To avoid that the master pager becomes a scalability bottleneck, a different master pager can be used for every task, for example the pager on the node where the task was created on. This reduces contention on a single pager. Both the update of the master pager's management information and querying the master pager to find valid global mappings can be done via IPC or via shared memory. In the latter case, locks are required to ensure consistency. The same arguments as for the in-kernel solution influence the choice for a synchronization primitive: Access and sharing patterns as well as latencies of remote accesses. With our user-level based solution however, the kernel is kept free of such a primitive and remains flexible, while user-level servers can be adapted to better suit a specific hardware, if necessary.

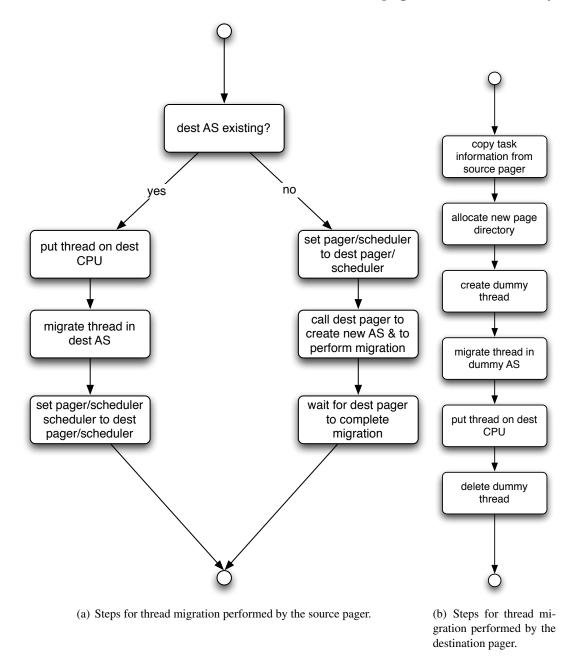

#### **Thread Migration**

Migrating a thread to another CPU on another node now becomes more complicated, as it is no longer sufficient to only put the thread on the new CPU with an appropriate system call. Instead, it must also be migrated into the corresponding address space on the target node. If no address space exists yet, one must be created. The pagers therefore must be aware of which address spaces belong to the same task. We discuss implementation-depended problems of thread migrations in Section 4.2.4.

27

# 3.3 Kernel Objects

For all kernel objects, such as page tables and thread control blocks (TCBs), it must be decided how locality can be improved, and how parallelism can be preserved. Because L4 is a microkernel, the number of objects we need to revise is small. We identified page tables, thread control blocks, and the entries of the mapping database.

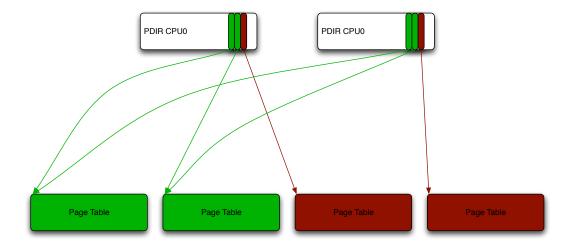

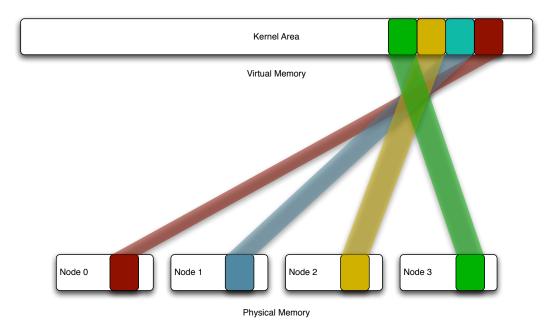

# 3.3.1 Page Tables

Page tables are potential candidates for replication. Write accesses are rare compared to read accesses and normally only affect a small part of the table (i.e. a few entries). Dynamic locks as suggested by Uhlig [36] could be used to serialize accesses to page tables, with the lock granularity being adjusted depending on the access pattern of a page table (which depends on the number of nodes on which the address space is active). Additionally, L4 already uses different page directories for each CPU to allow for CPU-local kernel data, as shown in Figure 3.6: Most entries of the per-CPU page directories point to the same, shared subtables (depicted in green), but some entries point to CPU-local subtables (depicted in red). The virtual addresses that are occupied by these "CPU-local" entries are mapped to different physical addresses on every CPU. This allows for CPU-local data without having to use indirection. L4 uses this concept for some statically defined in-kernel data, e.g. the thread control block of the idle thread. However, the concept currently does not support dynamic allocation of CPU-local memory, nor is it exported to user-level applications. Yet, it could be further enhanced in that the entire page table hierarchy is replicated instead of only the CPU-local tables. In that case, each page table hierarchy can be placed in node memory of the node the page tables belong to, thus making all page table accesses local. This leads to the problems we described in Section 3.2.2: Synchronization of page tables must be performed across node boundaries, requiring a synchronization primitive in the kernel that also depends on remote memory latencies. However, as described in Section 3.2.3, we use per-node address spaces instead of a single, node-spanning address space for each application. Therefore, we decided to optimize our solution for that case and not for the case of address spaces spanning across multiple nodes. Each address space is assigned a "home node", on which all shared page tables are allocated on, while "CPU-local" tables are allocated on the node of the corresponding CPU. With this model, an address space can still become active on every node (and on different 28 CHAPTER 3. DESIGN

Figure 3.6: Exemplary page table hierarchy for a system with two CPUs. The green entries in both page directories point to the same page tables and thus to non-CPU-local data. The red entries point to different page tables. The corresponding virtual addresses can thus be mapped to different physical addresses on each CPU.

nodes simultaneously), but it is favorable that it is active only on its home node. In that case, the entire page table hierarchy will be placed in node-local memory, and no in-kernel synchronization of page tables must be performed across node boundaries. It us up to the user-level to ensure that address spaces are active on exactly one node.

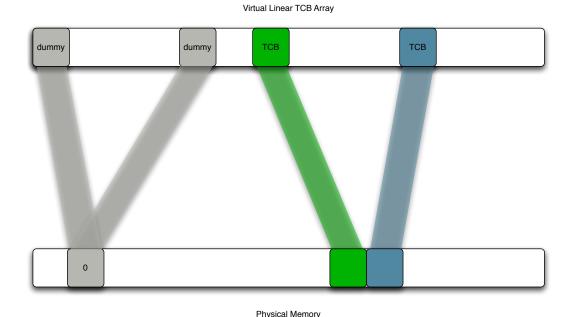

#### 3.3.2 Thread Control Blocks

A thread's TCB is used to store relevant information for that thread, including its state and its kernel stack. As a thread is always assigned to a single CPU (and thus to a single node), it seems to be a good idea to always keep a thread's TCB on the thread's node and migrate it whenever the corresponding thread is migrated. However, a TCB is not only accessed by its own thread, but also by other threads. For example, if a thread wants to send an IPC to another thread, it has to check the destination thread's state and thus its TCB. To avoid remote accesses in that case, every TCB would have to be replicated to every node's memory. We decided not to do this, but to migrate TCBs instead for two reasons: First, we consider the overhead for synchronization of the replicas too high - a thread's TCB is written on every IPC operation. Second, we favor IPC between threads on the same CPU over cross-CPU IPC, as the latter requires inter-processor interrupts and thus is more costly. If both threads run on the same CPU, accesses to the sender's and receiver's TCB are both local accesses. In case of a cross-CPU IPC, the additional penalty caused be accessing a TCB in remote memory is not significant compared to the overall costs for a cross-CPU IPC.

L4 currently addresses TCBs via a virtual linear array with a fixed size. A thread's ID is used to calculate the virtual address of its TCB. No memory is mapped into the virtual array initially. On a read-fault, a zero-filled "dummy TCB" is mapped in. On a write fault, memory for a new TCB is allocated and mapped at

the desired location. Figure 3.7 shows an example. Theoretically, migration of a

Figure 3.7: Virtual linear TCB array. The two dummy TCBs (gray) are both mapped to a zero-filled page. "Real" TCBs (green and blue) are mapped to different pages of physical memory, allocated on demand. In this picture, the mapping granularity is fine enough to allow for mapping on a per-TCB basis.

TCB is straightforward: Allocating a new physical page for it, copying the old page to the new page, and finally changing the mapping to the new physical address. Furthermore, the affected entries must be flushed from all CPUs' TLBs. However, a problem arises when more than one TCB occupies a single page (which is the case for the IA32 kernel): As mappings can only be changed on a per-page basis, all TCBs on a page have to be migrated. However, it cannot be ensured that the corresponding threads run on the same node. By migrating one TCB from remote to local memory, another TCB lying in the same page might be migrated away from its "home node". A more fine-grained solution is required, which allows for migration of one TCB without side effects for other TCBs. One approach is to expand the size of a TCB so that only a single TCB occupies a page. This either requires to reduce the maximum number of allowed threads or to increase the size of the virtual TCB array. The former approach might lead to a system running out of thread IDs too early, the latter approach is a problem on 32 Bit architectures, where the kernel area currently is limited to a size of 1 GB. Furthermore, also physical memory is wasted because it is questionable if there are any benefits from larger TCBs, even though the additional space could be used for the thread's kernel stack. L4 does not perform any recursion in the kernel, and in-kernel function call chains are short, thus there is no need for larger kernel stacks. Additionally, larger TCBs lead to a higher occupation of the TLB, leading to a higher TLB-footprint of the kernel, with negative effects on the overall system performance, at least when the number of existing threads is high.

30 CHAPTER 3. DESIGN

Another approach is to discard the scheme of direct addressed TCBs and to use indirect addressing instead. A thread's ID can be used to index into an array of pointers to TCBs. When migrating a TCB, new memory is allocated from the destination node's memory pool, the TCB is copied, and the pointer is changed to point to the new location. The memory on the source node can then be freed. This approach introduces an additional level of indirection, but provides the desired flexibility without limiting the number of threads or wasting both virtual and physical memory. There are two problems one has to take care of with this approach: First, when a thread is going to be migrated, it must be ensured that its TCB is not accessed by any other thread (running on a different CPU) in this moment. Read-Copy Update (RCU) [28-30] can be used to ensure that no other threads are currently accessing the TCB. Second, there might be threads which are currently not active but still have direct references to their own or another TCB on their kernel stack. As threads can be sleeping for an arbitrary amount of time, one cannot make any assumptions if and how long such references exist. Finding and updating all existing old references to a TCB when this TCB is migrated is not possible, as those references are stored on a thread's kernel stack, the layout of which is not known. Instead, a thread has to reload all TCB references it keeps when it is reactivated. This requires to identify all points within the kernel code at which stale TCB pointers might be accessed, which is not a trivial task. The pointer array itself is a candidate for replication, as write accesses are only required in case of a thread migration. Additionally, as a thread migration is always performed by the source CPU of the to-be-migrated thread, concurrent modifications of the same TCB pointer can not occur. Yet, it must be ensured that a TCB pointer is not accessed and dereferenced while migration is in progress.

Mainly due to time constraints, we decided to favor the first approach for our implementation.

#### User-Level Thread Control Blocks

Parts of a thread's TCB are mapped into the user area instead of the kernel area. These so-called UTCBs contain information that can be exposed to user applications without affecting security. In particular, a thread's message and buffer registers are part of its UTCB. As for kernel TCBs, there also arises the question where to place a thread's UTCB, and how to migrate it when the thread migrates. In contrast to TCBs, however, increasing the size of a UTCB to allow for migration of single UTCBs is even a bigger problem: For example, on IA32, a UTCB is only 512 bytes in size. Increasing the size to 4 kilobytes (i.e. eight times the size it actually requires) is not reasonable. On the other hand, changing the addressing scheme of UTCBs is even more complicated as it is for TCBs: The address of a UTCB is used as the thread's local ID (i.e. an ID that is only unique within its address space), and the kernel API specification ensures that the location of a thread's UTCB will not change during the lifetime of that thread [21]. If indirect addressing was used, this assertion would no longer hold true, causing problems with applications that might rely on that assumption.

However, the design decisions we made for the organization of address spaces, i.e. using different address spaces on each node, also offer a simple solution to this

3.3. KERNEL OBJECTS 31

problem, allowing for migration of UTCBs without indirection and without increasing their size. The reason why this is possible is that all threads within an address space run on the same node. Therefore, even if numerous UTCBs occupy a single hardware page, all of them can be backed with memory from the local node. If a thread is going to be migrated to another node, this implies migrating it into another address space. Only two conditions must hold true to allow for migration of a thread into another space: First, there must not exist a thread with the same local thread ID (i.e. UTCB location) in the target address space. Second, the UTCB area in the target address space must occupy the same region as it does in the source address space, so that the migrated thread's UTCB can be placed at the same address as it has been before.

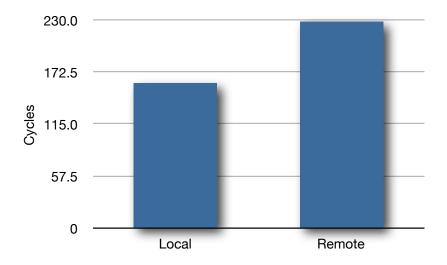

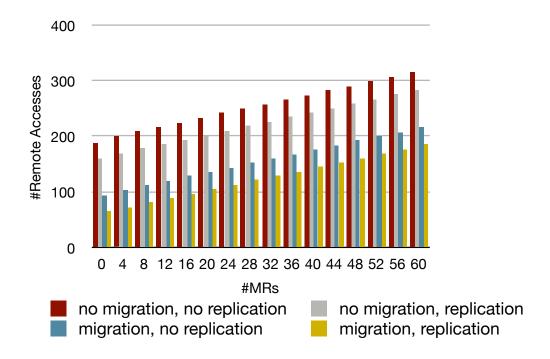

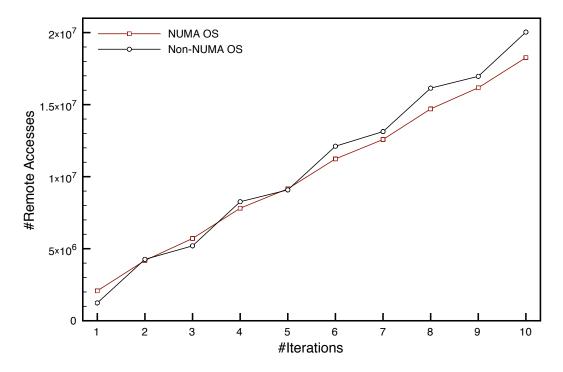

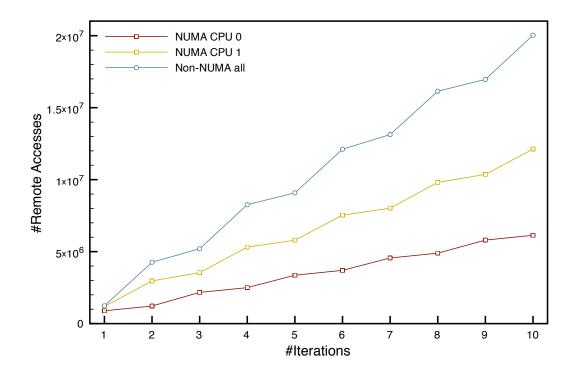

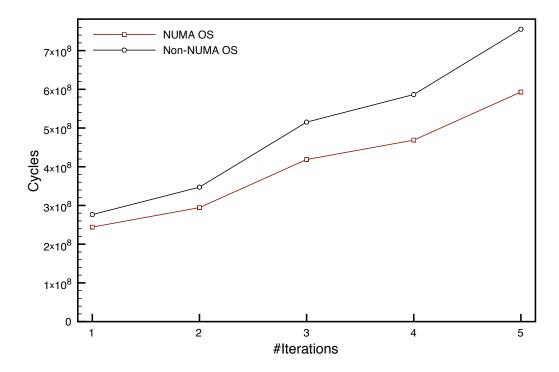

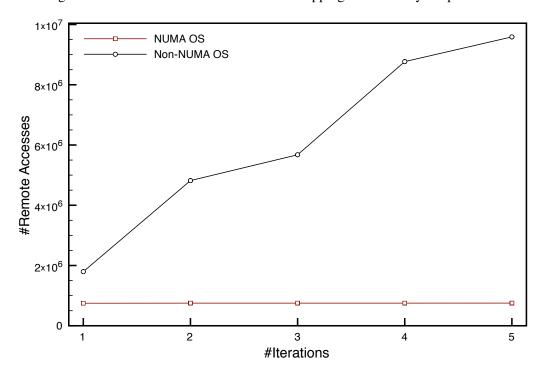

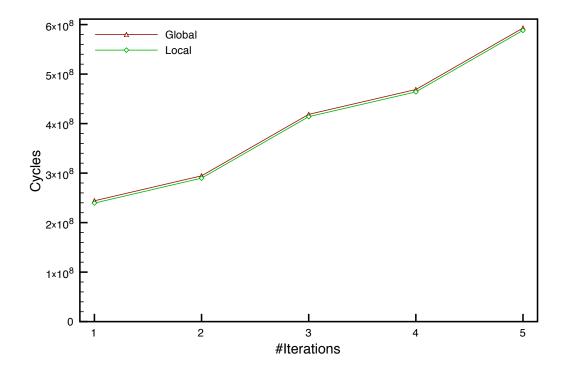

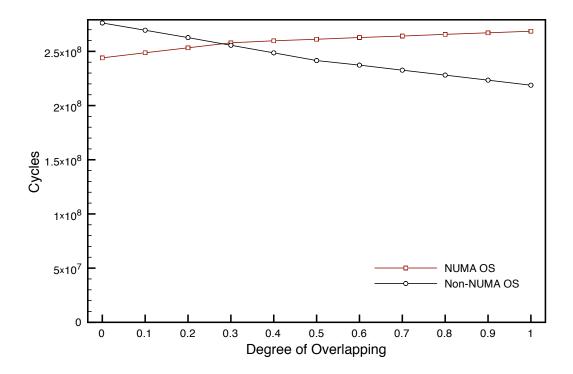

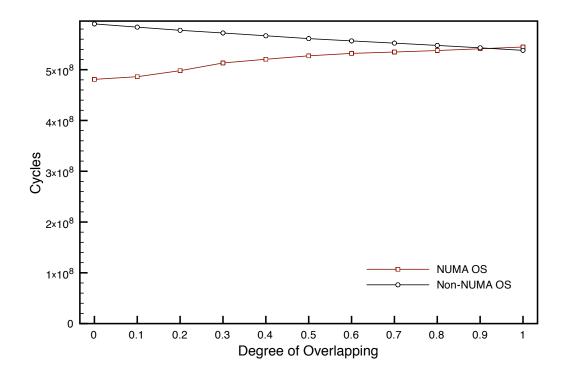

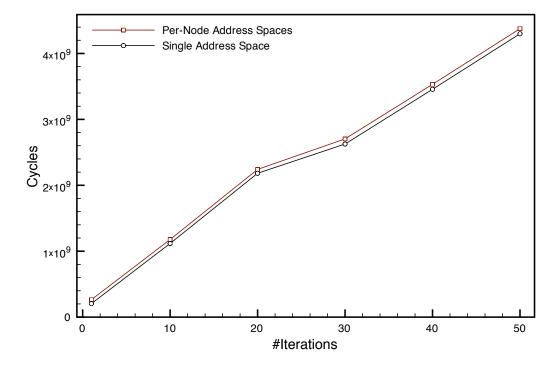

## 3.3.3 Mapping Database