# Applying Modern Processor Features to L4 Microkernels

Bachelor's Thesis

submitted by

cand. inform. Martin Ludwig Gurres

to the KIT Department of Informatics

Reviewer:

Prof. Dr. Frank Bellosa

Second Reviewer:

Prof. Dr. Wolfgang Karl

Advisor:

Dipl.-Inform. Thorsten Gröniger

17. Juni 2025 – 17. Oktober 2025

I hereby declare that the work presented in this thesis is entirely my own and that I did not use any source or auxiliary means other than these referenced. This thesis was carried out in accordance with the Rules for Safeguarding Good Scientific Practice at Karlsruhe Institute of Technology (KIT).

Karlsruhe, October 17, 2025

# Abstract

Optimizing time performance of interprocess communication (IPC) facilities on microkernels ( $\mu$ kernels), kernels with minimal functionality, is essential to ensuring competitiveness with monolithic kernels like Linux. With the emergence of recent work like *SkyBridge*, modern processor features have become key research subjects to develop new IPC libraries with that surpass native implementations and therefore improve  $\mu$ kernels. seL4 is a modern representative of  $\mu$ kernels, which we use as a design and implementation platform for user-interrupt (UINTR) support, Intel’s recently-introduced extension to send and receive (inter-processor) interrupts directly from user-space. In addition to UINTR we also implement support for the new user-wait extension, e.g. timed pause TPAUSE, and design an IPC library to make use of both of these new features on seL4. We find that our new IPC library—uIntercom (uIcom)—provides 1.1–5.5 $\times$  better time performance than either existing seL4 IPC facilities in the cross-core case, while potentially indicating better power efficiency in some metrics.

# Contents

|                                                            |          |

|------------------------------------------------------------|----------|

| <b>Abstract</b>                                            | <b>v</b> |

| <b>Contents</b>                                            | <b>1</b> |

| <b>1</b> <b>Introduction</b>                               | <b>5</b> |

| <b>2</b> <b>Background</b>                                 | <b>7</b> |

| 2.1 Microkernels . . . . .                                 | 7        |

| 2.1.1 What is a Kernel? . . . . .                          | 7        |

| 2.1.2 Micro- & Monolithic Kernels . . . . .                | 8        |

| 2.1.3 Historical and Modern L4 Microkernels . . . . .      | 8        |

| 2.2 Interprocess Communication . . . . .                   | 9        |

| 2.2.1 IPC Categories . . . . .                             | 10       |

| 2.2.2 Message Passing . . . . .                            | 10       |

| 2.2.3 Signals . . . . .                                    | 10       |

| 2.2.4 Remote Procedure Calls . . . . .                     | 11       |

| 2.3 Interrupts . . . . .                                   | 11       |

| 2.3.1 Mechanism . . . . .                                  | 11       |

| 2.3.2 Advanced Programmable Interrupt Controller . . . . . | 12       |

| 2.3.3 Exceptions . . . . .                                 | 13       |

| 2.3.4 Interrupt Handling . . . . .                         | 13       |

| 2.4 Modern Processor Features . . . . .                    | 13       |

| 2.4.1 UINTR Feature Background . . . . .                   | 14       |

| 2.4.2 Receiving User-Interrupt Notifications . . . . .     | 14       |

| 2.4.3 Sending User Interprocessor Interrupts . . . . .     | 17       |

| 2.4.4 UINTR-XState . . . . .                               | 19       |

| 2.4.5 Limitations of UINTR . . . . .                       | 20       |

| 2.4.6 User-Wait Extension . . . . .                        | 20       |

| 2.5 Introduction to seL4 . . . . .                         | 21       |

| 2.5.1 System Calls . . . . .                               | 21       |

| 2.5.2 Capabilities . . . . .                               | 22       |

|          |                                                  |           |

|----------|--------------------------------------------------|-----------|

| 2.5.3    | IPC Capabilities . . . . .                       | 25        |

| 2.5.4    | Interrupt Handling . . . . .                     | 27        |

| <b>3</b> | <b>Related Work</b>                              | <b>29</b> |

| 3.1      | User-Level-Interrupts . . . . .                  | 29        |

| 3.1.1    | Introductory Work . . . . .                      | 29        |

| 3.1.2    | Security Aspects . . . . .                       | 30        |

| 3.1.3    | Technical Analyses . . . . .                     | 30        |

| 3.2      | Applications of UINTR . . . . .                  | 31        |

| 3.2.1    | User-level Preemption with UINTR . . . . .       | 31        |

| 3.2.2    | Other Applications of UINTR . . . . .            | 33        |

| 3.3      | IPC on Microkernels . . . . .                    | 34        |

| 3.3.1    | SkyBridge . . . . .                              | 34        |

| 3.3.2    | UnderBridge . . . . .                            | 34        |

| 3.3.3    | HyBridge . . . . .                               | 35        |

| 3.3.4    | Other work . . . . .                             | 36        |

| <b>4</b> | <b>Design</b>                                    | <b>37</b> |

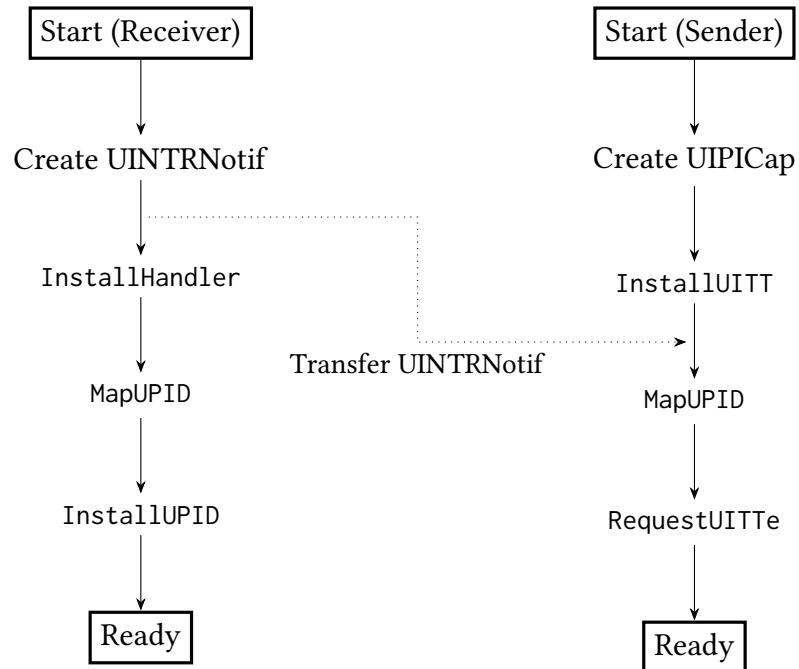

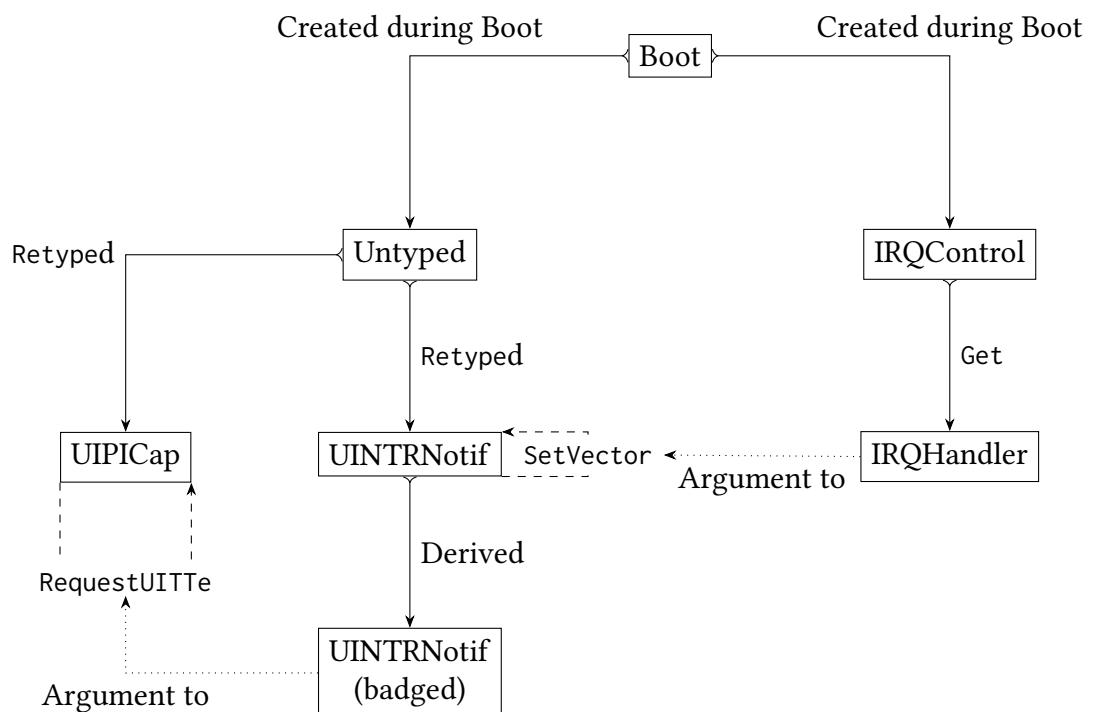

| 4.1      | Capability-based User-level Interrupts . . . . . | 37        |

| 4.1.1    | Initial Approach . . . . .                       | 37        |

| 4.1.2    | Capability-based User-level Interrupts . . . . . | 38        |

| 4.2      | IPC Library with UINTR support . . . . .         | 41        |

| 4.2.1    | Wait Types . . . . .                             | 42        |

| 4.2.2    | Signals . . . . .                                | 42        |

| 4.2.3    | Message Passing . . . . .                        | 44        |

| 4.2.4    | Remote Procedure Calls . . . . .                 | 44        |

| 4.2.5    | Final Overview . . . . .                         | 45        |

| <b>5</b> | <b>Implementation</b>                            | <b>47</b> |

| 5.1      | User-Interrupts on KVM/QEMU . . . . .            | 47        |

| 5.1.1    | CR4 and CPUID pass-through . . . . .             | 48        |

| 5.1.2    | UINTR-XState support . . . . .                   | 48        |

| 5.2      | User-Interrupts on seL4 . . . . .                | 49        |

| 5.2.1    | Additional Background . . . . .                  | 49        |

| 5.2.2    | Initial Steps and UINTR Capabilities . . . . .   | 49        |

| 5.2.3    | Issues Encountered . . . . .                     | 50        |

| 5.2.4    | Finalizing our Capabilities . . . . .            | 52        |

| 5.2.5    | Summary . . . . .                                | 52        |

| 5.3      | libUIIntercom . . . . .                          | 54        |

| 5.3.1    | More than just UINTR . . . . .                   | 54        |

| 5.3.2    | Connection Setup . . . . .                       | 54        |

|                                                           |            |

|-----------------------------------------------------------|------------|

| <i>CONTENTS</i>                                           | 3          |

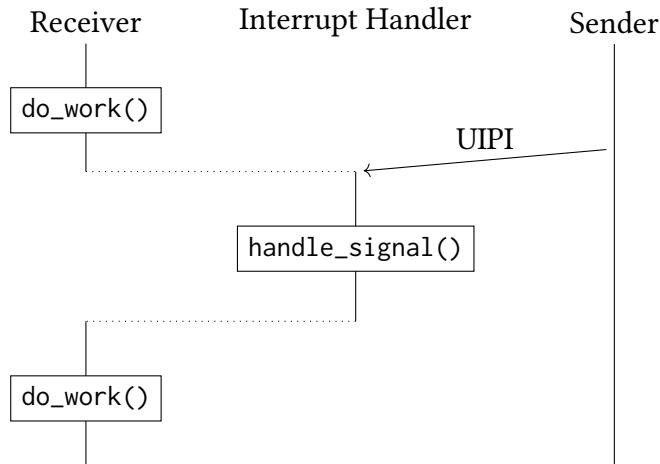

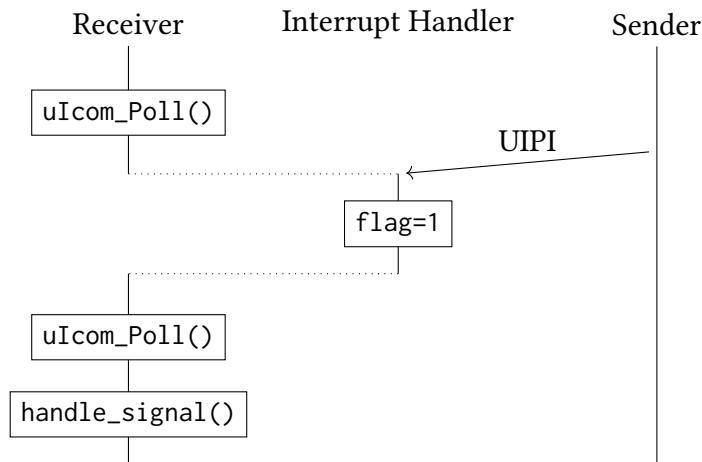

| 5.3.3    User-Interrupt and Connection Handlers . . . . . | 56         |

| 5.3.4    Sending and Receiving . . . . .                  | 56         |

| 5.3.5    Summary . . . . .                                | 60         |

| <b>6 Evaluation</b>                                       | <b>61</b>  |

| 6.1    Methodology . . . . .                              | 61         |

| 6.1.1    Measuring Time . . . . .                         | 62         |

| 6.1.2    Measuring Energy Consumption . . . . .           | 63         |

| 6.1.3    Measuring Efficiency . . . . .                   | 63         |

| 6.1.4    Further Performance Indicators . . . . .         | 64         |

| 6.2    Benchmarking . . . . .                             | 64         |

| 6.2.1    Setup . . . . .                                  | 64         |

| 6.2.2    Benchmark Design . . . . .                       | 65         |

| 6.3    Results . . . . .                                  | 66         |

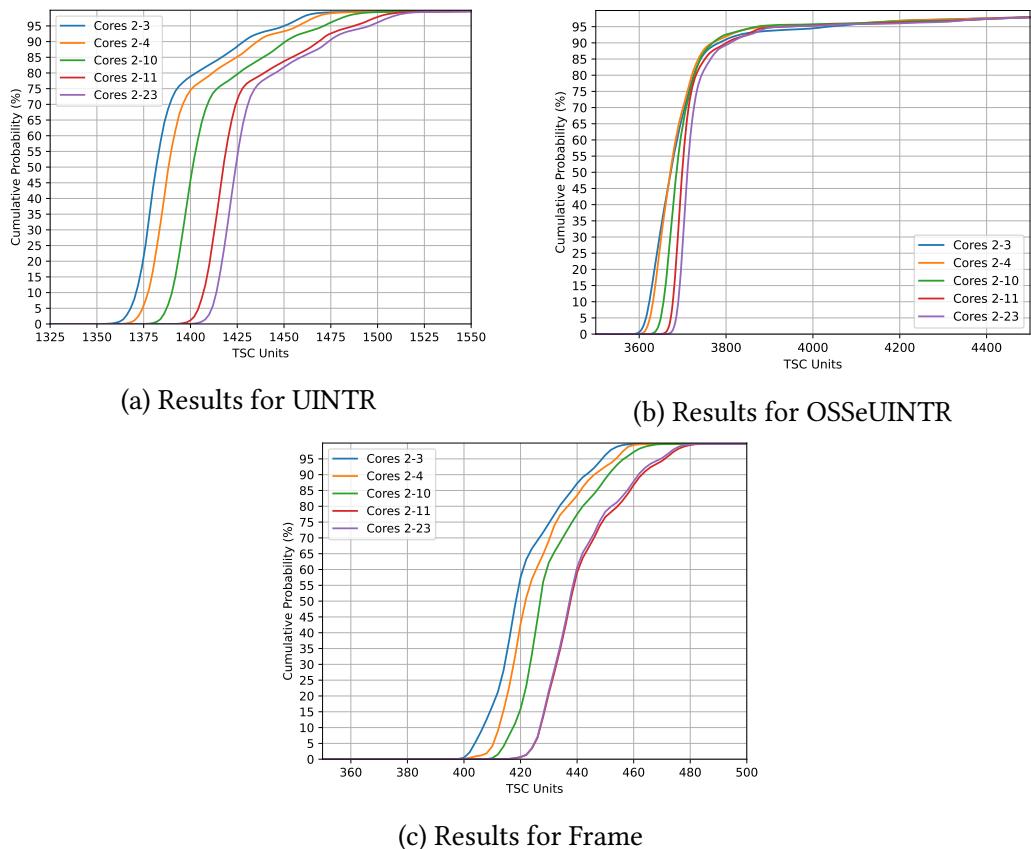

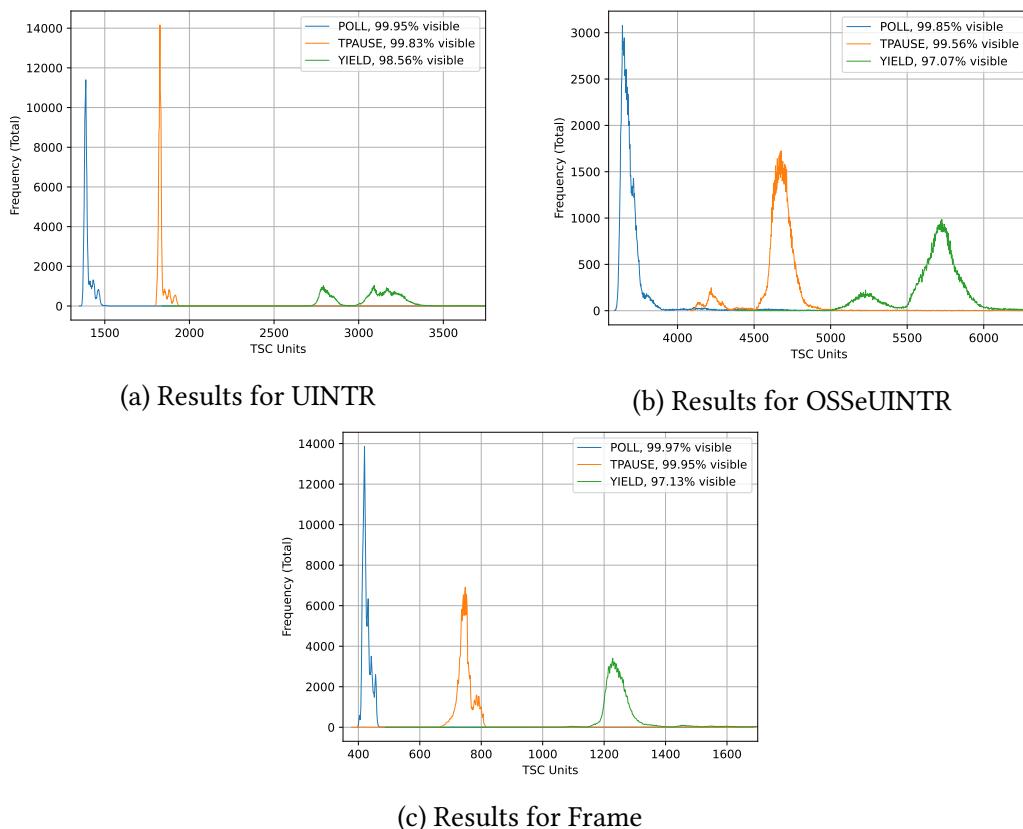

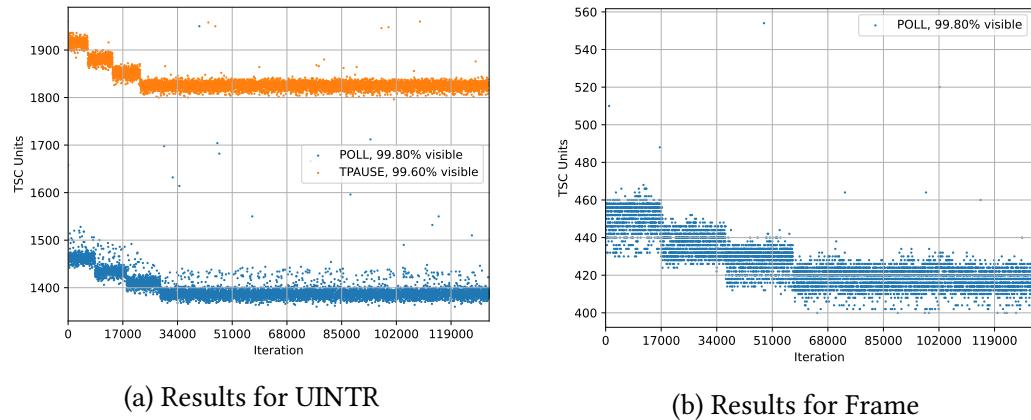

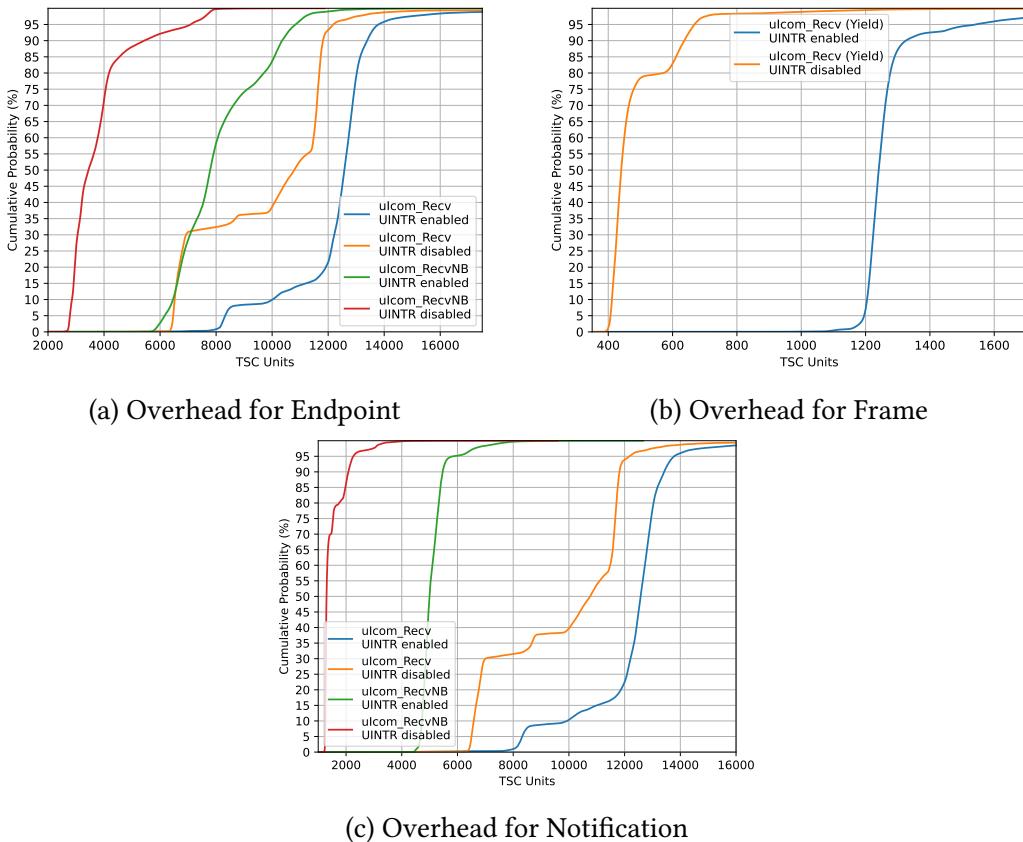

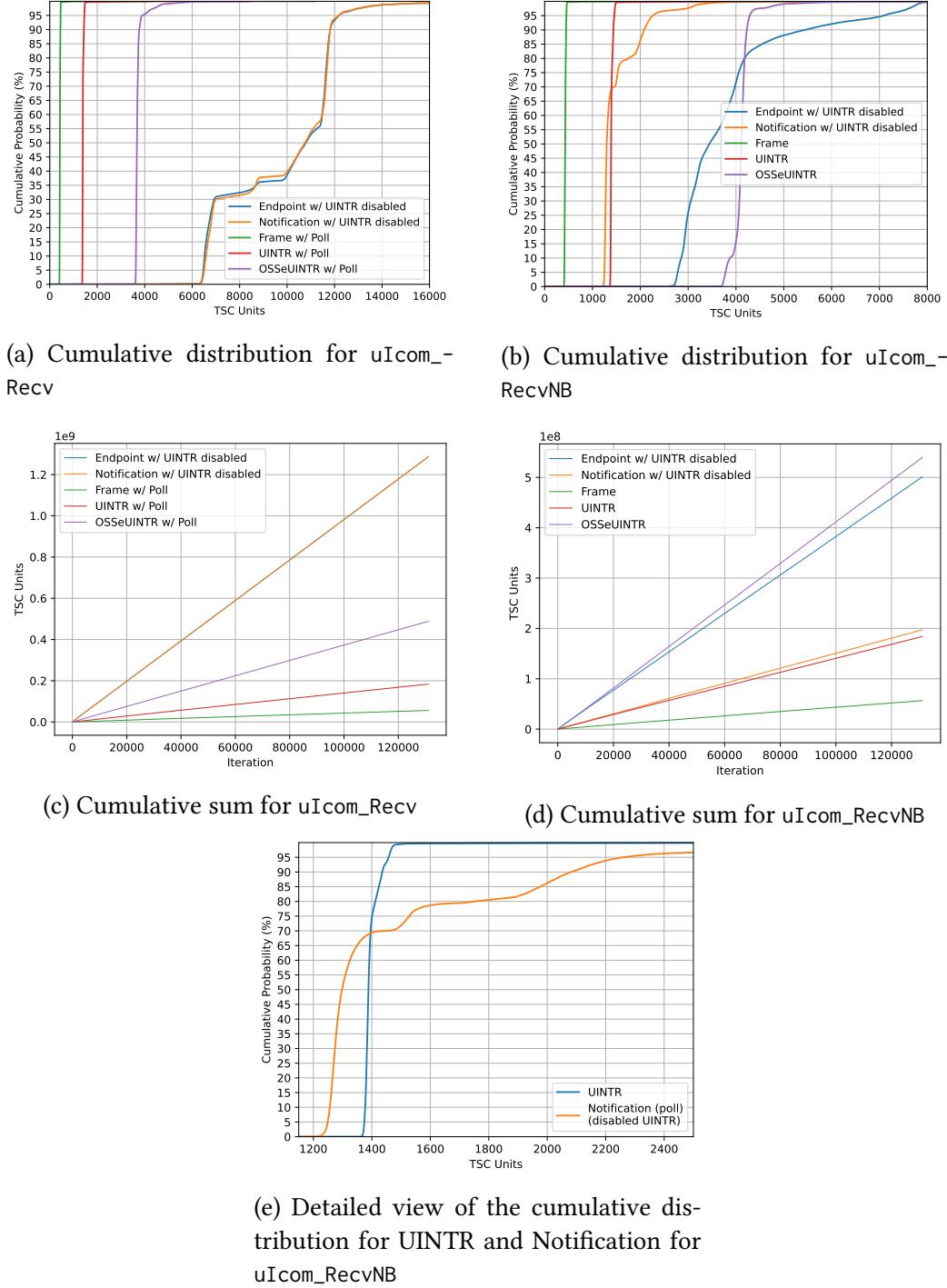

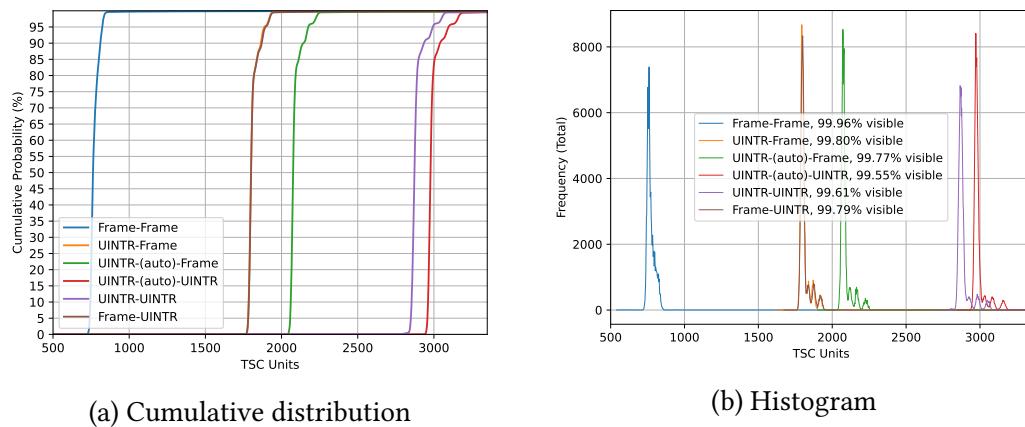

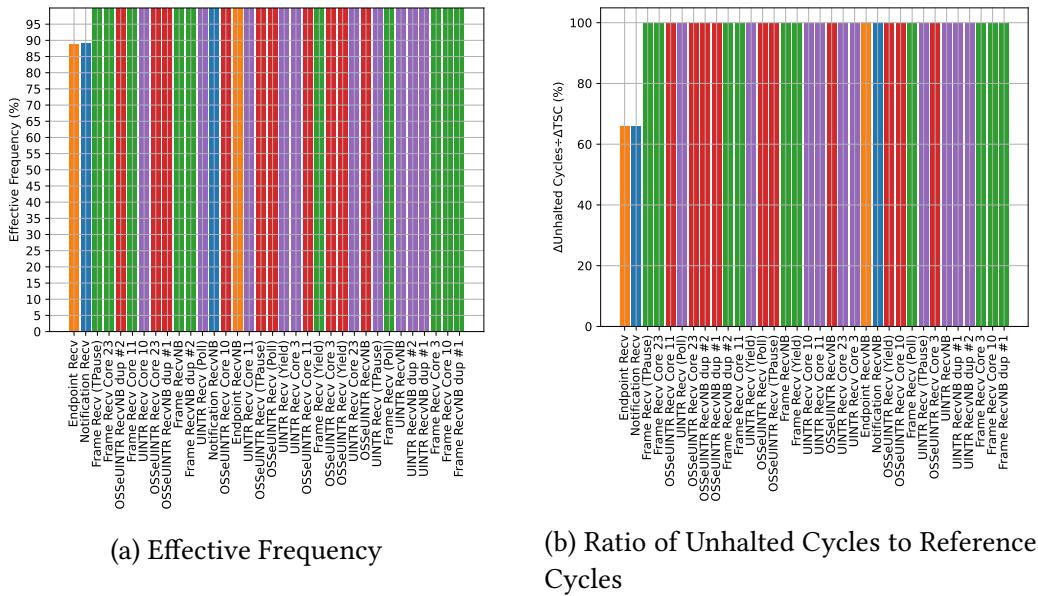

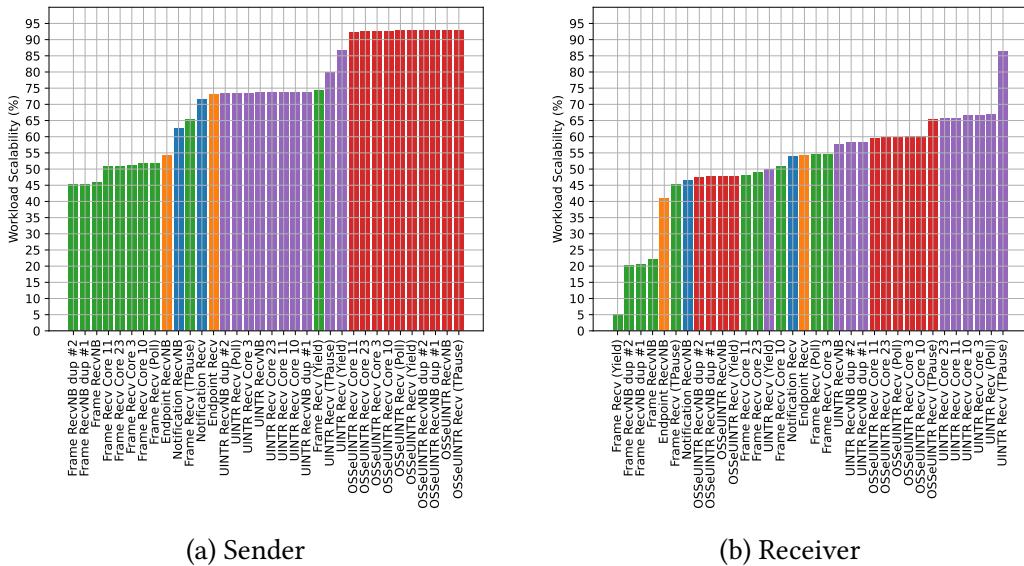

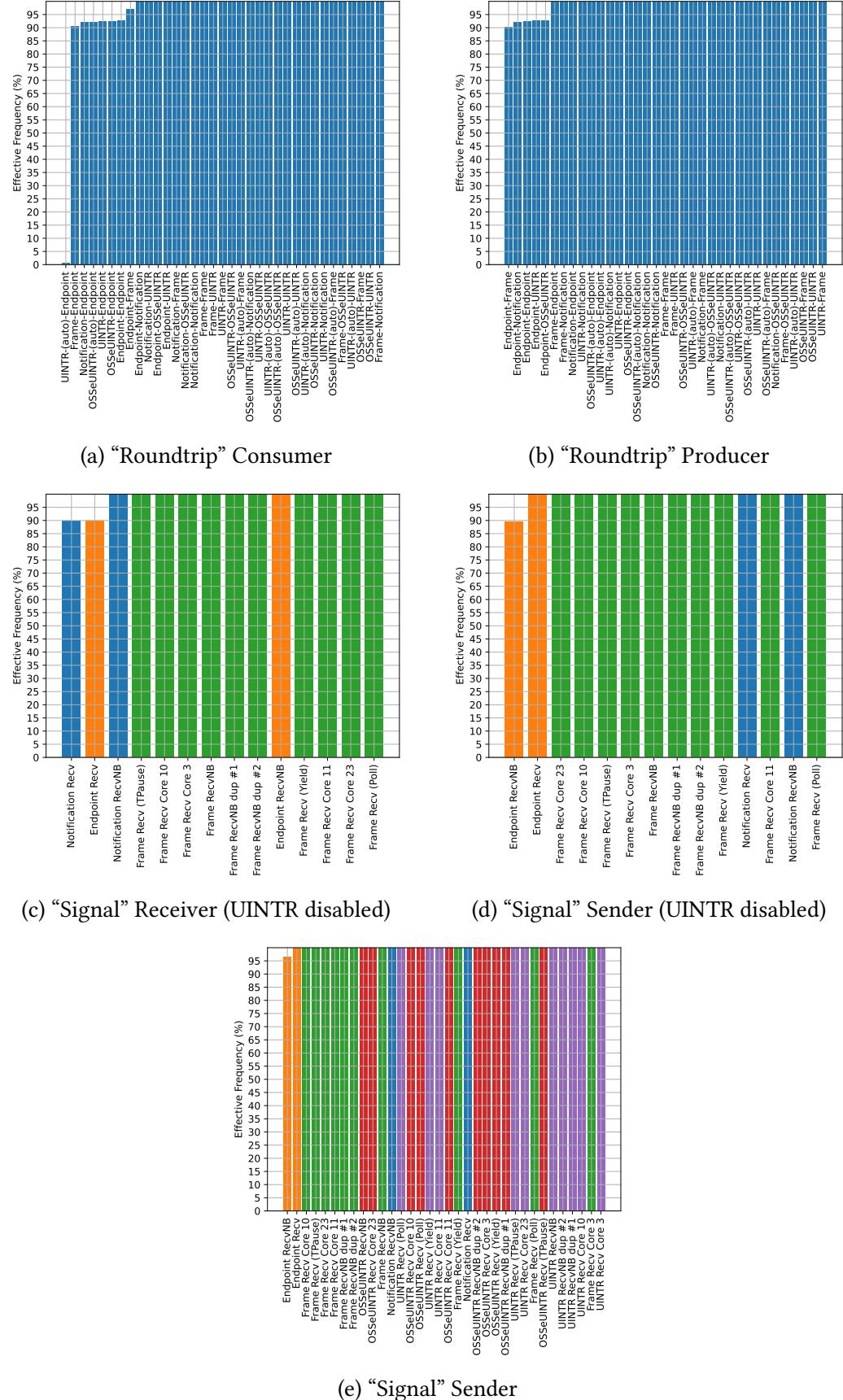

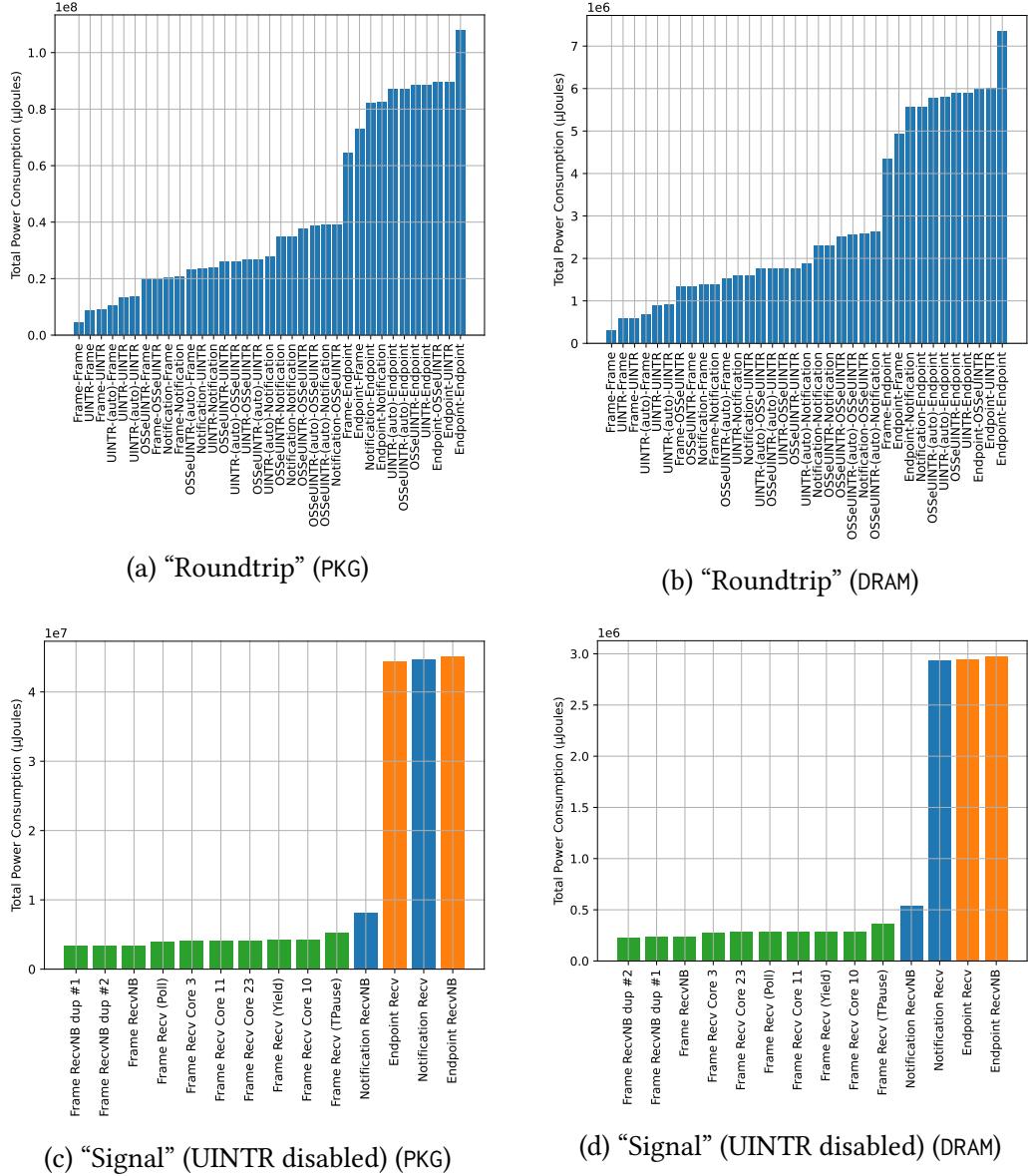

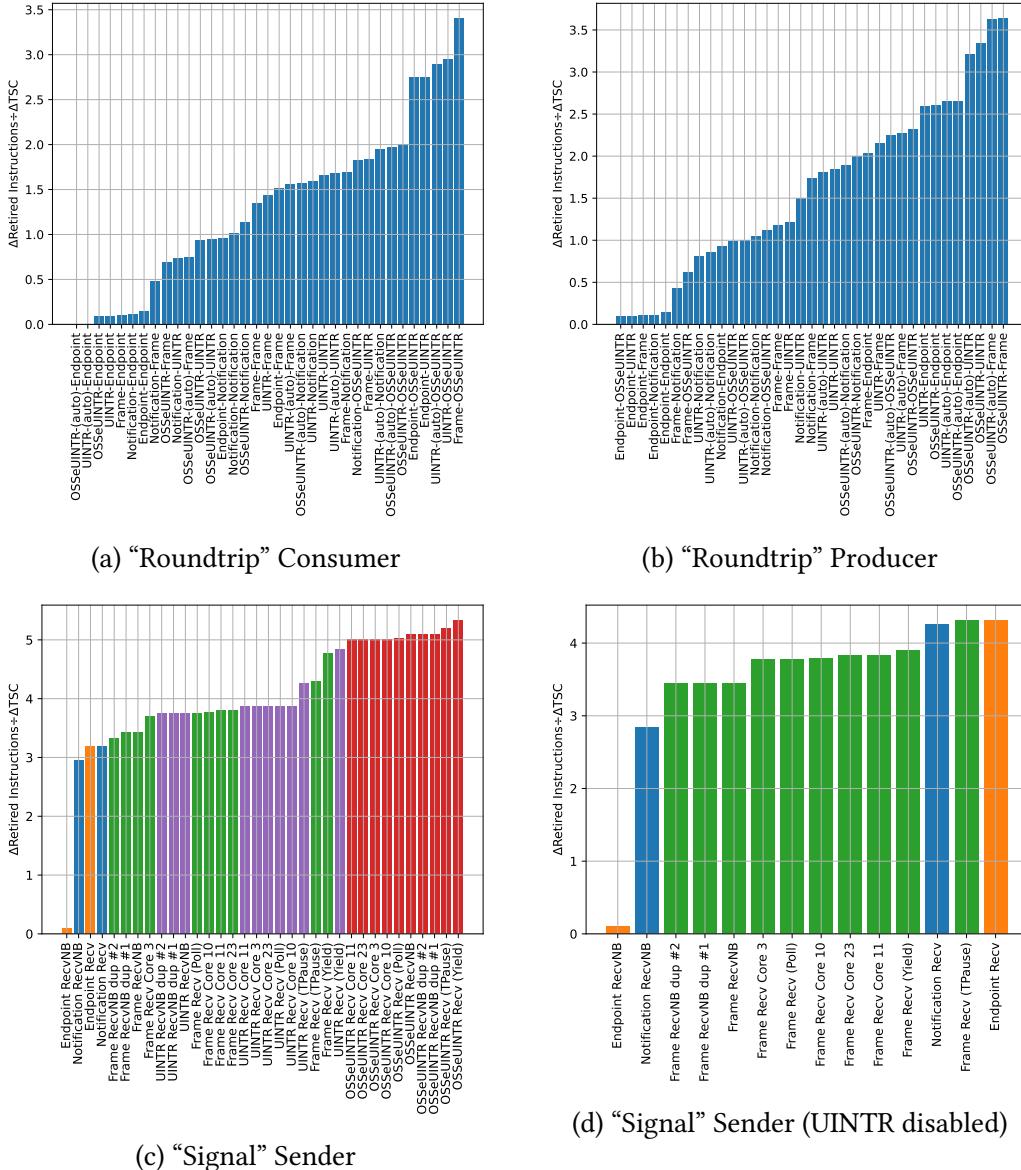

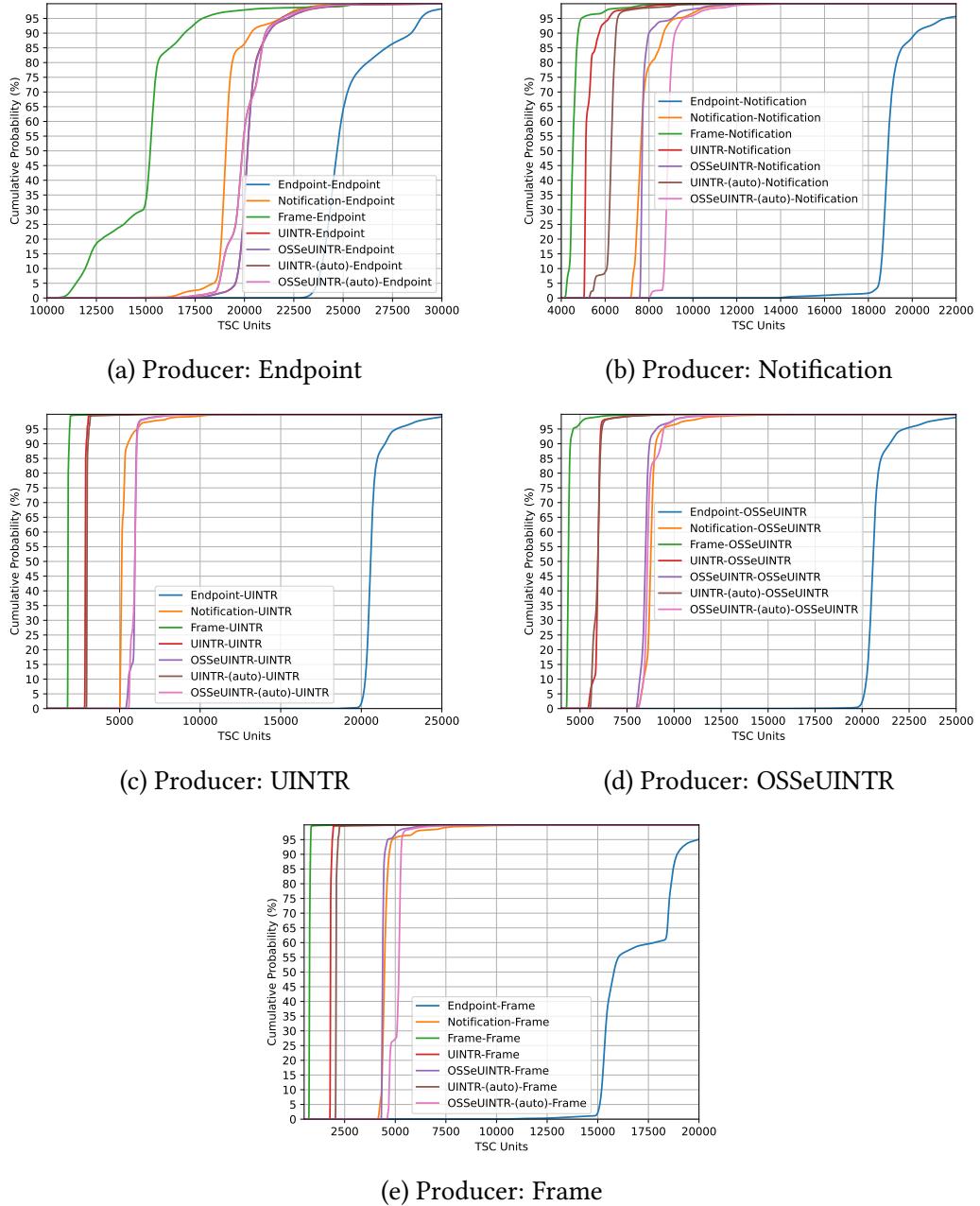

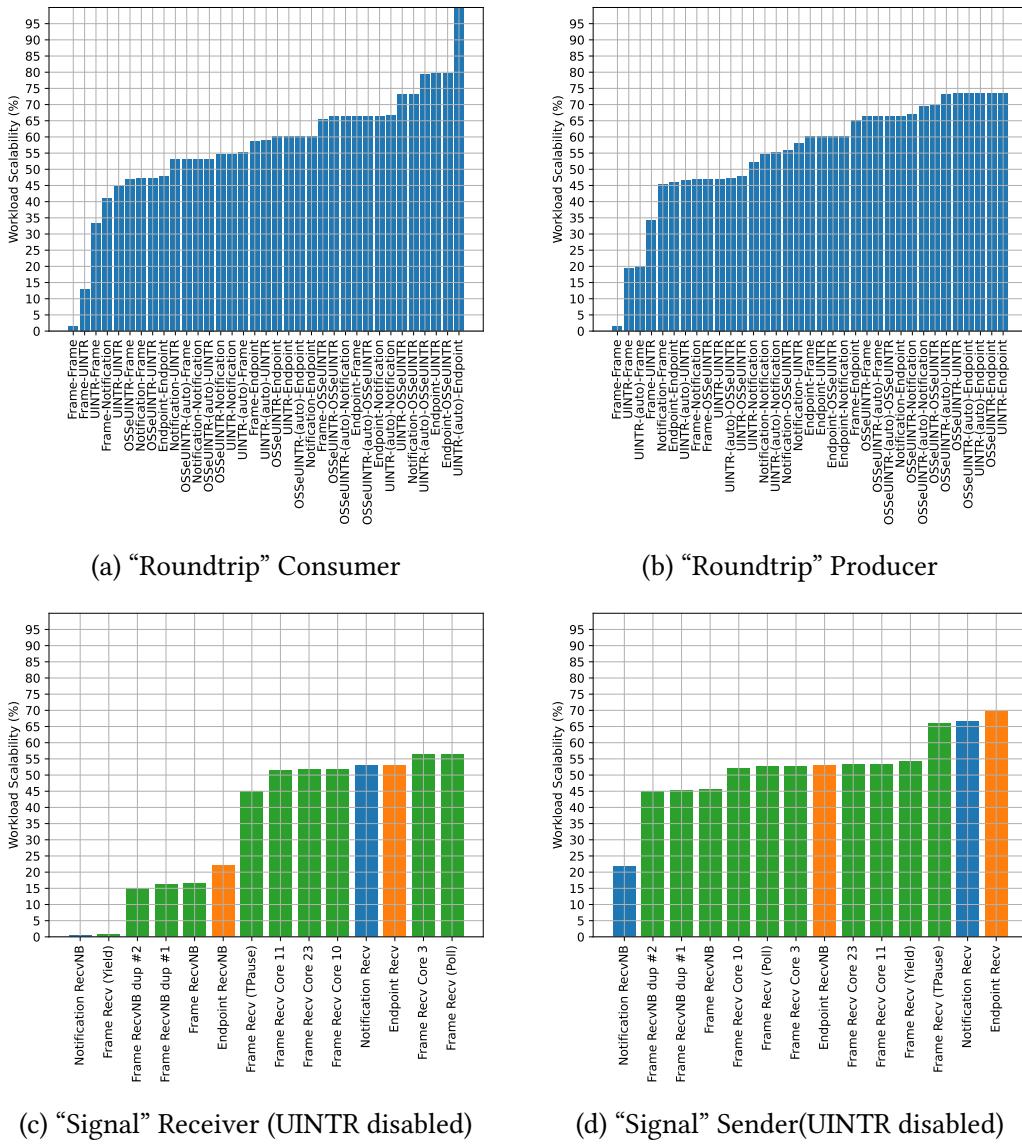

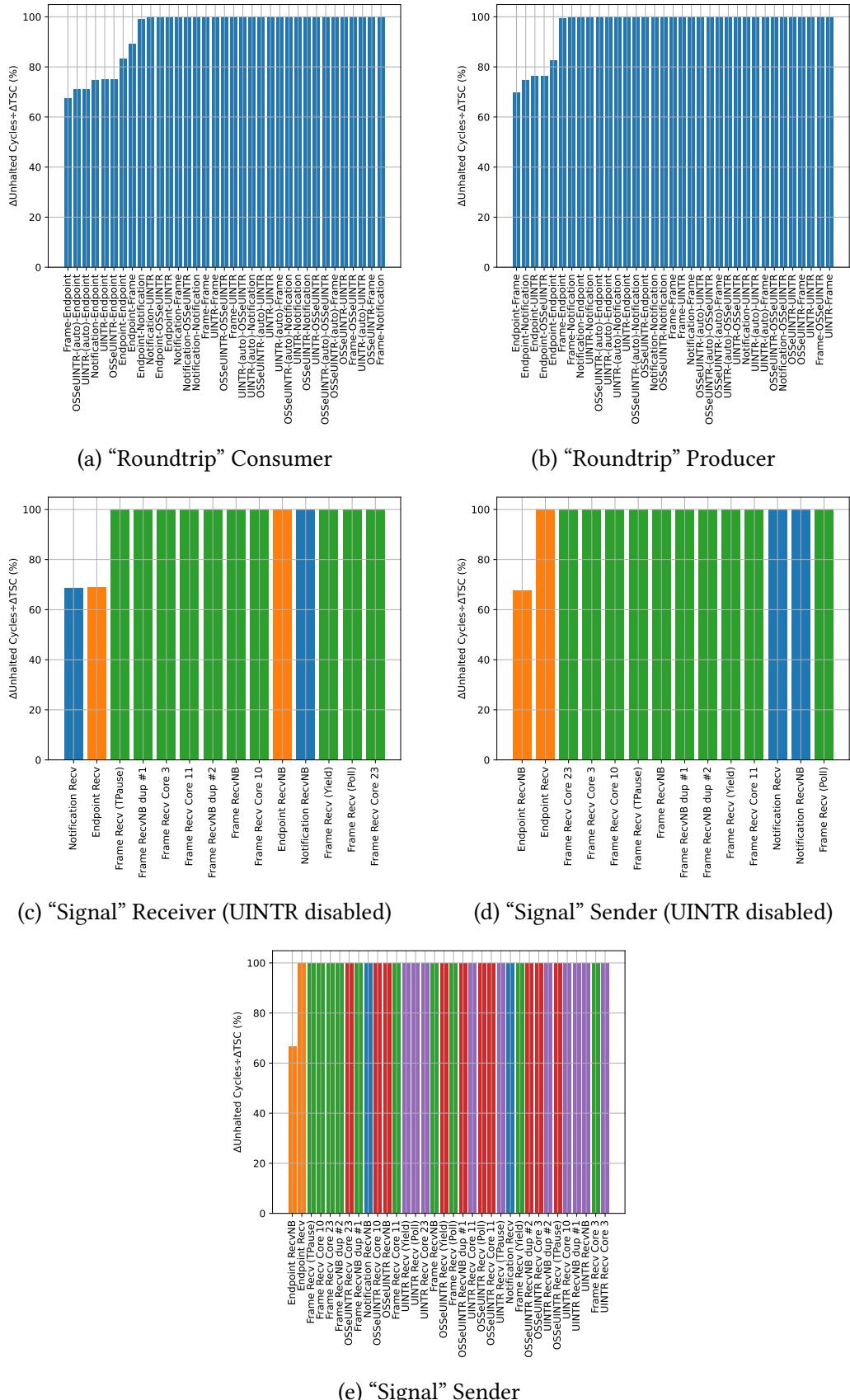

| 6.3.1    Time Performance . . . . .                       | 66         |

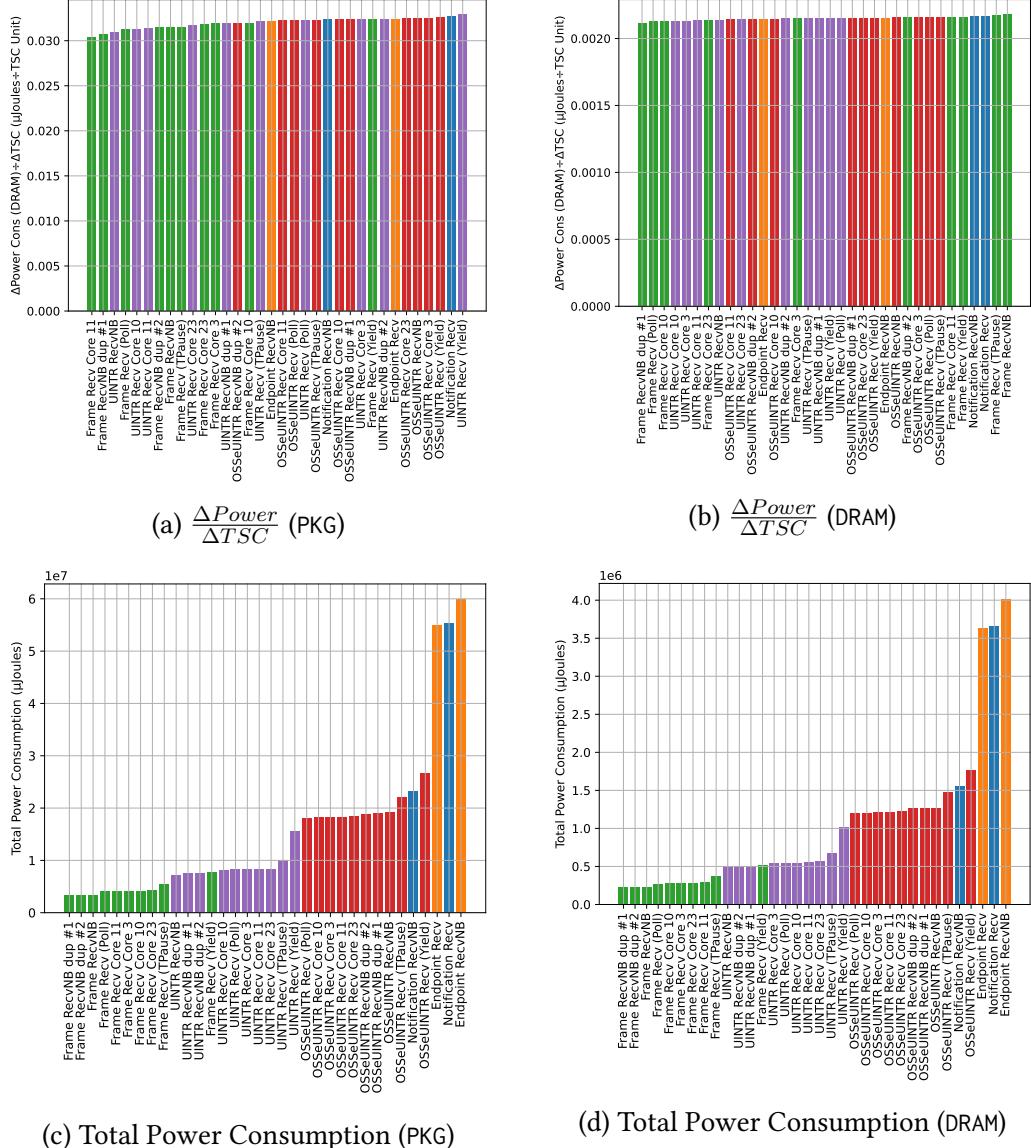

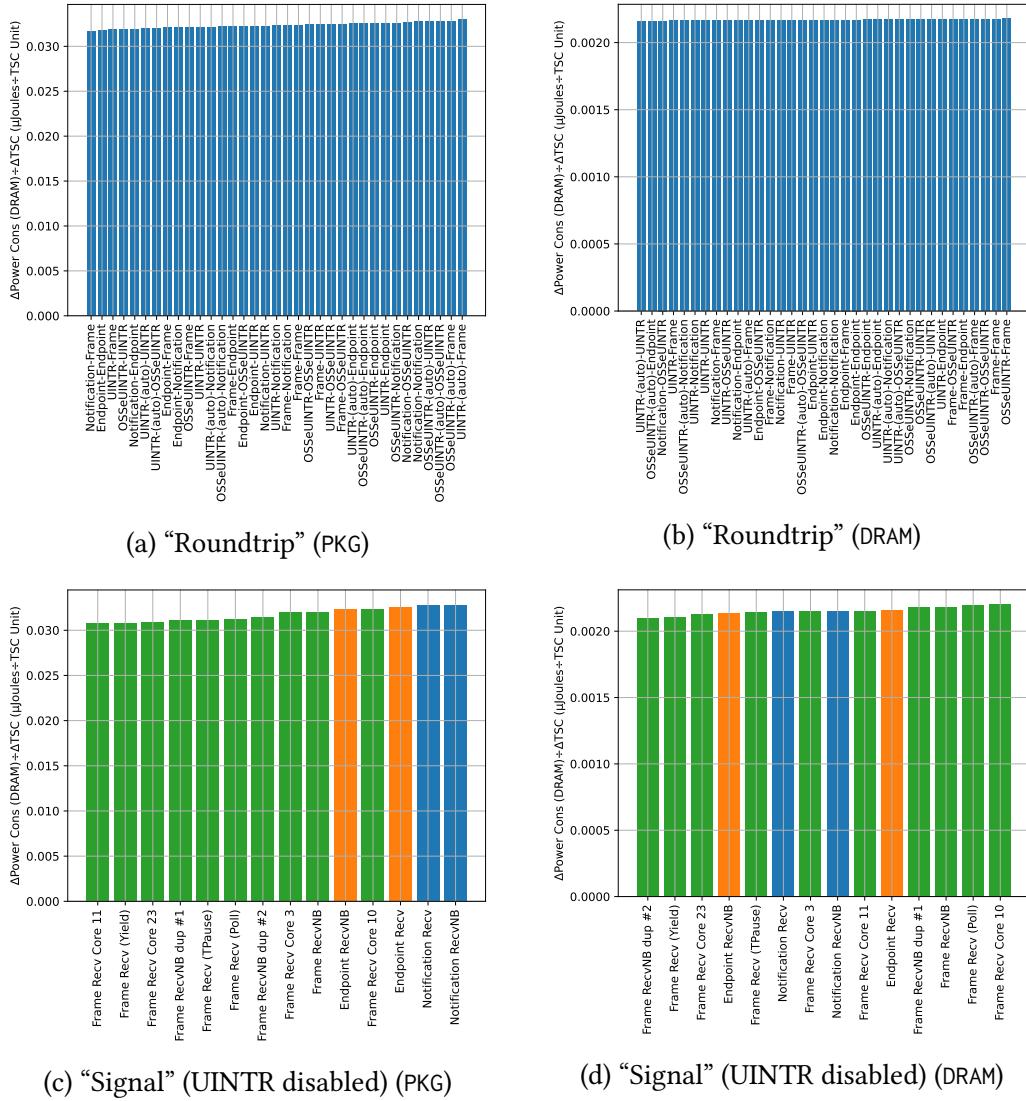

| 6.3.2    Power Performance . . . . .                      | 71         |

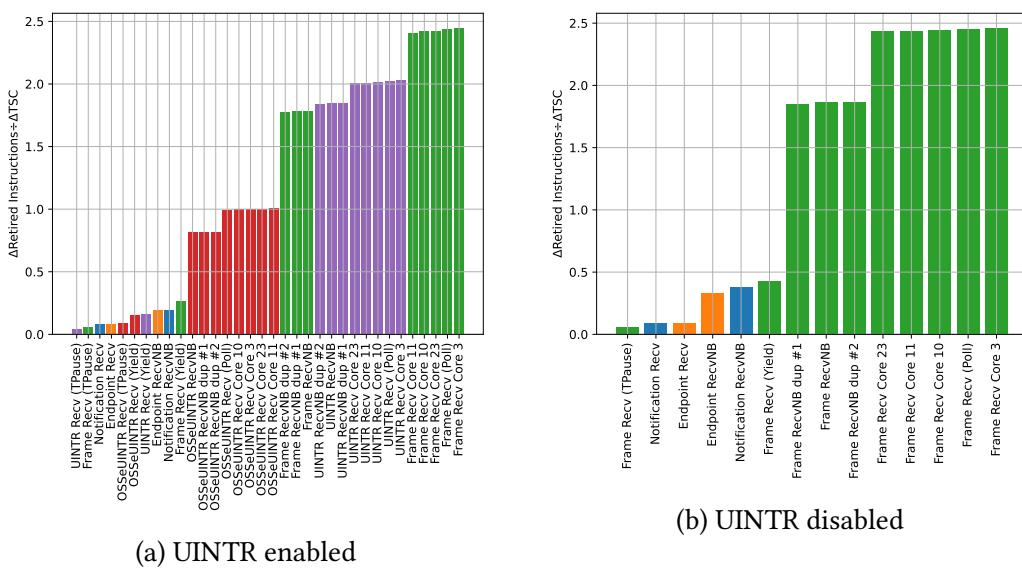

| 6.3.3    Further Performance Indicators . . . . .         | 72         |

| 6.3.4    Comparison to Related Work . . . . .             | 74         |

| <b>7 Conclusion</b>                                       | <b>77</b>  |

| 7.1    Conclusion . . . . .                               | 77         |

| 7.2    Future Work . . . . .                              | 78         |

| 7.2.1    Expanding uIntercom . . . . .                    | 78         |

| 7.2.2    Expanded Evaluation . . . . .                    | 79         |

| <b>Bibliography</b>                                       | <b>81</b>  |

| <b>A Discussed Data</b>                                   | <b>89</b>  |

| <b>B Further Data</b>                                     | <b>101</b> |

| <b>C Glossary</b>                                         | <b>109</b> |

# Chapter 1

## Introduction

Microkernels ( $\mu$ kernels), kernels with minimal functionality, built to increase isolation and limit error propagation, have been a topic of research for nearly 40 years now [1]. Since then, they have been redesigned and improved in every way [2], used as operating system (OS) research subjects [3], and even formally verified [4]. Major contributions to the field were also developed here in Karlsruhe [5]. Recently introduced processor features, such as memory protection keys (MPKs), have just started being investigated for applicability in these minimal systems, sometimes with impressive results [6, 7].

User-interrupts (UINTRs) are a new technology that allows interrupts to be forwarded directly to user-space. As a kernel-bypass mechanism, they might be a potential candidate for improving  $\mu$ kernel interprocess communication (IPC) and scheduling performance, which have been major bottlenecks of  $\mu$ kernels ever since their inception [8]. Another recently introduced technology is the user-wait extension, which allows user-space processes to enter power-saving states while waiting for events [9], which was only possible in kernel mode before. Given the precedent for modern processor features improving IPC performance in addition to two yet-to-be-evaluated new features on Intel's x86/64 platform, we ask whether these can be 1. Integrated into a modern  $\mu$ kernel representative and 2. Used to create a new IPC library that performs better than the native systems from both a time and energy perspective in the cross-core case. In the following chapters we answer these questions.

First, we introduce these features and necessary background in detail in Chapter 2 and give an overview of related work in Chapter 3. After this we present our design for both the integration and the IPC library on our chosen  $\mu$ kernel in Chapter 4, which is then followed by our description of both the implementation process and its details (Chapter 5). We then present our benchmark design and evaluate the collected data in Chapter 6, which we use to finally draw our conclusion and present an outlook for future work in Chapter 7.

# Chapter 2

## Background

This chapter is a summary of important concepts and necessary background information for later chapters. We first introduce the concept of  $\mu$ kernels in §2.1 to provide an insight into some core concepts as well as their history. Afterwards, we take a look at basic terms in IPC and provide some examples in §2.2. As UINTRs relies on interrupts as an underlying mechanism, §2.3 briefly introduces regular interrupts, which will be expanded upon in §2.4, in which we discuss the new UINTR feature, how it works, and how the user-wait extension could provide synergizing effects. Finally, we introduce important systems of the seL4  $\mu$ kernel in §2.5.

### 2.1 Microkernels

In this section we introduce  $\mu$ kernels. For this, we first introduce the concept of a kernel itself (§2.1.1), which is then used to define the differences between  $\mu$ kernels and monolithic kernels in §2.1.2. To conclude, we give a brief history of the L4 family of  $\mu$ kernels in §2.1.3.

#### 2.1.1 What is a Kernel?

An OS is responsible for abstracting system resources and providing a generally platform-independent, isolated interface for user applications [10]. To this end, most OS's have a core part, called a kernel, that directly controls these hardware resources with privileged instructions. These instructions can only be executed with certain execution privileges, which the kernel—in most cases—reserves for itself in order to keep untrusted user software from interfering with other programs or itself. This mode of increased execution privilege is incidentally called “kernel mode”.

In order to perform low-level interactions with hardware or parts of the OS, user software must do so through system calls, which are predefined entry points into the kernel and run in kernel mode (unless the kernel itself is running on a virtual system, in which case it usually has a different privilege level, which is lower than the actual kernel mode). Once the system call has finished executing, control is returned to the user software with the original privileges [11].

### 2.1.2 Micro- & Monolithic Kernels

Traditional kernels, such as Linux or Windows, have many different modules with various functions such as device drivers, extensive memory management, file system functions, a or multiple schedulers, etc. integrated right into the kernel. This leads to a large interconnected code base, a monolith, running in kernel mode. This is what is traditionally considered a monolithic kernel [8]. Monolithic kernels have large trusted codebases (TCBs), meaning there is a large amount of code that is trusted to be safe and secure. A potential attacker has a large attack surface to exploit, since compromising a single kernel module can compromise the entire kernel. In a similar vein, an erroneous kernel module can bring the entire system down by, for example, writing into a critical section of memory.

In contrast, a  $\mu$ kernel is often the minimal set of system calls and subsystems required to get a system to run user-mode software. Modules that are part of the kernel in monolithic kernels are delegated to processes in user-space (called “system servers”), which can be called by clients via IPC, which is one of the few systems managed by modern  $\mu$ kernels [12]. Moving kernel modules to user-space system servers reduces the attack surface of the actual kernel by deprivileging large chunks of potentially vulnerable code and leads to better fault isolation, since an erroneous server will only compromise itself, while the rest of the system is unaffected. This isolation, however, comes at a cost. Since in monolithic kernels inter-module communication consists of simple function calls and user-module communication requires a single system call, these processes are comparatively speedy when seen in contrast with  $\mu$ kernels, where a simple file system access can take multiple IPC round-trips through various system servers, tightly coupling client performance with that of the IPC design [7].

### 2.1.3 Historical and Modern L4 Microkernels

The original L4  $\mu$ kernel itself was born out of frustration with the state of first-generation  $\mu$ kernels, which were promised to be fast, secure, and lightweight, but in practice were slow, boiled-down versions of existing monolithic kernels, with the slowness of IPC being a major limiting factor for their performance [8]. L4 started as a from-scratch redesign of the IPC subsystem of Liedtke’s L3  $\mu$ kernel,

with a focus on new ideas that would lead to speed improvements. By reducing the amount of invoked system calls by merging send & receive, novel optimizations for message passing, like passing small messages via registers, and a new design for thread control blocks (TCBs) led to a 20x speed advantage compared to the Mach µkernel at that time [13]. These were later expanded upon and spun off into the new L4 µkernel, with a truly minimal amount of kernel systems, like a new form of address space management via system calls for sharing, granting and revoking pages and interrupt forwarding via IPC messages [2].

*Fiasco* was the first L4 µkernel to be implemented in a higher language and was designed for and used in real-time systems, but continued the belief that µkernels were inherently platform specific and had to be implemented in assembly in order to have competitive IPC speeds [8] by doubling the latency compared to the original L4 [14]. However, this was disproven by Liedtke and his students in Karlsruhe with *L4Ka::Hazelnut*, which reimplemented L4 mostly in C++ and still retained comparable IPC speeds [15] along with *L4Ka::Pistachio*, which was developed in cooperation with UNSW/NICTA and introduced a split of L4's application programming interface (API) and application binary interface (ABI). *L4Ka::Pistachio* was therefore able to be the first easily ported multi-architecture version of L4 [5], with ports mostly only needing to modify 10% of the kernel code [16].

µkernels were a popular target for formal verification of OS's [17], an effort aimed at increasing security and reliability, which culminated in seL4, a from-scratch reimplementation of L4 with security and verification in mind [18]. seL4 was the first general purpose OS to be formally verified [4]. While the initial attempts assumed correctness of the compiler, hardware, assembly and boot code, more recent work targets not just the kernel itself, but the entire core seL4 platform [19] and is still the subject of current research, such as adding time protection to kernels to avoid timing attacks [3].

## 2.2 Interprocess Communication

IPC is the general term for communication methods between different correspondents on either the same machine or sometimes even remote machines. As such, it encompasses many different types, the most important of which we introduce in §§2.2.2 to 2.2.4. However, before dealing with these communication pathways, we first introduce categories for IPC implementations in §2.2.1, which we can later use to categorize both existing and our own IPC mechanisms.

### 2.2.1 IPC Categories

We categorize IPC into three different categories, based on required behavior for successful message delivery:

1. Synchronous, meaning both the sender and receiver need to be waiting on the IPC object at the same time

2. Asynchronous, meaning the sender and receiver do not need to be waiting on the IPC object at the same time, but instead only need to call the IPC object after another

3. Asynchronous-Preemptive, meaning only the sender needs to call the IPC object and the receiver is *preempted* to receive and/or process the message

Calls to synchronous, asynchronous, and asynchronous-preemptive IPC objects can be either blocking or non-blocking. However, for synchronous IPC, at least one of the IPC participants needs to be using a blocking call for successful delivery.

Examples for these categories in conventional OS's are: 1. SendMessage of the Win32 library, which waits until the message has been processed [20], 2. Pipes on Linux, where sent data is buffered by the kernel until retrieved by a receiver [21] and 3. operating system signal (OSS) on Linux, where pending signals are processed upon reentering user-space [22].

### 2.2.2 Message Passing

Our first IPC type is message passing, which is a mechanism to communicate and synchronize actions between correspondents and, in general, provides two operations: 1. Send to send a message and 2. Recv to receive a message [23, sec. 3.6]. The communication link used by the mechanism varies from implementation to implementation, but can range from network packets to shared memory. Message passing mechanisms are usually either synchronous or asynchronous, with an asynchronous mechanism also needing to specify a *buffering* policy—either bounded or unbounded buffers—to determine how a “large amount” of messages is dealt with, sometimes by discarding messages if the buffer is full [23, sec. 3.6.3].

### 2.2.3 Signals

Similar to message passing, signaling mechanism also use the Send and Recv operations and serve as event notifications, usually combined with a flag or data word to determine the type. The signaling mechanism usually only stores one

pending signal per signal type, as seen with Linux signals [22], or seL4’s Notification, which we cover in §2.5.3. Signals are usually either asynchronous or asynchronous-preemptive and sometimes used as the underlying mechanism to implement message passing, where they are combined with a shared buffer and a pending signal signifies pending data in the buffer.

### 2.2.4 Remote Procedure Calls

Remote procedure calls (RPCs) are an abstraction on top of bidirectional message-passing IPC between a client and a server that types messages from the client to the server as procedure arguments and messages from the server back to the client as return values [23, sec. 3.8.2]. This allows the client to call procedures on a remote server, which allows it to

- Outsource computation and/or

- React to events from outside sources (other clients, for example) by having a shared state without holding shared memory

An example for a system using RPCs is a remote file-system, with calls relating to normal file access such as `read`, `write`, `open`, `delete` instead being remote calls [23, sec. 3.8.2]. Return values would either be file data or status codes, depending on the operation.

“Remote” in this case simply means “not in this address space”, meaning that communication between threads with separate address spaces on the same machine that is structured like a procedure call is an example of a RPC. This definition is common for client–system server communication on µkernels [13], however, if system servers are *passive* instead of *active*, meaning they do not have their own executing thread but simply consist of an address space, this form of communication is instead referred to as protected procedure calls (PPCs) [24].

## 2.3 Interrupts

In this section we introduce the concept of an interrupt (§2.3.1), briefly touch on the hardware mechanism for delivering interrupts (§2.3.2), continue with how interrupts are tied to exceptions on Intel’s x86/64 platform (§2.3.3), and how user-space programs usually interact with interrupts (§2.3.4).

### 2.3.1 Mechanism

Interrupts on x86/64 are, at their basic level, signals sent to the processor to notify it that *something* has happened, combined with a number, which is called an

interrupt vector (IV), to determine how to process the interrupt [25]. The first 32 IVs are reserved for exceptions, while the remaining 224 are called user-defined interrupts (UDIs), and have no architecture-defined causes. Every IV is also assigned a priority, which determines if an interrupt service routine (ISR) may be suspended and interrupted by the arrival of an interrupt with an IV of a higher priority.

Interrupts can be classified either as external (hardware) interrupts or software interrupts [25, sec. 7.3]. Hardware interrupts are caused by external sources to notify the system of certain events that need to be handled. Since interrupts could only be received by privileged software until the introduction of UINTR, the notified system was usually the OS and contained drivers, or the interrupt was forwarded to user-space software with OS-specific mechanisms, some of which we introduce in §2.3.4. Common sources for hardware interrupts are finished-work notifications from input/output (I/O) devices, like a disk drive, and periodic timer interrupts configured by the OS [26]. Software interrupts, on the other hand, are classified into the following categories:

- Exceptions, some details of which we discuss in §2.3.3.

- Interprocessor interrupts (IPIs), interrupts sent from one processor to another.

- Self-interrupts, caused by executing instructions such as `INTR n`.

On a task-level an interrupt is handled by 1. suspending the current task, 2. executing the ISR, 3. restoring the suspended task. This means an interrupt is transparent to the executed software. However, care must be taken when designing ISRs as, if the interrupts arrive faster than they can be handled, the system may end up in a live-lock, constantly servicing interrupts while not completing any other work [26].

### 2.3.2 Advanced Programmable Interrupt Controller

Interrupts are managed in hardware by the local advanced programmable interrupt controller (APIC), which is a per-core piece of hardware that receives interrupts from processor pins, internal sources, or the IOAPIC [25, ch. 12]. Local APICs also have a unique ID, which can be used to address a core when sending IPIs. The IOAPIC is an external piece of hardware that receives external interrupts from I/O devices and system sources and then forwards these interrupts to the local APICs. APICs, as reflected in their name, are highly configurable and support features such as *posted-interrupt processing*, which allows physical interrupts to be rerouted to virtual interrupts, which can be used to direct interrupts directly into virtual machines [27, sec. 31.6].

### 2.3.3 Exceptions

Exceptions can be classified into three categories [25]:

- Faults, a usually correctable exception that occurs during the execution of an instruction. The offending instruction is restarted after fault handling.

- Traps, an exception that occurs after the successful completion of an instruction. The next instruction is started after trap handling.

- Aborts, severe exceptions. Handlers need to shut down the offending application or even system.

When an exception occurs, a software interrupt with the associated IV is generated. Depending on the exception, additional data may be pushed to the stack to be consulted by the handler. A common fault exception is a page fault that occurs when a process accesses an address on a page currently not in memory [25].

### 2.3.4 Interrupt Handling

On the Linux monolithic kernel, interrupts are usually handled in kernel-space, but for memory-controllable devices, user-space drivers can also make use of userspace I/O (UIO) [28] to handle and acknowledge interrupts. UIO can be used to move kernel drivers to user-space, but some devices may still require a small kernel module to control device functions. Interrupts with UIO are controlled by blocking `read()` or `select()` calls on the device-specific files to get notified of pending interrupts, and `write()`, which is usually used to enable or disable interrupts.

Alternatively, some drivers, such as the Intel's high precision event timer driver, forward interrupt events as OSS [29] to then be received in user-space. However, interrupt processing itself is still done in the kernel driver.

In contrast to this,  $\mu$ kernels simply forward interrupts to user-space as IPC messages and forego further processing in the kernel [26]. Device drivers either wait for the next interrupt IPC message, or register an asynchronous routine, which is called upon receiving an interrupt. The user-space tasks need to perform interrupt processing and then reset the hardware themselves, by either calling appropriate system calls or performing writes on memory-mapped devices.

## 2.4 Modern Processor Features

We introduce the background and current state of support for Intel's UINTR feature on their x86/64 platform in §2.4.1, after which we go into detail on how a

thread would receive (§2.4.2) and send (§2.4.3) interrupts with this new feature enabled. We end our focus on UINTR by specifically highlighting some of its limitations in §2.4.5. Finally, we introduce the user-wait extension in §2.4.6.

### 2.4.1 UINTR Feature Background

UINTR is a relatively new feature of Intel’s x86/64 platform to allow forwarding of regular interrupts, which would normally trap into an interrupt handler in kernel mode, to an interrupt handler in user-space. While the theoretical potential of such a feature for faster networking and high-speed devices was already being discussed in the early 2000s [30], its first potential for implementation was the planned Risc-V “N”extension [31], which was later withdrawn due to a lack of support for the current design [32]. Despite further support from some of the embedded systems community [33], the feature has yet to (re-)appear on other architectures. Intel is therefore the first, and, to this day only, manufacturer to support the UINTR feature, which was first introduced on Sapphire Rapids server processors and later on Sierra Forest, Grand Ridge, Arrow Lake and Lunar Lake processors [34].

In addition to allowing regular interrupts to be forwarded to user-space handlers, Intel’s UINTR implementation additionally provides user interprocessor interrupts (UIPIs), which allow user processes to send software interrupts with an additional parameter to each other [9]. Since its original introduction, there has been one minor revision that was introduced with processors after Sapphire Rapids. No OS has built-in support for the UINTR feature, with the official proposed Linux patch-set from Intel being fully abandoned in April 2024 [27] after the Linux kernel mailing list seemingly lost interest after 2022 [35].

### 2.4.2 Receiving User-Interrupt Notifications

In essence, UINTR allows user-space processes to receive interrupts directly in user-space instead of using OS-specific mechanisms like UIO [25]. By allowing this, UINTR has the potential to reduce the inherent latency of first handling the interrupt in kernel-space and afterwards forwarding them to the user process [35].

Once enabled by setting a bit in the CR4 register, potential recipients of user-interrupt notifications (UINs), which is what the delivery of a normal interrupt to user-space is called [25, sec. 8.1], need to set three model-specific registers (MSRs). These are 1. IA32\_UINTR\_HANDLER, 2. IA32\_UINTR\_MISC, and 3. IA32\_UINTR\_PD, as well as the optional IA32\_UINTR\_STACKADJUST MSR, each of which set a specific aspect used during user-interrupt delivery (UID).

### IA32\_UINTR\_MISC

The IA32\_UINTR\_MISC MSR sets multiple values. For one, it contains a bit for storing the user-interrupt flag (UIF) flag which is a flag that en- or disables UID. It is of note that the flag is only actually stored in this bit in the MSR's XSAVE-region after the UINTR state is been XSAVES-ed, not in the actual MSR [25, sec. 8.3.2]. The UIF is controlled by three new user-level instructions [25, sec. 8.6]:

1. STUI, which sets the UIF.

2. CLUI, which clears the UIF.

3. TESTUI, which returns the current value of the UIF.

In addition to this, it also contains the user-interrupts notification vector (UINV), which is used to determine the IV that triggers UIN identification, which, if successful, eventually leads to UID. Finally, it also contains the UITTSZ, which we will explain in §2.4.3.

### IA32\_UINTR\_PD and the UPID

This MSR sets the address of the user posted-interrupt descriptor (UPID), which is the structure used by the processor to track a thread's current UINTR state in the PIR field, with the remaining fields only being used by sending agents.

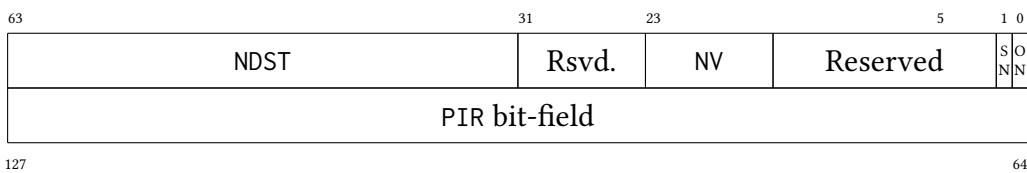

The UPID consists of the ON (outstanding notification) and SN (suppress notification) fields, which determine if a user-interrupt is a) pending and/or b) suppressed. They are used by sending agents to determine if they should send an IPI. ON is set automatically by SENDUIPI, while SN is free to be set by software. The UPID's memory layout can be observed in Figure 2.1.

Figure 2.1: UPID memory layout

In addition to these two bits, there is also the NV (notification vector) field, which sets the IV used by the IPI when SENDUIPI is executed while targeting this UPID, as well as the NDST (notification destination), which is the APIC ID of the destination core. Ideally, the NV is equal to the UINV set by the core targeted

by ND, otherwise the interrupt is received by the kernel instead of the targeted user-space thread. The remaining field is the PIR bit-field, which has a bit for every possible user-interrupt vector (UIV)  $v$  with  $v \in [0; 63]$ . Bit  $v$  is set if UIV  $v$  is requesting service [25]. Upon UIN processing, the PIR is OR-ed into the user-interrupt request register (UIRR), which lives in the IA32\_UINTR\_RR MSR, the most significant bit of which is the first UIV processed during UID.

### IA32\_UINTR\_HANDLER

This sets the user-interrupt handler (UIHandler), which is the linear address of the routine the rip is set to upon successful UID. The only requirement for this address is that it is canonical<sup>1</sup> and usually points to an ENDBR64 instructions [25]. The UIHandler is given two arguments upon execution: 1. The UINTR frame, consisting of the RIP, RSP, and RFLAGS of the interrupted thread; and 2. The UIV, which multiplexes a single UINV into multiple UIVs, thereby allowing multiple sources to signal the same thread with the same IV and still be distinguished by the receiver. UIVs are necessary because a thread can only have a single IV set as its UINV. Upon completion, the UIHandler should call UIRET, which is a new instruction that restores the state stored in the UINTR frame [25, sec. 8.6] and sets the UIF [25, sec. 8.3.1]. Intel introduced an extension to UINTR called “Flexible Updates of UIF by UIRET”, which instead makes UIRET load RFLAGS[1] into UIF, allowing threads to manage UIF from the UIHandler [25, sec. 8.7]. This enables receivers to mitigate potential live-locks from over-eager senders, which was impossible before this extension, as we again mention in §2.4.5.

### IA32\_UINTR\_STACKADJUST

This MSR sets the user-interrupt stack adjustment (UIStackadjust), a value which determines how the stack is adjusted when handling a user-interrupt. This is needed to prevent clobbering of the stack’s *red zone*, a region behind the stack pointer considered “reserved” and not allowed to be modified by interrupt handlers in some ABIs [37]. UIStackadjust[0] is used to determine whether the stack address is calculated by subtracting UIStackadjust from the current stack pointer, or simply set to the value of UIStackadjust. Since the resulting stack pointer is then forcibly 16-byte aligned, UIStackadjust[0] is automatically discarded when processing a user-interrupt [25, sec. 8.4.2].

The step-by-step process of successful UID is available in Listing 2.1. It is of note that a user-interrupt recognition (UIR) is only triggered if UIRR  $\neq 0$ . Therefore,

---

<sup>1</sup>A canonical address needs to have its unimplemented bits set to either all zeros or all ones. On the current x86/64 platform, these are all bits from index 63–48 [36, sec. 3.3.7.1].

Figure 2.2: UITT memory layout

successful UID can only occur if the PIR field has any set bits before a UIN is processed, which can prove to be a challenge when trying to receive interrupts from external devices [38].

### 2.4.3 Sending User Interprocessor Interrupts

In addition to allowing the reception of interrupts in user-space, UINTR also introduced the SENDUIPI instruction, which allows threads running in user-space to send IPIs to other user-space threads if correctly configured. Like with the setup of UINs, sending UIPIs also requires setting two MSRs: 1. IA32\_UINTR\_TT and 2. IA32\_UINTR\_MISC.

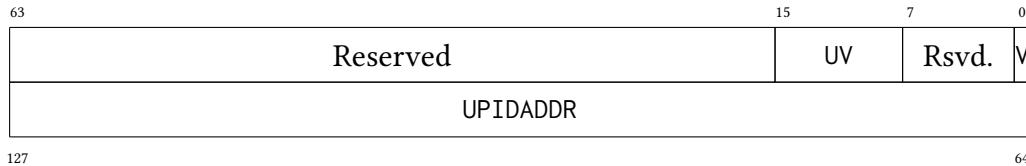

#### IA32\_UINTR\_TT and the UITT

Similar to the IA32\_UINTR\_PD MSR, the IA32\_UINTR\_TT MSR sets the address of the sender-specific data-structure, the user-interrupt target table (UITT). The UITT, as the name implies, is a table consisting of one or more user-interrupt target table entries (UITTes), each of which describe a combination of a receiver, by containing the address of a UPID in UPIDADDR, with a UIV, which is set in the UV field. Additionally, there is also the V (valid) field, which determines whether an entry is valid. A UITTe's memory layout can be examined in Figure 2.2. Of note is that the length of UV is 8 bits, which sets its possible value range to [0; 255], however, bits 15:14 must be set to zero, lowering the permitted range back to [0; 63], therefore not conflicting with the UPID's PIR bit-field as seen in §2.4.2. In addition to the UITT's address, IA32\_UINTR\_TT also contains a bit to activate the SENDUIPI instruction. When SENDUIPI  $n$  is executed, the  $n$ th entry in the UITT is indexed into and checked for a set V bit. If set, the UPID from UPIDADDR is then retrieved and the  $UV$ th bit in the UPID's PIR bit-field is set. If neither the UPID's ON or SN bits are set, the executing core then sends an IPI with IV NV to the APIC with ID NDST [9, chpt. 4, SENDUIPI]. An IPI sent via this mechanism is called a UIPI.

---

```

1 [Previous Events and Conditions]

2 - All (receiver) MSRs are set to valid values

3 - UPID.PIR[UIV] = 1, UPID.PIR[!=UIV] = 0

4 - UIF = 1

5 - An interrupt of vector IV = UINV

6         was sent to the core with the UPID installed

7

8 [Start User-Interrupt Notification Identification]

9 - Local APIC is acknowledged

10 - Local APIC interrupt is dismissed

11 [Start User-Interrupt Notification Processing]

12 - UPID.ON = 0

13 - UIRR |= UPID.PIR

14 - UPID.PIR = 0

15 [User-Interrupt is Recognized]

16 [Start User-Interrupt Delivery]

17 - Processor is woken up from

18     user-entered power saving states

19 - IF UISTACKADJUST[0] == 1:

20     - RSP = UISTACKADJUST

21 - ELSE:

22     - RSP = RSP - UISTACKADJUST

23 - RSP = RSP & ~0xF

24 - User-interrupt frame (Old RSP, RIP, RFLAGS)

25         is pushed to stack

26 - UIV is pushed to stack

27 - UIRR[UIV] = 0

28 - UIF = 0

29 - RIP = UIHandler

30 - [End]

```

---

Listing 2.1: UID, with some minor details omitted

### IA32\_UINTR\_MISC (continued)

As previously mentioned, the IA32\_UINTR\_MISC MSR also contains the UITTSZ field. UITTSZ + 1 determines the size of the UITT if SENDUIPI is activated in IA32\_UINTR\_TT. It is used when executing the SENDUIPI  $n$  instruction, where, if  $n > \text{UITTSZ}$ , execution is aborted and a general protection fault (GP fault) is raised.

#### 2.4.4 UINTR-XState

The extended state (XState) is a set of state components that originally was limited to just the x87 FPU state [36, sec. 10.5]. It is thread-specific and needs to be saved and restored during context-switches, for which the instructions XSAVE and XRSTOR were implemented [36, chpt. 13]. XSAVE and XRSTOR are not privileged and save the XState to memory given by an argument [9, sec. 6.1, XSAVE]. Eventually, XSAVES and XRSTORS were also introduced, which are privileged instructions that save and restore additional XState components that should not be accessed or modified from user-space [9, sec. 6.1, XSAVES]. XSAVES-managed state components are both set and enumerated differently than the regular XSAVE components.

UINTR also has an XSAVES-managed state component that can be saved and restored. It encompasses every MSR mentioned above, as well as the UIF flag. Notably, executing XSAVES on the UINTR state component modifies the IA32\_UINTR\_MISC MSR and clears UINV [36, sec. 13.5.11]. This means that XSAVES is destructive for the UINTR state and executing two consecutive XSAVES will overwrite the saved state with the cleared state, deleting UINV. Implementations therefore need to either keep track of UINVs or ensure that every XSAVES is *always* followed by XRSTORS before the next call.

A potential reason for this truly baffling behavior is the issue of erroneous UID, which might occur if the UINTR MSRs are not cleared when another thread is switched in. The theoretically still valid MSR values lead to UIN processing if the memory address of IA32\_UINTR\_PD is somehow still valid and ON or SN or any reserved bits are not coincidentally set when a sender, unaware of the receiving threads scheduling, executes SENDUIPI. UIN processing then triggers UID, which sets RIP to the previously-set UIHandler address, which then tries to execute potentially random memory, causing errors. Clearing UINV prevents this, as the IPI is instead delivered to the kernel. However, this only solves the issue for kernels that use XSAVES, which is not guaranteed (see §5.2.3).

### 2.4.5 Limitations of UINTR

UINTR cannot be fully controlled by user-space. In order to receive UINs, a thread needs to set at least three MSRs, while a sender only needs to set two. Both the sender and receiver need to have the receiver’s UPID mapped to their respective address spaces. Furthermore, the sender also needs to have their UITT mapped into their own address space. However, since all memory accesses during the execution of `SENDUIPI` and UIN processing are performed with supervisor privileges [9, 25], these mappings do not need to be user-accessible. In fact, we believe user access to these data structures is dangerous, the reasons for which we explain in the remainder of this section.

We conclude that some level of kernel-control over the UINTR feature is necessary, for the following reasons:

1. Setting up UIN completely hides any events on the selected IV from the kernel. The kernel should not be circumvented for UINTR setup, as a user-process could then simply “steal” critical IVs, such as the regular timer interrupt, and therefore cripple the OS’s abilities, which is in this case the ability to preempt and reschedule tasks.

2. The UPID contains a notification vector field, which determines the IV used by processes when executing the `SENDUIPI` instruction. Since this field is decoupled from the MSR that determines which interrupts are forwarded to user-space, free control over this field could be used by nefarious processes to send any IV they want, potentially messing with OS-systems or introducing live-locks.

3. Freely controlling the UITT can be used to create false entries pointing to user-owned memory. Since every UITTe contains a UPID address to consult when executing `SENDUIPI`, free control over UITTees would lead to the same situation as seen with free control over the UPID.

In addition to these concerns, UINTR should only be used between trusted correspondents if the “Flexible Updates of UIF by UIRET” extension is unavailable, due to the concern for potential live-locks caused by malicious senders of UIPIs. Despite exceptions triggering interrupts, UINTR does not support handling of exceptions in user-space, although there have been discussions about potential use-cases of such a feature [39, 40].

### 2.4.6 User-Wait Extension

The user-wait extension was introduced around the same time as UINTR, with it first appearing on Intel Xeon processors together with UINTR on Sapphire

Rapids [36]. It expands the already existing wait instructions MWAIT and MONITOR—which allow the processor to enter an implementation-dependent optimized state upon executing MWAIT until an event or store occurs on the address range previously specified by MONITOR [9, sec. 4.3, MWAIT]—with user-mode equivalents UMWAIT and UMONITOR. MWAIT is allowed to switch to any C-State, while UMWAIT is limited to just C0.1 and C0.2. We will call these optimized states “sleep states” after this point.

In contrast to the privileged counterpart, UMWAIT has an immediate argument, which sets the time stamp counter (TSC) timestamp after which the processor exits the sleep state even if no event occurs. This means that programs wanting to use UMWAIT first need to read the TSC, then add their desired deadline offset, then execute UMWAIT. In addition to this argument, there is an additional deadline, usually set by the OS, called the OS deadline. It determines the maximum time in TSC units that UMWAIT is allowed to wait for. Note that the OS deadline is an offset instead of a timestamp. The OS deadline is set with a new MSR, called IA32\_UMWAIT\_CONTROL, which also controls the maximum sleep state UMWAIT is allowed to enter [25, sec. 4.3, UMWAIT]. The extension also adds the TPAUSE instruction, which acts like UMWAIT but without a monitored address range. TPAUSE therefore only waits for the deadlines, while UMWAIT can also exit the sleep states earlier due to memory events [9, sec. 4.3, TPAUSE]. The user-mode sleep states are also exited upon receiving an interrupt, with Intel’s manuals specifically mentioning that user-interrupts also cause this behavior [25, sec. 8.4.2].

Due to issues with how MONITOR and UMONITOR reclaim addresses, processors that repeatedly execute these instructions may suffer from performance loss or an inability to enter sleep states on some affected architectures [41].

## 2.5 Introduction to seL4

This section introduces some technical details of the non-mixed-criticality system (MCS) seL4  $\mu$ kernel on x86/64. As part of this, we first introduce the limited number of system calls in §2.5.1, describe what seL4’s capability-based access-control entails and how it is implemented in §2.5.2. After this, we focus on existing IPC paths for seL4 in §2.5.3 and finally explain existing methods for interrupt handling in §2.5.4.

### 2.5.1 System Calls

seL4, being an L4  $\mu$ kernel, implements only three basic system calls [42, sec. 2.2]:

1. Yield, which returns control to the kernel and invokes the scheduler. This is the only system call that does not require a capability to invoke.

2. Send, which sends data via a capability and performs capability-specific actions.

3. Recv, which receives data via a capability.

While these calls are enough to provide all required functionality, seL4 further implements six more system calls [42, sec. 2.2], which are mostly simple variants of the previously mentioned calls. For our purposes, we only focus the following three:

- Call, which combines Send and Recv into a single system call.

- NBSend, which is Send, but does not ensure delivery and returns immediately if the message could not be delivered.

- NBRecv, which polls for a new message and returns immediately if none are available. Otherwise it acts like Recv.

Call specifically implements some additional functionality, which will be further elaborated in §2.5.3 after capabilities have been introduced in the following sections. The Send and Recv system calls and variants use thread-specific message registers to pass data and are invoked with user-space stubs. The signature for the Send-stub is `void seL4_Send(seL4_CPtr dest, seL4_MessageInfo_t msgInfo)`, where `dest` is the invoked capability and `msgInfo` is a struct that holds a label and the `message_length`, among other fields [42, sec. 4.1]. The amount of message registers used is determined by the `message_length` field.

### 2.5.2 Capabilities

seL4 uses capability-based access-control to hardware features. Capabilities are kernel-controlled objects that can be invoked, created, shared, and revoked [42, sec. 2.1]. Some capabilities have a guard or badge value, which is a simple word of varying length associated with the capability. In addition to this, rights fields are also held by some capabilities, which allow or disallow certain methods to be invoked. After introducing a capability of a certain name, we will refer to a [NAME] capability simply as [NAME].

#### Addressing Capabilities

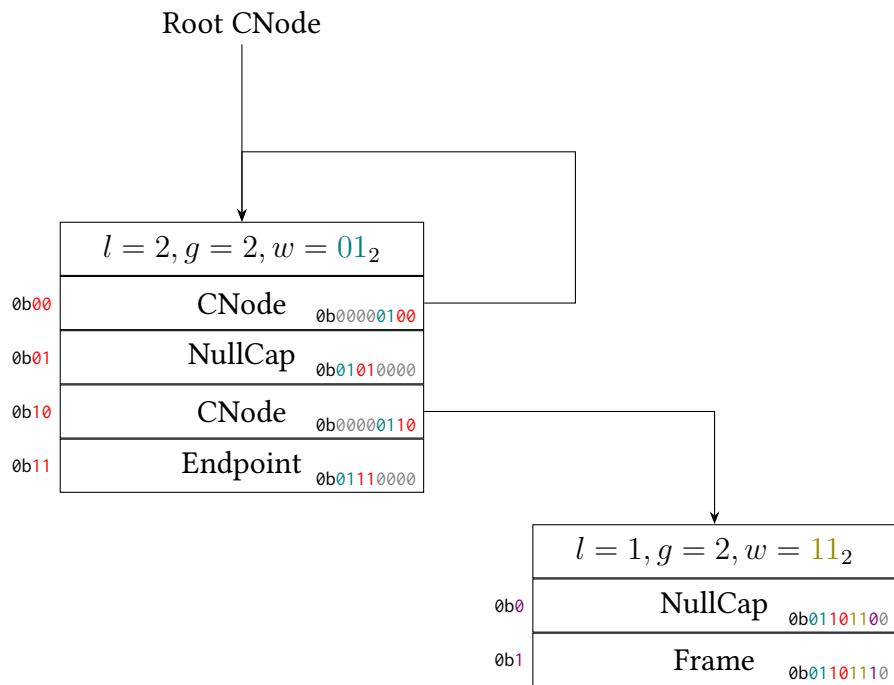

Since capabilities are kernel-controlled objects, user-space tasks cannot interact with them directly. Therefore, tasks need a way to address them. These addresses are called capability pointers (CPtrs) and are derived from a guarded page-table constructed by nested CNode capabilities. A CNode holds a list of capabilities,

which can again contain another CNode, which holds another list of capabilities. Every thread has a root CNode, which determines the set of all capabilities a thread can invoke, which is called the capability space (CSpace). It is used as the starting point when resolving CPtrs when no other root CNode is given for the invocation. A CNode capability  $c$  has a length  $l_c$ , a guard word  $w_c$  and a guard length  $g_c$ , which are used during the translation process.

The translation process also uses a *depth*  $d$ , which determines the bit position at which to start translating, starting from the least significant bit. The default value for  $d$  is the *machine word size*  $s$ , meaning the translation process starts with the  $s$ th least significant bit, which is the most significant bit. To resolve a CPtr for a given root CNode, the first  $g_{root}$  bits of the CPtr are checked against  $w_{root}$ , after which the next  $l_{root}$  bits are used to determine the index into the CNode's list. If the reached capability is another CNode and  $d > g_{root} + l_{root}$ , the process is repeated with the next CNode's  $g_{next}, l_{next}, w_{next}$  until, for the set  $C$  of traversed CNodes, either

$$t = d - \sum_{i \in C} g_i + l_i = 0$$

and a capability is found and returned, a *guard mismatch* occurs, or a non-CNode capability is reached while  $t \neq 0$ , which is called a *depth mismatch* [4, secs. 3.3-3.4]. A visual example of the translation process can be seen in Figure 2.3.

## Creating Capabilities

In order to create a new capability, a thread must invoke a capability-creating method. The initial task is given several capabilities for that purpose. The most common of these is the Retype method of the Untyped capability, which controls a portion of untyped physical memory. Retype can be used to create most capabilities, including memory-managing capabilities to frames or other memory-management structures.

As of seL4 13.0.0, capabilities on x86/64 have 128 bits of storage, some of which are reserved for shared fields, that can be used for rights managed and state-keeping. If a capability requires further memory, for example because it is managing a physical structure (e.g. paging structures), it is designated as a *physical* capability with an object of a certain size and consumes additional memory upon creation, which it needs to track by storing a pointer in the aforementioned storage bits. Physical capabilities need to be created via Untyped's Retype and consume part of the Untyped's memory.

Other capabilities, like the root-owned IRQControl capability, are used as rights-managers and can only be used to create new sub-capabilities to specific entities in the managed space. The sub-capabilities cannot have any memory

Figure 2.3: An example capability guarded page-table with word size  $s = 8$ . Capabilities have their simplest CPtr in their box on the right and the index for their containing list on the left. Values in gray are ignored. It is assumed that the proper *depth* is used for CNode addressing. Since CPtr translation follows loops, given the example that the CNode  $0b00000100$  has the same guard word and guard size as the root CNode, Endpoint can also be addressed with  $0b01000111$ .

associated with them, since the managing capabilities do not have associated memory to hand out and cannot be created via Untyped’s `Rtype`.

## Invoking Capability Methods

To invoke a capability, a thread has to set its message registers, which are housed in a special thread-local memory region, to contain the capability’s `CPtr`, method ID, and further arguments. After which it invokes the `Call` system call and control is handed over to the kernel. The kernel then retrieves the actual capability object and performs the method-specific actions, checking if the thread passed a correct capability with the appropriate rights along with other sanity checks. Return values are then passed back via the thread’s message registers and can then be decoded in user-space.

## Deriving Capabilities

Many capabilities can be *derived*, meaning a new capability is created from the original capability, either with different rights, a different badge or guard, which is called *minting* or simply *copied*. If the capability is a physical capability, derived capabilities refer to the same object. This is how shared memory can be implemented in seL4 [42, sec. 7.3], since a Frame capability can only be mapped once. The Frame is then derived and either placed directly in the recipient’s `CSpace`, or transferred via capability transfer, which we explain in §2.5.3, and then the derived capability is mapped into the recipient’s virtual address space (`VSpace`). Or the sender can map the capability directly into the recipient’s `VSpace` if they have access to their `PML4` capability, which is the `VSpace` root. Internally, seL4 keeps track of the derivation tree [42, sec. 3.1.5], so that when a capability is revoked or deleted, the derived capabilities (as well as the original capability in case of `Delete`) and the referenced object are deleted properly.

### 2.5.3 IPC Capabilities

IPC on seL4 is handled similarly to capability invocation. In fact, IPC is handled via capability invocation [42, chpts. 4, 5]. seL4 offers a capability for message passing and signals each, called Endpoint and Notification capability respectively. Endpoints are discussed in §2.5.3, while Notifications are touched on in §2.5.3.

## Endpoints

In seL4 an Endpoint represents the right to send or receive messages to and from the specific endpoint represented by the capability. An Endpoint has four different rights [42, sec. 3.1.4]:

- *Send*, which allows the holder to send data via the Endpoint

- *Receive*, which allows the holder to receive data via the Endpoint

- *Grant*, which allows the holder of the Endpoint to transfer capabilities

- *GrantReply*, which allows the holder of the Endpoint to transfer a Reply capability.

A Reply is a special kind of capability that is granted to the receiver of an Endpoint message and can only be used once. It is only used when the sender invokes `Call` with the Endpoint, which blocks the sender until the receiver sends a message on the received Reply. If an Endpoint does not have the *Grant* or *GrantReply* rights, the calling thread is simply suspended and needs to be manually restarted [4, sec. 4.2.4].

An Endpoint with *Grant* can also transfer other capabilities. For this, the receiver simply sets the CNode slot to save the new capability to and calls `Recv`. The sender places the CPtr in the designated array and calls `Send`. After a successful rendezvous, the receiver owns a copy of the original capability. For sake of scope we will not describe capability unwrapping, which is the mechanism used when sending more than one capability [4, sec. 4.2.2].

Since seL4 has no kernel-housed message buffer, both the sender and a receiver need to be waiting on the Endpoint at the same time. This means either the receiver must already be waiting with `Recv` when the sender uses (NB) `Send`, or the sender must already be waiting for the receiver with `Send` for a message to be successfully delivered. `NBSend` fails quietly if the message could not be delivered. In addition to the normal communication pathway, Endpoints also supports the *fast-path*, which is a highly optimized path through the kernel [43]. The fast-path is invoked if the following conditions hold true: 1. Endpoint was invoked with either `Call` or `ReplyRecv` 2. No thread with a higher priority is waiting to be scheduled 3. The message consists only of regular data and fits into the message registers. We categorize Endpoint messages as synchronous, with both blocking and non-blocking variants for `Send` and `Recv` [42, sec. 4.2].

## Notifications

A Notification represents an asynchronous signaling mechanism [42, chpt. 5]. The transmitted signal is the badge value of the Notification, which is saved

by the kernel until retrieved. Additionally, if a thread is already Waiting on the Notification, the first waiting thread is unblocked. There are three invocations for Notifications [42, sec. 5.3]:

- Signal, which sends a signal with the badge value

- Wait, which waits until a signal is received

- Poll, which maps directly to NBRecv and checks if a signal is pending and simply returns if none exist.

A single Notification can also be bound to a thread's TCB, which allows the thread to also receive a signal any time it calls Recv on an Endpoint. It is up to user-space to determine whether the message was a signal to the bound Notification or a message on the Endpoint. We categorize Notification messages as asynchronous, with both blocking and non-blocking variants for the receiver and only non-blocking Signal for the sender.

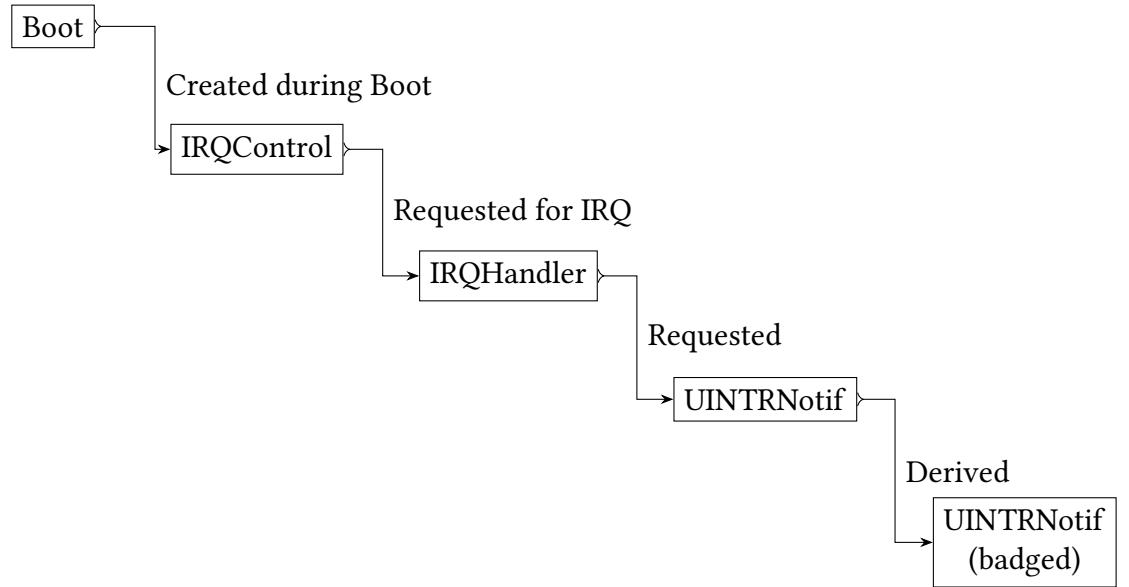

#### 2.5.4 Interrupt Handling

seL4 specifically uses two capabilities to control access to interrupt request lines (IRQs). The IRQControl capability is handed to the initial task and can then be used to create new IRQHandler capabilities. An IRQHandler can control legacy interrupts, IOAPIC interrupts, or MSI interrupts [42]. Which type of IRQHandler is created depends on the specific invocation used on IRQControl, which each type using a different method and parameters. Once an IRQHandler capability is created, SetNotification can be used to register a Notification to the IRQ, which can then be used to receive interrupts by calling Wait or Poll. Therefore, forwarding an interrupt to user-space is done via an asynchronous IPC mechanism and is not preemptive. Interrupts are acknowledged with IRQHandler's Ack, after which the next interrupt can be received with Wait.

# Chapter 3

## Related Work

In this chapter, we first provide a comprehensive overview of analyses on Intel’s UINTR feature (§3.1) to gauge its viability for use in  $\mu$ kernels as well as shed some light on potential limitations. The following section explores further work on applications of UINTR, most of which are user-level preemption. Lastly, we explore work related to IPC on  $\mu$ kernels as a potential sources for comparison and inspiration for our design (§3.3).

### 3.1 User-Level-Interrupts

This section takes a look at recent work on UINTR to provide a better understanding of its benefits and limitations. We first dive into some introductory work (§3.1.1), look at a security analysis (§3.1.2) and lastly into technical analyses of Intel’s UINTR (§3.1.3).

#### 3.1.1 Introductory Work

One of the first scientific works to use UINTR was an effort to replace the polling-based receive-mechanism of *NewMadeleine*, an event-driven communication library that allows asynchronous communication, with notifications based on UIPIs. For this, Goedefroit [44] uses Intel’s Linux patch to compare UIPIs and OSS and found that UIPIs have a lower and more consistent delivery latency than OSS, with a roughly  $3\times$  advantage. Goedefroit also finds that UIPIs is not unaffected by the non-uniform memory access (NUMA) layout, with UIPIs between distant cores being  $\sim 1.5\times$  slower, however, OSS are also affected by this, as mentioned in §3.3.4. In *NewMadeleine*, Goedefroit prepares both a notification mechanism for a shared-memory IPC system based on OSSs and UIPIs and shows that the UIPI driver has a slightly higher latency than a busy-waiting variant, but performs bet-

ter than OSS. These results are reflected in the new driver’s throughput, which is slightly lower than busy-waiting but still massively outperforms OSS. In essence, Goedefroit demonstrates that UINTR can provide tangible performance benefits compared to OSS while reducing the overhead ratio compared to busy-waiting. Goedefroit also submitted a pull request for a bug in Intel’s kernel patch related to the alt-stack feature.

### 3.1.2 Security Aspects

The first security analysis of UINTR provides insight into the characteristics of UINTR and IPI virtualization (IPIv), both features were introduced with Sapphire Rapids. Rauscher and Gruss [45] confirm the comparatively low latency of UIPI and use these characteristics to construct a covert channel, a keystroke detection mechanism and a website fingerprinting mechanism, all of which work under virtualization due to the new IPIv feature, which allows virtual machines (VMs) to send IPIs without supervisor intervention. Rauscher and Gruss highlight both the potential benefits and security risks of these new features, if used without mitigations. UINTR also need to be considered when implementing sandboxing mechanisms, as shown with Erebor [46].

### 3.1.3 Technical Analyses

Using reverse-engineering and fine-grained benchmarks, Aydogmus et al. [47] analyzed the detailed performance characteristics of UIPIs from the sender, receiver, and round-trip perspective. They find that receiving UIPIs flushes the instruction pipeline, which leads to a loss of throughput, according to them, unnecessary latency. Aydogmus et al. propose extended user-interrupts (xUI), with 4 aspects: 1. Tracked interrupts, 2. hardware safepoints, 3. kernel-bypass timers, 4. interrupt forwarding, all of which they implement and evaluate on simulated hardware. The most interesting to us are tracked interrupts, which promise to reduce UIPI latency by using draining instead of flushing together with branch mispredictions to dynamically inject UIPI micro-ops into the instruction stream at a potentially earlier point in time. Hardware safepoints would automatically enable or disable UINTR for applications instead of explicitly requiring the use of SETUI and CLUI instructions, while interrupt forwarding extends the UIN mechanism already provided by UINTR with dedicated support for multiple UDIs using two new 256 bit fields [47]. Kernel-bypass timers are also of interest to Intel, who have proposed their own user-timer system using UINTR which might be introduced with Clearwater Forest processors [34], potentially to mitigate the need for manual solutions such as the ones found in Skyloft [38].

The most recent technical analysis characterizes UINTR with a focus on virtualization. Kone et al. [48] look at UINTR’s general capabilities, trade-offs for potential software wanting to use UINTR and offer a unique perspective on the performance characteristics in a virtualized environment, both with IPIv enabled and disabled. For this, Kone et al. build a new set of benchmarks to compare UIPIs to OSS, with a custom function to read the TSC, `readtsc()`. In line with other previous work, Kone et al. find an increased delivery latency ( $\sim 1.3 \times$ ) depending on the physical placement of the sender and receiver threads for both native and IPIv-enabled systems, as well as a severe (up to  $\sim 2.6 \times$ ) delivery latency degradation under IPIv compared to a native system. However, they still prove that UINTR is a viable alternative to OSS in any case, as every UINTR operation outperforms its OSS counterpart, especially the sending operation, which is up to  $\sim 25 \times$  faster and scales exponentially better under contention.

As a potential use-case for UINTRs, Kone et al. develop a user-level scheduler, *Christine*, which will be further discussed as part of section (§3.2.1).

## 3.2 Applications of UINTR

Following the technical aspects of Intel’s UINTR, we introduce literature that focuses on analyzing UINTR in different use-cases. The most common use-case is user-level preemption to implement user-level schedulers. Work focusing on this is discussed in §3.2.1, while §3.2.2 touches on work focusing on other applications.

### 3.2.1 User-level Preemption with UINTR

An early work using UINTR is a user-level threading library for cloud applications by Li et al., called *LibPreemptible* [49]. Li et al. use UINTR to construct a user-level timer – their implementation of which is called *LibUtimer* – that provides regular interrupts to threads by having a dedicated timer thread poll on thread-based deadline set in memory. Once a deadline is reached, *LibUtimer* sends a UIPI to the offending thread, which triggers a context switch via the interrupt handler. *LibPreemptible* can implement various scheduling policies and dynamically change time-slice quanta. This results in a flexible scheduler that can achieve better tail-latency and higher throughput than the state-of-the-art scheduling system of the time, Shinjuku [50].

Shortly after, Fried et al. present *Junction* [51], a kernel-bypass system for the cloud. Similar to *LibPreemptible*, *Junction* also uses UIPIs from a separate scheduler core to preempt its user-level threads and provide an equal workload distribution. They find that UIPIs reduce the timeslicing overhead by  $\sim 2 \times$  when

compared to OSS, which allows for higher time slice granularity, which in turn provides a potential avenue for reducing tail latency in  $\mu$ second scale workloads, as demonstrated with *LibPreemptible*. In addition Fried et al. find that, for saving the extended processor state in the interrupt handler, the `XSAVEC` instruction is as fast as `XSAVEOPT`, while being easier to use correctly.

*SkyLoft* [38] is a user-level scheduling framework, which can support multiple applications, instead of just threads within the same application. Its use of UINTR differs to previous work by being the first published work to enable UINs for hardware timers. As native support for user-space timers and proper hardware interrupt notifications are still in development [34, 52], this is not entirely trivial and requires manually setting a bit in the `PIR` field of the `UPID`, so the hardware interrupt actually triggers `UID`. Jia et al. solve this by sending a self-UIPI while UINs are suppressed in the interrupt-handler and at setup, setting the bit without causing `UID` until the next hardware timer interrupt arrives. Even with this additional overhead, Jia et al. find that hardware timer notification are still faster than dedicated user-level timer cores sending UIPIs.

While UINTR is not the main focus of their publication, Lin et al. [53] use UINTRs in combination with MPKs to create a user-space core scheduler, called *Vessel*, which uses a user-level privileged mode to separate address spaces between threads in user-space, called a *uProcess*. Lin et al. use UINTRs to preempt different *uProcesses*, which then transition into the user-space privileged mode via protected call gates. Once the core is in the privileged state, it switches its address space, scheduling a new *uProcess*. *Vessel* is used to co-locate different types of applications to the same core, while providing an increased throughput for both latency-critical and best-effort applications when compared to contemporary solutions, with UINTRs being a key technology for these results.

Guo et al. [54] compare OSSs to UINTR as a preemption mechanism in two different user-level schedulers, one based on *Caladan*, a kernel-bypass system, and another based on the Go runtime. They compare UINTR-based and OSS-based preemption to compiler instrumentation, with which a compiler inserts regular yield checks for cooperative scheduling, and find that the decreased overhead with UINTR is inconsequential for application performance with larger time quanta, while being at least on-par with compiler instrumentation for a  $10\mu$ s quantum. OSS, as also shown in previous work, perform less favourably. However, the schedulers' average preemption cost with UINTR is significantly lower than that of compiler-instrumentation. Guo et al. find UINTR “are not a panacea”, but have some useful applications, such as  $\mu$ second scale preemption. In addition, they find that, compared to OSSs, using UINTRs leads to fewer L1 cache misses and branch mispredictions. In regard to context switches, Guo et al. find that saving the AVX-512 registers with `XSAVEC` incurs a  $\sim 10\text{-}30\times$  overhead compared to saving the registers one-by-one.

As a further application of user-level preemption, Huang et al. [55] introduce UINTR to database engines with *PreemptDB* and compare UINTR-based user-level preemption to waiting, hand-crafted, and automatic cooperative scheduling. *PreemptDB* uses preemption to suspend low-priority transactions when new high-priority transactions are queued. While doing so, Huang et al. recognize the need for atomicity in their context switch routine, which can be called outside of interrupt handlers. To achieve this, the context switch routine temporarily disables UID and includes instruction pointer checks to ensure that the currently handled interrupt was not delivered while inside the context switch. *PreemptDB* with UINTR provides lower latency for high-priority tasks while maintaining throughput and requires no specific tuning.

Finally, the user-level scheduler by Kone et al. [48] – *Christine* – is used to compare and document differences between UINTR and OSSs in both native and virtualized systems to document the extent to which UINTR can reduce tail latencies. Similarly to *LibPreemptible*, Kone et al. use a dedicated timer thread to busy-spin and call their custom `rdtsc()` function. Kone et al. additionally implement worker synchronization to ensure workers are not spending their entire time in the scheduling routine due to an insufficient time quantum. *Christine* predictably has degraded performance in every metric under virtualization, while showing that UINTRs are capable of supporting a more precise, stable and focused scheduler at smaller timer quantum sizes than OSSs.

### 3.2.2 Other Applications of UINTR

Li et al. [56], similar to Jia et al. use self-UIPIs to receive hardware interrupts over the UINTR mechanism. They use this to modify *SPDK*, a I/O storage software, which can either use a polling thread to check for hardware availability or receive and handle MSI-X interrupts via the kernel. Their modifications result in a two-thread user-level threading framework, which switches between an idle-thread executing `TPAUSE` and the actual worker thread, depending on whether the thread is waiting for the I/O operation interrupt, redirected via the IOMMU to the UINV, or not. *SPDK+* achieves a similar latency to the original polling method, while also achieving slightly better power efficiency than both the original polling and interrupt method. Li et al. predict even higher efficiency for increased core counts.

Goedefroit continued their work on applying UINTR to the BXI network [57]. Most importantly for us, Goedefroit et al. found a way to trigger a UINTR directly from a PCIe device by combining the posted interrupt descriptor (PID) structure of IOMMU interrupt redirection with the UPID. While useful for avoiding unnecessary interrupt-management via self-UIPIs, it requires mapping the UPID/PID-union to user-space, which would allow malicious software to trigger arbitrary

interrupts using SENDUIPI, as we already discussed in §2.4.5. Goedefroit et al. find that UINTR are slower than polling but provide a decent communication/- computation overlap, which makes it a good tool for use in high performance computing applications, in line with Goedefroit’s previous findings [44].

Similar to Goedefroit et al., Li et al. [58] found their own way to circumvent the self-UIPI in order to receive hardware interrupts in their UINTR-based storage system *Aeolia*. Instead of having hardware set the required PIR field, they set the PIR field themselves by mapping the UPID into their user-space driver’s memory, effectively emulating the mechanism self-UIPIs are used for in previously presented work. *Aeolia* therefore suffers from the similar security issues as Goedefroit et al. when it comes to the triggering of arbitrary interrupts.

### 3.3 IPC on Microkernels

With the clear potential of UINTR in µkernel IPC highlighted in the previous sections, we look at some other recent work in this field. We take a closer look at the “Bridge”-family of IPC mechanisms, starting with SkyBridge (§3.3.1) and continuing along the line of advancements with UnderBridge (§3.3.2) to the most recent representative, HyBridge (§3.3.3). We end the section with a short look at other IPC-related work (§3.3.4).

#### 3.3.1 SkyBridge

SkyBridge is another new IPC mechanism, this time specifically designed for µkernels. It uses the VMFUNC instruction to bypass the kernel and directly call code from other processes by switching the extended page tables (EPTs) of the client and server when the client wants to invoke a server function. For this, servers register with the kernel to map function entry points to a table, which a registered client can then use to call server functions via a library call. To keep unauthorized processes from executing VMFUNCs, switching EPTs and calling server functions without permission, SkyBridge utilizes binary rewriting when mapping code pages. For actual message passing, SkyBridge uses shared buffers for large messages and registers, complying with the x86/64 calling convention, for small messages. SkyBridge achieves a  $\sim 2\text{-}10 \times$  round-trip-time advantage compared to the default IPC methods [59].

#### 3.3.2 UnderBridge

The successor to SkyBridge, UnderBridge, instead circumvents cross-server IPC overhead entirely by moving system servers back into the kernel. Since the

kernel has a shared state, cross-server IPC skips context switches and kernel-controlled argument validation. UnderBridge can therefore be seen as a new form of kernel-bypass, but communication between servers needs new isolation and protection mechanisms to remain secure. In addition to this, servers can now execute privileged instructions, potentially endangering the entire system if faulty. UnderBridge achieves isolation via MPKs, which creates isolated *execution domains* for each server in kernel mode. Execution domains consist of code segments, stored in the core kernel protection domain with read-only access, and data segments, stored in their own protection domain to which they have full access. Cross-server communication is handled via IPC-gates installed in the code-domain and a shared memory domain for each communication channel, other channels are handled via shared memory pages with the core kernel or client. Since MPKs only support 16 different protection domains, servers are dynamically migrated between user- and kernel-space as needed if the maximum amount of protection domains is reached. Privileged instructions are removed via binary rewriting and trapped by introducing a hypervisor which ensures privileged instructions are only executed by the core kernel. These measures prevent malicious system servers from intentionally modifying or compromising the core kernel. UnderBridge, despite having a worse base-case of 0 cross-server IPC on client-server IPC, scales much better and therefore reaches parity and even surpasses SkyBridge at 1-2 cross-server IPCs per client-server call. This leads to a  $\sim 1.5 \times$  throughput advantage in the SQLite3 benchmark compared to SkyBridge [6].

### 3.3.3 HyBridge

HyBridge further enhances UnderBridge by increasing the amount of available isolation domains by combining MPKs with EPTs, calling the combined mechanism extended protection keys (EPKs). By observing that MPKs and EPTs are both thread-specific values, it assigns each of the 512 EPT the 15 available domains with MPKs, leading to 7680 possible memory protection domains. This allows EPKs to massively outperform software-based multiplexing solutions for EPKs on Linux and eliminates one of the major downsides of UnderBridge by allowing HyBridge to move every system server into kernel space instead of just a few. Cross-Server communication is unchanged from UnderBridge, but client-server communication now utilizes a EPT switch via VMFUNC instead of a regular context switch to kernel. This allows HyBridge to achieve throughput parity in the SQLite3 benchmark with UnderBridge, while surpassing it in most cases [7].

### 3.3.4 Other work

We end this section with a draft on IPC benchmarking, which finds, by testing IPC latencies on different OS's in virtualized and native environments, that an observable part of IPC latency is affected by the NUMA layout [60], which will be relevant for later sections and would also affects a new IPC implementation for multi-core systems on  $\mu$ kernels, which uses shared memory and regular IPIs on ARM to implement a inter-core IPC and notification utility on its own  $\mu$ kernel [61].

# Chapter 4

## Design

This chapter details the design for our implemented system, which is a new IPC facility on L4 µkernels using the new UINTR feature in conjunction with the user-wait extension. Given that previous research on UINTR proved its usefulness as a replacement for OSS on Linux, we intend to see if UINTR may also have a place in the realm of µkernels. Due to the differences between L4 and Linux, we first introduce our design for UINTR on our chosen kernel in §4.1, as we could not simply port Intel’s Linux patch.

If this kernel-bypass mechanism can be used to implement most IPC facilities with potentially improved performance compared to already existing facilities, introducing UINTR as a core of modern µkernels design could align the next generation of µkernels to have an even smaller TCB, further reinforcing the tenets mentioned in §2.1.3. With this in mind, we explain our design for our IPC library in §4.2.

### 4.1 Capability-based User-level Interrupts

We first explain some of our initial thoughts and approach in §4.1.1, after which we illustrate our capability-based designs for UINTR objects in §4.1.2.

#### 4.1.1 Initial Approach

We initially intended user-interrupts to be configured by a server, which receives requests from clients to establish UINTR-based connections between server-clients and client-clients to allow for RPCs. Server-clients would advertise their API via the server, where client-clients would then request access. They would then be handed the appropriate permissions or tokens and the server would set the