# Towards Heterogeneous Deterministic Replay for Symmetric Multiprocessors

Masterarbeit von

# Michael Zangl

an der Fakultät für Informatik

Erstgutachter: Zweitgutachter: Betreuender Mitarbeiter: Prof. Dr. Frank Bellosa Prof. Dr. Wolfgang Karl Marc Rittinghaus

Bearbeitungszeit: 1. Juni 2017 – 12. November 2017

Ich erkläre hiermit, dass ich die vorliegende Arbeit selbständig verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel verwendet habe.

Karlsruhe, den 12. November 2017

iv

## Abstract

A program can be recorded and then deterministically replayed. This is used for debugging applications and detecting the cause of bugs or errors after they were observed.

During recording, all non-deterministic events are stored for later replay. Upon replay, this allows the program to behave exactly like the recording, down to the instruction level. A detailed analysis of the program is possible during replay. To improve the analysis results, it can be done in a different environment than the recording while preserving the exact instruction flow.

In this master thesis, the ability to extend a heterogeneous record and replay system with multi-core support is evaluated. To make memory race conditions deterministic, a chunk based protocol is evaluated with which a transactional memory is simulated in the hypervisor. No hardware modifications are required for this.

A prototype is implemented based on QEMU that records a virtual machine and replays the recording in an emulator. It is shown that recording on a virtual machine causes low memory overhead and acceptable performance overhead. The scalability of the system is shown to be good for processor numbers that are currently used in virtual machines, although for high numbers of processors this solution does not scale. It is validated that a correct replay is possible in an emulated environment.

ABSTRACT

vi

# Contents

| Abstract Contents |              |          |                                  |   |    |  |  |   |              |

|-------------------|--------------|----------|----------------------------------|---|----|--|--|---|--------------|

|                   |              |          |                                  |   |    |  |  | 1 | Introduction |

| 2                 | Background 5 |          |                                  |   |    |  |  |   |              |

|                   | 2.1          | Virtuali | ization                          |   | 5  |  |  |   |              |

|                   |              | 2.1.1    | Software Emulation               |   | 5  |  |  |   |              |

|                   |              | 2.1.2    | Hardware Assisted Virtualization | • | 7  |  |  |   |              |

| 3                 | Analysis     |          |                                  |   |    |  |  |   |              |

|                   | 3.1          | User-S   | pace Record and Replay           |   | 11 |  |  |   |              |

|                   | 3.2          | Full Sy  | stem Record and Replay           |   | 12 |  |  |   |              |

|                   |              | 3.2.1    | Emulation                        |   | 12 |  |  |   |              |

|                   |              | 3.2.2    | Virtualization                   |   | 13 |  |  |   |              |

|                   |              | 3.2.3    | Heterogeneous Record and Replay  |   | 14 |  |  |   |              |

|                   | 3.3          | Multico  | pre Record and Replay            |   | 15 |  |  |   |              |

|                   |              | 3.3.1    | Software Memory Tracing          |   | 15 |  |  |   |              |

|                   |              | 3.3.2    | Hardware Assisted Memory Tracing |   | 17 |  |  |   |              |

|                   |              | 3.3.3    | Virtualized Memory Tracing       |   | 19 |  |  |   |              |

|                   | 3.4          | Conclu   | sion                             | • | 20 |  |  |   |              |

| 4                 | Design 21    |          |                                  |   |    |  |  |   |              |

|                   | 4.1          | Record   | ing                              |   | 21 |  |  |   |              |

|                   |              | 4.1.1    | Initialisation                   |   | 21 |  |  |   |              |

|                   |              | 4.1.2    | Processor Events                 |   | 22 |  |  |   |              |

|                   |              | 4.1.3    | Chunk Based Commit Protocol      |   | 23 |  |  |   |              |

|                   |              | 4.1.4    | Direct Memory Access             |   | 29 |  |  |   |              |

|                   |              | 4.1.5    | Checkpointing                    |   | 30 |  |  |   |              |

|                   | 4.2          | Replay   |                                  |   | 31 |  |  |   |              |

| Bi | Bibliography 6    |         |                                |      |  |  |  |  |  |

|----|-------------------|---------|--------------------------------|------|--|--|--|--|--|

| 7  | Conclusion        |         |                                |      |  |  |  |  |  |

|    | 6.4               | Conclu  | ision                          | . 59 |  |  |  |  |  |

|    |                   | 6.3.2   | Memory Consumption             |      |  |  |  |  |  |

|    |                   | 6.3.1   | Performance                    |      |  |  |  |  |  |

|    | 6.3               | Scalabi | ility                          |      |  |  |  |  |  |

|    | 6.2               | Validat | ion                            | . 53 |  |  |  |  |  |

|    |                   | 6.1.1   | Analyzing the Scenarios        |      |  |  |  |  |  |

|    | 6.1               | Evaluat | tion Scenarios                 | . 49 |  |  |  |  |  |

| 6  | Evaluation 49     |         |                                |      |  |  |  |  |  |

|    | 5.5               | Conclu  | ision                          | . 47 |  |  |  |  |  |

|    |                   | 5.4.2   | Replay the Chunks              |      |  |  |  |  |  |

|    |                   | 5.4.1   | Restoring the Initial State    | . 46 |  |  |  |  |  |

|    | 5.4               | Replay  | ′                              | . 46 |  |  |  |  |  |

|    |                   | 5.3.7   | Stopping the Recording Session |      |  |  |  |  |  |

|    |                   | 5.3.6   | Ending a Chunk                 |      |  |  |  |  |  |

|    |                   | 5.3.5   | Capturing Memory Access        |      |  |  |  |  |  |

|    |                   | 5.3.4   | Recording Events               |      |  |  |  |  |  |

|    |                   | 5.3.3   | Processor Memory Access        |      |  |  |  |  |  |

|    |                   | 5.3.2   | Starting a Recording Session   |      |  |  |  |  |  |

|    |                   | 5.3.1   | Creating an Initial Checkpoint |      |  |  |  |  |  |

|    | 5.3               |         | ling                           |      |  |  |  |  |  |

|    |                   | 5.2.3   | Event Log                      |      |  |  |  |  |  |

|    |                   | 5.2.1   | Memory Access Maps             |      |  |  |  |  |  |

|    | 5.2               | 5.2.1   | Page Set                       |      |  |  |  |  |  |

|    | 5.1<br>5.2        |         | Protocol Data Structures       |      |  |  |  |  |  |

| 5  | <b>Imp</b><br>5.1 | 1       |                                |      |  |  |  |  |  |

| =  | Imm               |         |                                |      |  |  |  |  |  |

|    | 4.3               | Conclu  | ision                          | . 33 |  |  |  |  |  |

|    |                   | 4.2.2   | Chunk Ordering                 |      |  |  |  |  |  |

|    |                   | 4.2.1   | Initial state                  | . 31 |  |  |  |  |  |

# Chapter 1 Introduction

Debugging programs often requires to go back in time and to trace the real cause of an error. This can be the case for a normal program bug that is only recognizable by the errors it causes in the following program execution. In this case, finding the source of it is difficult. It may be useful to re-execute the program and trigger the bug again. But reproducing the bug is not always possible for the user, since small differences in program execution may lead to the bug not being triggered. The same way, finding the entry path into the system of malicious applications proves difficult, since those programs can alter system logs and other information after they have infected a system. Once the user realizes that such a malicious application is or was on the system, it may not be possible any more to find out where it came from and what the application did. A record and deterministic replay system that records the running system and then allows to re-simulate the execution down to the instruction level can be used to debug such defective or malicious applications [4].

When recording a system, all non-deterministic events are captured. They are written to a log which is used during replay to make the replay deterministic. To allow for high performance record and replay, hardware support can be used for recording. This is done using virtualization extensions of modern CPUs and running the system that should be analyzed as a virtual machine. During replay, the same hardware and the same environment can be used in order to ensure correctness [10, 19].

But software emulation allows for a more detailed program analysis than hardware virtualization [4]. So to allow the recording to be run in background with high performance while having powerful tools to analyze it, a heterogeneous approach can be used. The recording of the system is done in a virtualized environment while the replay is done in an emulator.

For single-core systems, this has been implemented in V2E [24]. But modern processors have multiple processors to increase performance through parallelism.

When executing programs in parallel, new problems occur. A common problem are memory race conditions. Small differences in the time at which instructions are executed on different cores may cause differing program results, including crashes. Those problems cannot easily be reproduced since they do not occur deterministically. To analyse them, record and replay can be used as well. This is why a record and replay solution should support tracing and replaying multiple processors. Such a multi-core record and replay has not yet been implemented in a heterogeneous environment. Evaluating the possibility of such an implementation will be the scope of this work.

4

# Chapter 2

# Background

This work is on recording and replaying applications in virtualized environments. For this, the a basic knowledge of virtual environments is required. Special attention is on the support for multiple processors and memory synchronization, since this will be one key aspect of this work.

### 2.1 Virtualization

Originally, an operating system is meant to run on the bare hardware. The operating system expects to have full control over the hardware. This prevents multiple operating systems from running in parallel.

For debugging purposes, it is often required to pause an operating system and to access it's memory. In this case, there needs to be an mechanism that takes care of the hardware in those situations. One solution to this problem is to run an other operating system on the hardware and then run the system that should be analyzed in a virtual, simulated environment.

### 2.1.1 Software Emulation

An emulator is a software that simulates a the complete computer hardware. It allows the user to specify virtual IO devices like a serial console or a hard drive that this computer then uses. The emulator then simulates a system start from that hard drive. All instructions the CPU would execute to do this are interpreted in software.

This full system emulation allows a operation system and normal applications to be run inside the emulator without any modification. The program behaves exactly as it would on a real system. Since the emulator is written in software, it can be instructed to perform additional operations in addition to simply running the program. This includes debugging the application by pausing on a specific breakpoint. The current state of the emulated CPU can then be inspected, including all register contents and the hardware state. That way, full systems can be debugged without the need for hardware debuggers.

The emulator can even do more complex operations like tracing all memory accesses and analyzing them.

The big advantage of software emulators is their flexibility and the ability to run any target architecture on any host architecture. An example for such an emulator is QEMU running in the TCG mode [3].

#### **Multi-core Emulation**

There are two approaches to emulate multi-core applications.

The first approach is to run the processors in sequence and frequently switch between them [3]. This approach is known from classic multi tasking applications. From a guest application point of view, all processors make progress. Since the guest system usually does not expect an exact timing of the inter processor communication, it will still work as it normally would on a full parallel system.

The switch may not happen during instructions that are considered atomic on the emulated platform. A memory write of an 64 bit word is an example for such an instruction on 64 bit systems. The emulator might need several native instructions to emulate this write. During those instructions, the memory state may only be half updated. To prevent this, a switch between processors is only possible at the end of such instructions.

Since the emulator has full control over the environment, this is not a problem in practice. The emulator does not rely on external interrupts to do the switch but it can instead use an internal counter that counts the instructions executed on the current core. It can switch to an other core after executing a given number of instructions.

If the switch is not frequent enough, programs that rely heavily on inter processor communication may be behaving differently. A spin lock for example may block the program execution by a long time until the emulator switches to the processor holding the spin lock. That way, real parallel program execution cannot be emulated reliably.

An alternative to the sequential emulation is to emulate all processors in parallel on different host processors. [6, 8] For this, each host processor is emulating one target processor. The host processors use the inter processor communication mechanisms of the host to simulate inter processor communication of the emulated system.

#### 2.1. VIRTUALIZATION

Special care needs to be taken for memory accesses. Memory accesses on the host system may not have the same granularity as the ones on the target system. This may require the host system to use special locking in order to guarantee the atomic instructions of the guest system to be atomic on the host system.

The emulator state synchronization needs to be taken care of as well. Pausing the emulator to analyze it's state requires to pause all processors simultaneously. This requires a special management layer for the emulator in which it manages the processors and pauses or resumes them as needed.

**Emulation Performance Optimizations**

While software emulation allows for an exact simulation of the target system, it has a major disadvantage in speed. CPUs can perform complex operations in one cycle. To simulate those operations, multiple CPU instructions on the host system may be required. Emulating hardware access adds additional CPU time which would not be required on the target system. This is why software emulation is significantly slower than natively running the program.

There are various optimizations available to counter this. The most important one is a just in time compilation of the guest code. The code is not interpreted but instead dynamically translated to machine code for the host system. Using this method, a program still needs several times longer to run than it would natively. [3]

An other major performance disadvantage of software emulation is the access to hardware. System hardware runs in parallel to the main processor. The program flow of a normal program can continue while the hardware is doing work. A software emulator needs to emulate this hardware. This simulation is done in software and is thus running on the CPU. Therefore, the CPU cannot continue to emulate the guest program.

To improve this situation, the hardware access can be translated instead of emulated. It then uses the resources of the host hardware and allows the CPU to continue with the guest program. This makes hardware accesses - like disk reads - asynchronous on the emulated system. While this is the same behavior as on the host system, it is an unpredictable behavior since the hardware access time is not deterministic.

#### 2.1.2 Hardware Assisted Virtualization

While software emulation allows for a lot of flexibility, it has the major disadvantage that it is several times slower than native execution. To avoid this issue and allow for a new native performance when using virtualisation, hardware manufacturers added virtualisation support. This allows to run unmodified guest systems directly on the host processor.

Those hardware extensions allow the guest operating system and it's application to use the CPU. The virtual memory layout can be controlled by the guest system, although it does not have complete access to the physical memory.

The part of the host system that controlls the virtual machines is called the hypervisor. From a user perspective, it can be used in a similar way the emulator is used to run the guest system. Instructions that operate on the virtual memory can run without the interference of the hypervisor. When the guest operating system accesses hardware, the hypervisor needs to filter the request to emulate a real hardware access as if the guest operating system was running directly on the hardware.

Hardware virtualisation requires the guest program to use the correct instruction set architecture for the processor. It is not possible to run programs that were compiled for other architectures.

#### **Guest Memory Access**

While the guest system is running, will use instructions that access the main memory. The guest system should have it's own, isolated memory area with contiguous addresses starting at 0 for this.

If the guest would be given direct access to the host memory, this would lead to conflicts. Therefore, a translation layer is added that translates between guest physical and host physical addresses.

On modern systems like the Intel processors with virtualisation extensions, this is done by mapping the memory addresses on a page granularity level. A page table like the one for normal applications is used to map the addresses.

This table is called the extended page table (EPT). It is set up and controlled by the virtual machine monitor. The guest can itself use the normal page table to isolate it's applications, which leads to a two level address translation as shown in Figure .

The guest operating system itself uses page tables to distribute the guest physical memory among it's processes. This lads to a two level translation in which the virtual address of the guest process is mapped to the guest physical address first and then to the host physical address, as described in Figure 4.1. Non-virtualized processes running directly on the host do not need this two stage address translation. For them, the extended page table is not used.

The flags of the EPT and the guest page tables are independent from each other. If the guest accesses a page, the corresponding access flags of both tables are set. The guest handles the access flags in it's page table. Since the EPT cannot be seen by the guest, the access flags of the EPT can be evaluated and reset by the host. The same applies to the dirty flag on page writes. In the Intel implementation of the EPT, the access flags are set hirarchically on all page table levels. The dirty flag is only set on the last level of the EPT.

The EPT has read, write and execute flags as well. When a guest attempts

Figure 2.1: The memory addresses of guest applications are mapped to the guest physical address. This memory address is then mapped to the host physical address. Hardware can provide full support for this two stage process.

to perform any operation on a page, those flags are evaluated in the guest page table first. If a violation is detected by the hardware, the processor traps. This trap is forwarded to the guest operating system to handle the page fault. After the permission tests for the guest page table have passed, the flags in the EPT are evaluated. If there is a violation in those flags, the host operating system needs to handle that page fault. It can then fix that corresponding page table entry and re-evaluate the page table miss to provide a page to the client or it can emulate an invalid memory access as if the guest would have accesses a non-existing physical address.

Current hypervisors like KVM are built to run unmodified guest operating systems. Those systems expect to have a contiguous memory starting at an address near 0 and ending at a fixed size. This is why those hypervisors are designed to give the guest system a large, contignuous block of memory. This restricts the largest guest physical address to the total amount of memory given to that guest.

However, as virtualisation becomes more common, alternative approaches use the flexibility of not running directly on the hardware to give sparse memory to the guest system. This allows the guest to make use of the full set of theoretically available physical addresses on modern systems. [2]

#### Trapping

Whenever the hardware is not able to directly handle an instruction the guest system executes, it traps into the hypervisor. The hypervisor is then able to handle this instruction of the guest system.

Most instructions a guest application executes do not trap and can completely be handled by the hardware. This includes memory accesses and some accesses to machine specific registers.

Hardware accesses cannot be handled by the hardware itself directly because there may be many guest operating systems running in parallel. This is why every access to the hardware traps into the hypervisor. The hypervisor can then decide to pass the request on to the real hardware or to emulate the hardware feature.

An example for this is network traffic: If a guest wants to send a network package, it communicates with a virtual network device. That device is simulated by the hypervisor. As soon as the guest instructs that virtual device to send the package, the hypervisor decides whether to pass it on to the real network interface or to handle the send request internally and e.g. send it on to an other virtual machine.

An other emulated instruction is the CPUID instruction. This instruction allows to get the id of the current core. Since a guest application can have a different view of the cores and this view should be transparent to the guest, the id given to the guest needs to be determined by the hypervisor. It returns the id of the virtual CPU (vCPU) in this case.

# Chapter 3

# Analysis

The more complex applications get, the more complex it gets to reproduce errors and trace the source of errors. To debug such an application in which erroneous or malicious behavior was observed, a record and replay approach can help. Using this, the application is recorded. The recording can then be executed again to observe and analyze the exactly same program behavior.

### 3.1 User-Space Record and Replay

Conventional debuggers allow the user to set breakpoints to pause the program on a specific condition. The program can then be inspected and the execution can be resumed. They only allow the user to see the current program state and then to go forward in time. It is not possible to go back in time. If an error did not directly trigger the breakpoint but only the later effects of the error did, the cause of the error cannot be examined any more.

A solution to this problem is to find a test case that always triggers the error and then to run this test case and set breakpoints earlier in the instruction flow.

For modern, complex software, not all bugs can be reproduced. This especially applies to fuzzing, a modern testing method in which the program is fed with random input and the program behavior is examined. If a fuzzer triggers a race condition or any other rare problem, the error may not happen in the next run even if the same input parameters are used.

For this, developers require debuggers that can go back in time [4, 15]. Such debuggers allow the analysis of a previous program state. They record a program by storing the initial program state. The debugger then stores every nondeterministic behavior of the application. That way, the debugger can replay the exact program flow starting at a program start or a checkpoint. To go back in time, the debugger restores the last checkpoint before the desired time frame and then replays the program until the desired state is reached.

One of those user-space record and replay systems is Jockey [21]. It runs on an unmodified Linux by linking it into an existing binary. It then intercepts all library calls of that binary that are non deterministic. On a Linux system, those are the wrappers for system calls. All other program execution is expected to be deterministic. This limits Jockey to single-core applications that do not use any form of shared memory and that do not receive external signals.

The problem with receiving asynchronous events like signals is that they need to be replayed at the exact same time they occurred during recording. A user-space recording library has no possibility to record an exact time reference at which the signal occurred. This prevents an exact insertion of the signal in the replay stream.

The second problem that Jockey faces is with concurrent memory access. If there are multiple threads in the running program or if there are multiple processes working on a shared memory segment, the order in which they access the shared memory must be recorded to make a deterministic replay possible. This requires context switches to be recorded. This would only be possible for a user-space, non-preemptive threading library. Any preemptive thread switch would be an asynchronous event that cannot be recorded in user-space.

Recording multiple processes at once and recording their interactions or even recording a whole operating system is not possible, since there is no shared timing information between the processes. That way, no synchronization during replay is possible and each process could only be replayed independently.

### 3.2 Full System Record and Replay

An alternative to recording only a single process is to record the whole system that process runs in. Such a recording would include the process itself but would also allow to debug it's operating system interactions and the communication with other processes. This has the advantage that it is more platform independent since it does not rely on a target application interface. In addition to this, it may cause a lower overhead since there is no need to include the contents of inter-process communications or the communication between a process and the operating system.

#### 3.2.1 Emulation

An emulator allows the implementation of record and replay relatively easily. Since the emulator is completely simulating the target system, it has full control over it. All interrupts are triggered by the emulator and all communication of the target system is doen through the emulator.

#### 3.2. FULL SYSTEM RECORD AND REPLAY

A naive approach would be to let the emulator record every single instruction it executes. This would lead to a very big log file and a lot of logging overhead. Therefore, instructions that are fully deterministic given the current emulator state do not need to be recorded. This includes instructions that read or write normal memory, arithmetic instructions and branching instructions.

For recording an emulated system, all actions of the emulator that do not depend on the current target state only need to be logged. This includes the times at which the emulator decides to trigger an interrupt vector and the results the emulator returns for IO operations that are mapped to external hardware like network cards.

During replay, the interrupts are then inserted at the same place in the instruction flow. Since the emulator has full control over the target and emulates every single instruction, it can count the instructions to determine the right place to insert the interrupt.

Other events that were synchronous to the target execution are triggered by it in the replay at exactly the same time as they were during recording. For those events, the resulting operation of the emulator is read from the log. That way, the replay behaves exactly as the recording system did.

#### 3.2.2 Virtualization

The problem with emulators is that they are slow in comparison to running the program on the original hardware. To trigger rare bugs that would require a replay mechanism to reproduce them, the program needs to run a relatively long time. It would even be best to run the recording in a production environment to be able to trace bugs in production. Using an emulator there is not an option, since the slowdown would severely reduce the throughput of the production system.

To get a performance close to a system that is running natively on the hardware, virtualization can be used. A virtualized system can be recorded at low memory overhead and a speed close to the one without recording [10, 23]

An additional disadvantage of emulators is that malware often contains mechanisms to detect an emulator and refuses to work in this environment. Virtualized environments are used for web servers, so malicious software often targets those environments. Therefore, no preventive measures against virtual machines are implemented in many such applications [7].

In a virtualized environment, the hypervisor manages all communication of the virtual machine with the outside world. If designed correctly, the hypervisor is the only source of indeterministic behavior of the virtual machine. Therefore, no modifications to the guest system are necessary to be able to do a full system record and replay. During recording, a sequential log of hypervisor events is generated. Those events record the non-deterministic input values and the timing and values of nondeterministic events. Hardware performance counters are used to count the number of instructions the virtual machine executed. That way, the exact time of asynchronous events can be recorded.

Since all asynchronous events are delivered by the hypervisor by default, there is no additional interrupt or other hardware interception required. The event can directly be stored by the hypervisor in it's memory space. This allows a recording overhead of approximately 5% on typical workloads [23].

During replay, the virtual machine is restored to the initial state. Then, it is resumed. Since the virtual machine state is exactly the same as during the recording, all future events are guaranteed to happen at exactly the same state during replay. Whenever the virtual machine makes a synchronous call that involves the hypervisor that requires a non-deterministic input value, that value is read from the recorded log.

Asynchronous events are inserted by instructing the CPU to pause the guest at a given instruction count. This is the same count that was stored in the recording log. When the CPU hits that instruction count, the hypervisor is invoked. The hypervisor reads the event information from the log and simulates it for the guest.

#### 3.2.3 Heterogeneous Record and Replay

In a virtualized environment, recording introduces only a low overhead. But during replay, there are no complex analysis tools available. For debugging, it is required to extend the replay mechanism and run further analysis on the program [5,22,23].

To combine the advantages of virtualisation during recording and emulation during replay, a heterogeneous approach can be used. The recording is done in a virtualized environment. The emulator is configured to exactly match that environment. This is not trivial, since the emulator needs to be able to emulate all instructions of the source platform for every possible input parameters exactly, including the flags registers and the unspecified behavior [6]. Current implementations have slight differences between the real hardware and the emulator. This is the case for instructions that are not used by the C compiler or instruction result bits that are usually ignored [13]. So for normal applications, there should be no difference in the execution due to those differences in interpreting the instructions. But a exact replay cannot be guaranteed. It is then loaded with the initial state of the virtual machine. During replay, the events to be emulated are read from the replay log.

In Decoupling dynamic program analysis from execution in virtual environments, a ht erogenous record and replay solution called Aftersight has been implemented and evaluated. The new aspect here is that the replay environment differs from the source environment since replay can be done on an other machine. In the previous virtual machine to virtual machine case, it was sufficient to record the input parameters to external hardware as long as that hardware would behave deterministically. Since the replay is done on a different hardware now, those hardware components may not be available or may not behave exactly as they did on the source system. To solve this problem, the output of the hardware needs to be recorded as well [24].

It has been shown that a correct replay can be achieved for full modern operating systems like windows or Linux. The recording overhead was approximately 10% for a Linux kernel compilation.

*Aftersight* was used to detect bugs in the Linux kernel. One of their achievements was the detection of a uninitialized stack use in the network stack that was present there for several years.

### 3.3 Multicore Record and Replay

The previous projects focused on record an replay on single-core systems. With the arise of systems that contain multiple CPUs, new problems arise. For those systems, the relative order of events that may influence other processors nees to be recorded [12, 17]. The non-deterministic effects of concurrent memory access is the greatest challenge.

#### 3.3.1 Software Memory Tracing

An emulator can run multiple CPUs in parallel by running them in sequence and periodically switching between them. The emulated system has the impression that all CPUs are making constant progress. Since there is no actual parallel execution, memory race conditions cannot happen. The emulator records the times at which it switches processors during recording. During replay, the processor is switched at exactly the same time. This ensures a consistent replay.

The disadvantage of this approach is that it makes no real use of multi-core hardware and adds to the already present slowness of the emulator.

A faster emulation can be achieved by running the emulated CPUs on parallel physical CPUs. [8] The memory model of the emulator needs to allow concurrent access, especially for atomic instructions like the test-and-set instruction. This can be achieved by synchronizing the access of the processors to the memory.

The problem with this is that the synchronization is non deterministic. An example for this is if a guest uses a spin lock, there is no guarantee which emulated

processor will get the lock. To ensure a consistent replay, this information needs to be recorded.

Since the emulator does not know about the semantics of a memory access the target system does, the emulator needs to record the order of every single memory access of the application to replay them in the correct sequence. Creating one log entry for every memory access and synchronizing every single memory access would result in a big log size and in a huge recording time overhead.

During replay, the emulator only needs to ensure the correct ordering of the single memory accesses. Each CPU is paused before the memory access until the time for this particular access is reached. This makes a replay straight forward in this situation.

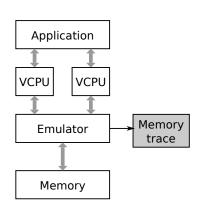

Figure 3.1: The emulator intercepts all memory accesses and traces them.

While this ensures correct recording and replay, it adds a lot of performance overhead to

memory accesses. Since every executed instruction needs to be fetched from memory, this adds a lot of performance overhead. Even when using a readerwriter lock that allows for parallel and low-overhead read locks, there would be a lot of writes to memory cells that would need to be locked. There would also be a global clock that is shared by all processors and that would ensure the correct ordering of memory accesses. All this reduces the scalability of this approach and reduces the performance benefits from using multiple processors.

The disadvantage can be counteracted by grouping multiple memory accesses. Those groups of instructions are called chunks by most implementations [14, 18, 19]. The memory is then not locked for each single memory access but for the chunk as a whole.

A global time frame those chunks are referenced against is introduced [16]. If a processor does a memory access that may cause conflicts with other processors, that access is detected. On each such access, the global time is captured and increased. This denotes the end of a chunk. During replay, the instructions that were part of the chunks are replayed in the same order in which they were encountered during recording.

While this reduces the size of the record, it still introduces a lot of overhead since the emulator needs to check every single memory access for collisions. This check is done in software and adds several CPU instructions per emulated instruction.

#### 3.3.2 Hardware Assisted Memory Tracing

To avoid the significant performance overhead of emulation, the memory tracing mechanisms can be implemented in hardware. The computer hardware is extended by modules that trace the interleaving memory accesses for later replay.

Using this approach, it is not necessary to trace every access to the CPU. CPUs do a sort of memory synchronization on their own using a cache coherence protocol. Hooking into the cache coherence is sufficient to track each CPUs view of the main memory. [11, 18]

Modern processors use a snoop cache coherence policy. The caches snoop on the memory address bus to detect cache conflicts.

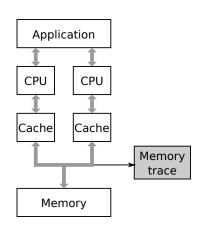

In Architecting a Chunk-based Memory Race Recorder in Modern CMPs [18], hardware modifications that allow the recording of interleaved memory sequences are proposed. For this, the cache coherence protocol is extended. A logger for relevant memory events that synchronize the memory between the CPUs is added, as shown in Figure 3.2.

Events on the cache coherence bus do not contain any timestamp. Since there is no global synchronization on that bus as well, the order in

Figure 3.2: The communication between memory and CPU caches is monitored and the memory access order is recorded.

which the messages are viewed by each processor cannot be determined by simply recording the messages.

To solve this issue, a logical clock is introduced for each processor. It tracks the oder of the individual events. By appending the logical clock to the coherence messages, the processors can record at which time the other processor sent the event and at which time they received it.

The instructions that cause memory accesses are then grouped into chunks between the cache coherence messages. Each instruction in the chunk has the same view of the main memory except for the changes the local processor does. Chunk termination is synchronized using the logical clocks which allows for a replay in the correct order. The changes a processor does to main memory then become visible to other processors after chunk termination, since this is the time the processors first may have synchronized their caches.

In *Rerun* [11], such an approach was implemented. The single chunks are named episodes in Rerun. An episode lasts at most as long as the core does not access any memory that is referenced by the current episodes of other cores. To

detect such conflicts, the the cache coherence bus is monitored. Similar to Intel, the local clock of each processor has been added to the coherence protocol to be able to record the order in which such events happened. This may detect false positives if two bytes on the same cache line are updated, but those false positives do not influence the validity of the result.

If such a reference happens, the core ends it's current episode by writing the current time to the log. During replay, the episodes are replayed sequentially in the same order in which they have ended. This ensures a consistent view of the memory for all processors during replay. There is no ability for a parallel replay in this method since no chunk dependency information is stored.

In *Karma* [1], the concept or Rerun was enhanced by allowing a parallel replay. For this, the predecessors and the successors of each episode need to be recorded. They can be extracted from the cache coherence protocol messages that lead to a episode end.

During relay, this dependency graph is analyzed. Instead of ordering the episodes by a global time frame and running them in sequence, the episodes of each recorded processor are now run on their own processor. Episodes that do not conflict can then be run in parallel. For conflicts, processors need to pause until all episodes that their next episode depends on have ended. For this system, a recording overhead on of 1% for typical applications and 10% for memory conflict intensive benchmarks has been shown. The replay speed cold be increased to be between 19% and 28% slower than the original recording on the same hardware.

Although this approach causes a low overhead during recording, the recording is relatively complex. In *DeLorean* [14], a new coherence protocol that focuses on recording is proposed. Implicit memory transactions are suggested to make the deterministic recording easier. Within each chunks, the instructions are considered to be atomic as seen from other processors. If there is a conflict, chunks may be rolled back and the processor is reset to it's previous view of the memory.

To allow for detecting conflicts and rolling back, changes to the processor hardware and the memory bus are required. Therefore this approach requires specialized hardware.

Some processor instructions, like accesses to machine specific registers, are hard to roll back. To avoid this problem, the current chunk is committed before each of those instructions and a new chunk is started afterwards. This ensures that they do not need to be rolled back.

For a correct replay, the commit order of the chunks needs to be stored. The chunks can then later be replayed in the same order in which they were committed to ensure a correct view of the main memory. During replay, a commit protocol needs to be used as well. In addition to this, *DeLorean* uses two separate logs per processor to store non-deterministic events. One log is used for asynchronous events like interrupt requests. For those events, the system needs to be paused at

#### 3.3. MULTICORE RECORD AND REPLAY

a specific time during replay. The other log is used to store the results of synchronous operations like I/O operations. Those events are triggered by the guest during replay at the exact same state as they were recorded.

The granularity in which memory accesses were logged are cache lines. This makes two memory accesses conflict not only if they affect the same memory cell but also if they are on the same cache line. This greater granularity is required because the chunk coherence protocol only works on cache lines.

#### 3.3.3 Virtualized Memory Tracing

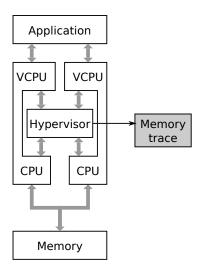

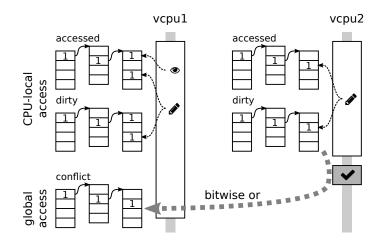

With the emerge of virtualization technologies, an additional layer is added between the hardware and the operating system. It allows to run an unmodified operating system in a virtualized environment. This allows the memory tracing mechanisms to be moved to the hypervisor layer (Figure 3.3). Since the hypervisor is implemented in software, no hardware modifications are neccessary.

In Samsara [19], such a recording system was implemented. It uses a memory chunk protocol that is similar to *DeLorean*. In contrast to *DeLorean*, the recording is able to run on an state of the art system and does not require hardware modifications.

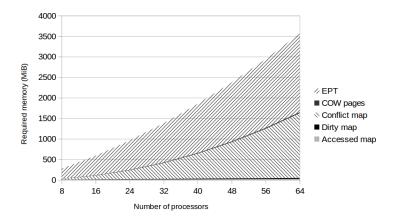

Modern processors with virtualization support use a separate extended page table to map the memory of the guest to the physical memory. Normally, hypervisors use one table per virtual machine for this mapping. *Samsara* instead uses one table for each processor. This allows the tracking of the accessed and dirty bits of each

Figure 3.3: The hypervisor instructs the CPU to provide it with tracing information. It then writes the traces to the log.

individual processor to detect reads and writes to memory pages.

To simulate transactional memory, copy-on-write is used. On each write to memory, that write operation is only performed to a copy of the actual memory page. This page is then written back to main memory during the commit operation. Since the extended page tables are per processor, this allows a different view of the main memory for each processor so that each processor sees it's own writes but not those of other uncommited chunks.

A chunk is ended when the processor switches from guest to hypervisor. Page fault switches are ignored, since they occur frequently due to the copy-on-write required for writing memory. Other switches trigger a commit attempt of the current chunk. If the chunk is committed, the set of accessed pages is determined. It is then compared to the dirty map for the current processor. That map contains a list of pages that were written to by other processors. If there is any intersection because any of the pages the current processor accessed were written to by an other processor, the commit is aborted and the processor is rolled back to the state at which the chunk started. If there is no conflict, the chunk is committed by writing all pages that were modified back to the main memory. Then, the written pages are added to the dirty map of all other processors so that they get a conflict if they attempt to commit a conflicting access.

Samsara puts a lot of effort in optimizing the recording and reducing the recording overhead. This includes an optimized copy-on-write strategy that reuses copies from the previous chunk, double buffering of the conflict page set for reduced locking conflicts and a commit protocol that reduces the time a global lock needs to be held to a minimum. With those optimizations, *Samsara* adds an overhead between 310% and 510% for a four core simulation. Although this is a significant overhead, it is relatively low compared to other software based solutions [17].

During replay, the same mechanism can be used to simulate a transactional memory. To ensure a correct ordering, each chunk may only start if all previous chunks have been committed. For this, the index of the chunk that was committed last before the current chunk needed to be recorded. For page writes, copy-onwrite needs to be used as well. The changes may only be written back to main memory on the current chunk commit. This commit may only happen after all previous commits of the other processores happened to ensure a correct replay order.

While *Samsara* puts a lot of focus on efficient recoding, the replay was not implemented in their prototype and not evaluated in their paper.

### 3.4 Conclusion

Various ways of recording a system and replaying it later have been evaluated in the past. The ability to record a virtual machine using normal consumer grade hardware has only been evaluated lately. While the recording on this platform was evaluated to work, it was not yet evaluated if such a recording can be analyzed using an emulator to get a more detailed view on the recorded program.

For recording, a chunk based recording approach has been shown to have a low overhead in general. In *Samsara*, such an approach was implemented for recording a virtual machine. The ability to replay of such a multi-core recording using an emulator needs yet to shown. This will be the primary goal of this work.

### Chapter 4

# Design

In this work, a record and replay system will be implemented that supports replay in a different execution environment than the recording. The focus of this work is on supporting multiple CPUs that run in parallel in this heterogeneous environment.

### 4.1 Recording

During the recording phase, non-deterministic events are captured for later replay.

#### 4.1.1 Initialisation

When starting a recording session, the recoding infrastructure needs to be set up before executing any guest code. A storage needs to be created and made accessible by the host kernel. This can be done before starting the virtual machine.

The recording state is only bound to the virtual machine. This allows the recording of multiple virtual machines simultaneously. Therefore, the required data structures need to be added initialized for the virtual machine. For each processor, a event log storage that records the processor events needs to be created.

The initial state at which the system starts is usually the system reset state. In this state, the processors are in a predetermined state. This state is set up by the hypervisor and can be set up fully deterministically. Therefore, it is not required to record the initial system state.

The virtual machine is then started. The loading of the BIOS, the boot vector, and other IO events are then recorded so that the system boot can be replayed exactly.

#### 4.1.2 **Processor Events**

During the execution of the virtual machine, the processor may generate events that cannot be emulated during replay. Those events need to be detected and recorded to an event log for later replay.

#### **Synchronous Processor Events**

Many processor instructions are deterministic. This includes memory accesses, disk access and instructions that do register computations. The result of those instructions can be fully emulated if the current state of the CPU, RAM and disk are known. This is why those instructions do not need to be recorded.

The output of the remaining instructions cannot be fully determined by the emulator. This includes reads and writes to IO memory and machine specific registers. Since they are synchronous to the program flow, they will happen at the exact same time during replay. Their input parameters are the same as well, since they depend on the current CPU state which is fully known to the emulator. So only the registers that were changed as a result of the instruction need to be changed. A synchronous processor event containing those results is added to the event log for those instructions.

For verification, it can be useful to record the input parameters and the processor state when running the instruction as well. That way, divergences between the recorded program and the replayed one can be detected early without adding much overhead.

The processor events are then scheduled to be written to the event for synchronous log. There is one log for each virtual processor. This avoids synchronization problems.

#### **Asynchronous Processor Events**

Interrupts are asynchronous events that are passed on to the guest system. Whenever those interrupts are generated, the guest application is paused by the hardware and the hypervisor has to forward the interrupt to the guest. The time at which this interrupt happens is independent from the current processor state. This means that those events won't be happening automatically during replay.

To be able to replay those events, they need to be recorded in a way that allows inserting them at the exact same instruction during replay. To ensure this, the CPU is instructed to count the number of instructions it executes in guest mode. This count is then used to store the time at which an interrupt happened.

In addition to the instruction count, a part of the guest processor state is stored as well. This allows a validation of the replay processor state on interrupts. Due to

#### 4.1. RECORDING

limitations of the hardware, the instruction count may be off by a few cycles. [9] During replay, the processor state can be used to re-align the instruction counts of the replay and the recording.

The event is then scheduled to be written to the asynchronous event log. The event log for asynchronous events is separated from the one for synchronous events. This makes handling the different cases during replay easier.

### 4.1.3 Chunk Based Commit Protocol

On single-core systems where the CPU is the only entity that accesses the main memory, memory accesses are fully deterministic. A multi-core record and replay requires to record the interleaving of the memory accesses. This is done using a commit and rollback procedure that ensures that concurrent memory accesses can be tracked.

#### **Defining a Chunk**

A chunk is defined as a sequence of instructions whose view of the main memory is not influenced by other processors. Form the view of the instructions inside a chunk, they have exclusive access to the memory. From a outside view, all changes a chunk makes to main memory happen atomically.

The memory state at the beginning of a chunk is the memory state the instructions operate on. The instructions can then modify the memory and following instructions in the same chunk see the modifications of the current CPU only. Written memory is not made available to other processors but only stored locally. Those dirty pages are visible globally after a chunk has ended successfully. Such a successful end of a chunk is called commit.

Implementing this in practice introduces difficulties, since there is no hardware mechanism that ensures this atomic protocol. A roll back approach has been chosen to avoid this issue: Each chunk that cannot commit using those invariants is rolled back instead. This may happen on conflicting writes. If two concurrent chunks write to the same memory cell, their real write order is unknown. This is why those chunks need to be rolled back.

For avoiding a full memory snapshot when starting a chunk, the chunk reads are always done on the current main memory. This introduces the problem that the chunk may read a memory area that was altered by an other processor after the chunk started. This violates the assumption that a chunk always has an uninfluenced view of the main memory. For this reason, chunks such accesses are traced and chunks with such accesses are rolled back.

To avoid overhead, a page wise approach is used for tracking memory accesses. This has the additional advantage of being able to track page reads and writes using the accessed bits of the page tables.

#### **Processor Isolation**

Whether a chunk is committed or rolled back is determined at the end of each chunk. Therefore, other processors may not see any effects of the other processors until after they have committed.

To ensure this, all changes the to the main memory during a chunk is not written directly to memory but to a temporary memory area. To implement this efficiently, copy-on-write is used.

All processors share a common memory that represents all guest memory contents that have been committed. Each processor has it's own page table that maps in all this guest memory as read only. As soon as the guest writes to a memory page, that memory page is duplicated for the guest and the writes are written to the duplicate. The guest then does further reads and writes to that local page. That way, changes to memory contents are not visible to other processors.

Handling machine specific registers and accesses to IO memory cannot be delayed using this mechanism. The processor requires the hardware to do those accesses immediately. To make this direct hardware interaction possible, it needs to be done in a state in which a rollback may not happen. For this, the current chunk is committed before such an access is done. The access is then executed and the next chunk starts with the result of the access. That way, the access only needs to be done once on the hardware. If the next chunk is rolled back later, the results of the access can be re-used. For this, it is stored in the processor local data structure that restores the processor state on rollbacks.

#### **Tracking Chunk Memory Accesses**

In order to determine whether a chunk can be committed, the pages that were accessed in the chunk need to be tracked.

This is done by using the accessed flag of the extended page table. This flag is set by the processor MMU on each EPT lookup at the corresponding page table entry and all parent entries.

At the beginning of each chunk, the flag is reset. That way, the flag was set by the hardware at exactly the memory pages that were accessed during the chunk once the chunk has ended.

The the flags are read at the end of each chunk. For this, the EPT is walked hierarchically. Since the accessed flags are set on all page table levels, a full scan of all page tables is not required. The scan can be done efficiently in linear time relative to the number of accessed pages.

#### 4.1. RECORDING

For memory writes, copy-on-write needs to be used. This requires all pages to be set to read only. That way, the hypervisor is trapped on the first write access to each page. The hypervisor then copies that page to a new memory page and alters the EPT entry to point to the new page. It sets the accessed flag and sets a flag in the dirty page set to indicate that this page was written to in the current chunk.

For storing the set of accessed and dirty pages, a data structure that holds a set of pages and allows for a fast iteration of the page numbers and a fast check if it contains a single page number needs to be used. *Samsara* uses a bitmap in combination with a linked list. Both data structures always contain the same information. This redundancy allows the fast lookup times of a bitmap to be combined with the linear walk time of a linked list.

The disadvantage of this approach is that a bitmap takes as much space as the highest possible virtual address is. For virtual machines with a contiguous memory, this is not a big problem since the maps are still comparably small. But as the virtual memory gets bigger, the size of the bit maps increases. Modern systems may not even require a contiguous virtual memory. On those systems, a memory bitmap mapping the full 48 bit address space that a modern Intel EPT could address requires  $2^{48}$  bits (35 terrabytes) of memory.

To reduce this amount, that information can directly be stored in the page tables. One of the reserved bits of the EPT can be used for this. The dirty flags is set in the EPT of the current processor when a copy-on-write operation occurs. The insert operation for this is no performance overhead, since the EPT entry needs to be written to to update the page address any way.

An efficient walk of the dirty pages is only possible if all parent pages have the dirty bit set correctly. The dirty bit cannot be set on the first page table walk that determines the page address on a page fault, since it is unknown then if the page should be copied. Therefore, the dirty bit is only set in the last level of the page tables. For each page that was marked as dirty, the accessed flag is set as well. Since the accessed flag is set in the complete page table hirarchy, the accessed pages can be iterated efficiently. During the commit phase, such a walk of the accessed pages is required. During that walk, the dirty pages can be tracked as well with low overhead.

#### **Detecting Chunk Conflicts**

At the end of each chunk, a decision needs to be made on whether to commit the chunk or to roll it back. For this, a conflict page set is used for each processor that tracks the pages on which it might conflict with other processors.

For this, the commit conflict page sets are first locked globally. This ensures that no other processors influence the computation. It also ensures that no other commits happen while the current chunk is committed.

Then, the read and write actions of the chunk are compared to other chunks that were active while it was running. The chunk needs to be rolled back if any chunk it has accessed was written to by an other processor during time the chunk was active.

For this, each processor has a processor local map of pages that were modified by other processors during the chunk. Other processors did modify this map when they did commits, so this information does not need to be derived.

The processor then computes a list of pages it has accessed. It is then tested if that list intersects with the conflict page set. If they do intersect, a conflict happened and the chunk needs to be rolled back.

#### **Chunk Commits**

After determining that a chunk needs to be committed, the data required to replay it is written to the replay log and it's memory modifications are made available to other processors.

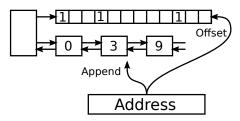

First, the commit index is determined. For this, a global counter is used that is incremented atomically. This commit index is used for the chunk end event so that the chunks can be ordered correctly during replay.

Then, the list of the copy-on-write pages of the current chunk is determined. Those pages can be found by either walking the extended page table or by tracking them in a separate copy-on-write list. Those pages are written back. For each of thoise pages, the corresponding page is added to the conflict page set of all other processors.

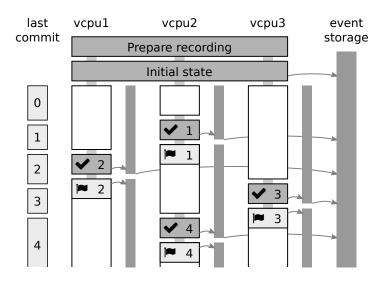

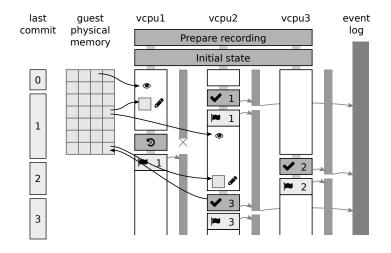

During the chunk, all events were written to the temporary event log. On a commit, this temporary event log is written to the persistent event log. In addition to the processor events, a chunk start and a chunk end event is added. Those events are added to the asynchronous log, since they have not been triggered by the program flow. In Figure 4.1, this mechanism and the temporary event logs are visualized.

The chunk start event contains the index of the last commit that happened before the chunk was started. Since a chunk's view of the main memory is determined by the time it started, this information is required during later replay to determine the time at which the chunk may start running. Due to the delayed addition of the events to permanent storage, the current commit counter can be added to the start of the chunk as well. That way, the replay system can determine the commit time at which a chunk ends easily. This makes ordering the chunks for later replay on single-core processors easier.

At the end of the chunk, a chunk end event is added. It contains the commit index of the chunk.

It would also be possible to store the list of accessed and written pages of

Figure 4.1: The execution of the guest CPUs is periodically paused. The chunk is then committed by storing it's events to the event log. The chunk end event contains an index that indicates the order in which the commits happend.

the current chunk. This might allow for further performance optimizations during replay. Since replay performance is not the focus and a fast recording with low memory overhead is desired, this is not done. A correct replay is possible without this information.

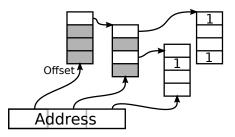

#### **Chunk Rollbacks**

If a conflict was detected during the commit phase of a chunk, the commit is aborted. The chunk is rolled back and the processor state is restored so as if no instructions were executed since the last chunk.

All changes made to the memory are discarded by removing the copy-on-write pages and restoring them with the current memory contents of those pages.

The processor state is then restored to the state that was stored at the chunk start. This state includes the registers of the processor with the instruction pointer. That way, the program resumes it's execution at the point where the previous chunk ended.

There might have been interrupts on the current processor for the chunk that is to be rolled back. Since the chunk is rolled back, the guest needs to see a state in which those interrupts have not been handled. For this to happen, the interrupt flags are set again. This causes the processor to execute the interrupt handler for

Figure 4.2: On memory writes, a local copy of the memory page is created. That copy is committed at the end of each chunk. If it was accessed by other processors in between, the chunk is rolled back and the changes are discaded. Chunk starts and commits are stored to the event log.

the flag with the highest priority as soon as the processor starts executing the next chunk. From a guest perspective, this causes the impression that the processor was only paused by the hypervisor and the interrupt occurred while the processor was paused. The guest will then execute the interrupt handler as if that interrupt handler was never executed.

#### **Forced Commits**

Commits are normally done on a regular basis every several milliseconds. This ensures that changes a chunk made become visible to other processors after a few milliseconds. For this, a timer is used that traps the vCPU into the hypervisor after a given time. The current chunk is then committed.

But there are situations that require an instant commit of the current chunk. One such situation is the interaction with hardware. When the guest system accesses hardware, the hardware is not accessed directly. Instead, the hypervisor is trapped to emulate the hardware access. The hypervisor normally forwards those calls to the real hardware. This may be a network device or a hard drive. For most devices, this forwarding means that the hardware state changes in a way that cannot easily be undone.

State from one processors should only be visible to other processors after a chunk commit. Since the hardware device is shared between processors, it would

#### 4.1. RECORDING

also mean that the commit protocol would need to be extended to hardware registers. The hardware would need to have the ability to be visible to other processors in an older state and conflicts on the hardware would need to be detected.

When rolling back such hardware operations, all state needs to be restored. This includes communication with external devices. For the network interface, packages could be delayed. But other interfaces like the serial port might not be able to delay the messages if the timing is critical or if the processor awaits a direct response.

Therefore, the commit and roll back protocol cannot be extended to generic hardware devices. To avoid this issue, whenever the hypervisor traps for an IO operation, a commit is forced. The processor then either commits or rolls back the current chunk. If the chunk was rolled back, the processor is restored to the old state and the IO operation request is ignored by the hypervirsor. The processor resumes the virtual machine execution at an earlier point. The guest chan then attempt the IO operation again in hope that no conflict occurs.

If the commit was successful, the IO operation is performed. The hypervisor then sets the guest registers to to correspond with the new hardware state and loads the return value from the hardware into the desired register. After that, the snapshot for later roll back is done. This ensures that a roll back always rolls back to directly after the IO operation. The IO operation itself is not rolled back.

Since the guest was not resumed, no memory accesses may have been done in the time between the commit and the rollback checkpoint. That way, this short time does not need to be protected by the memory commit protocol.

#### 4.1.4 Direct Memory Access

When other hardware has direct access to the main memory, the same problems as with multiple processors arise. Therefore, that hardware needs to participate in the commit protocol as well.

This may even happen in systems with only one CPU that support direct memory access (DMA). DMA allows the hardware to directly access the main memory. In virtualized environments, the guest operating system has no direct control over the DMA controller. Instead, all accesses are trapped by the hypervisor. It then checks the access permissions and forwards the request to the controller. That controller can then both read from and write to main memory.

The memory that is written by the DMA controller on a write operation can be seen as deterministic as long as the state of the source hardware is known or recorded. But while the read operation is in progress, the destination memory area is written to by the DMA controller at an unknown time. Therefore all read of the running CPU to the affected memory area can be considered non-deterministic. For operations where the DMA controller reads from memory, a similar problem may arise. While the DMA controller reads the memory, the processor may modify that memory area. Therefore the values read by the controller are nondeterministic.

Guest applications normally require a deterministic behavior of the DMA controller. This is why they do not access the memory that was passed on to the DMA controller while a DMA operation is still in progress. But this behavior cannot be relied on to ensure a deterministic replay. It can be enforced by the hypervisor by locking the affected pages for read/write access while the DMA operation is in progress. That way, the guest application will need to be halted if it attempts to access one of those pages.

An alternative is to buffer the DMA controller memory by using copy-on-write while the controller reads from memory. For DMA writes, the data is written to background pages and the pages are then made visible to the guest by re-mapping them. This has the advantage of making the DMA operations atomic and allowing a simpler replay implementation at the cost of reducing the DMA performance and increasing memory requirements while recording.

#### 4.1.5 Checkpointing

An alternative to starting the recording at the system start is to allow for it to be started at a user defined time. This has the advantage that the log size is smaller.

To create a checkpoint and start a recording session from there, the virtual machine needs to be paused. A memory snapshot needs to be taken. A hypervisor supports two modes to create a snapshot. In the stop-and-copy mode, the virtual machine is paused, the snapshot is written to disk and the machine is then resumed. In the copy-on-write mode, the virtual machine is only paused a short time to save the processor state. The memory is then to set read only and uses copy-on-write if the virtual machine attempts to write to a memory page. That way, the virtual machine can continue to run while the snapshot is written to disk. Once the snapshot is completely written, copy-on-write can be disabled again. Since copy-on-write is used during the chunks, a stop-and-copy checkpoint can to be done to not interfere with that protocol.

A copy-on-write snapshot is not possible the way copy-on-write snapshots are usually implemented. Current implementations assume that there is only one EPT per virtual machine. If a page write occurs during the snapshot, that EPT can be changed to point to a new page location and preserve the original page contents. This approach does not scale well since there is now one EPT per virtual processor. To avoid this issue, the write back on chunk commits can be intercepted. Before a page is written back, it is first checked if it needs to be preserved for an ongoing checkpoint write. If it needs to be preserved, the original page content is copied

#### 4.2. REPLAY

to a different memory location before the new page content is written. The copied page is then used for the snapshot.

After taking the snapshot, the system initializes the additional data structures for recording. The extended page table is set up for the copy-on-write mechanism. Then, all processors add the initial event to their recording log. That event contains information about the initial processor state. This may include additional information about the current CPU features to match this processor automatically in later replay.

When allowing to start the recording while a virtual machine is running, it may be desired to stop the recording after some time. To stop recording, all processors need to be paused so that none of them writes to memory any more. The hypervisor then does a final commit or roll back operation for each processor. Since the processors are paused, all processors have the same view of the main memory after this is done. The hypervisor then closes the event log and removes all event hooks. The EPT is restored to remove the copy-on-write flags.

After all processors are done with this, the virtual machine can be resumed. The processors then continue to run the virtual machine in the normal, nonrecording execution mode from the point where the recording ended. A recording can be started again at any time. This makes the recording system flexible.

## 4.2 Replay

The replay is done in an emulator that is able to exactly emulate the source system. The emulator is started at the same state the recorded system was when recording started. It then replays the exact instruction flow of that system. To replay nondeterministic instructions and the correct order of memory accesses, the emulator uses the recorded event log.

#### 4.2.1 Initial state

The initial state of the replay needs to be exactly the same as the initial state of the source system.

If the recording was started with the virtual machine construction, the emulator needs to create the exact same system state. It needs to make the same number of CPUs available. Each CPU needs to have the correct virtual CPU ID set and the CPU features need to be matched to those of the source system.

The memory state is set to the initial, reset memory state.

No further setup is required since the non-deterministic actions that may occur during the system boot are all handled by the recording mechanism. This also includes the start of the non-primary processors that is triggered by the guest operating system in the early boot process.

#### 4.2.2 Chunk Ordering

During recording, the vCPUs were running in parallel. If memory race conditions between the processors occurred during recording, the order in which the memory was accessed was recorded by recording the order in which the processors committed their memory. When replaying, the memory accesses need to be replayed with an order that ensures that the result of the memory accesses is the same.

For correctness, an exact ordering of all memory accesses is not required. It is only required that all memory accesses to a fixed memory address happen in the exact same order as they happened during recording.

During recording, the commit protocol ensured that no two threads accessed the same memory at the same time except for reading. Moreover, it is even guaranteed that if a processor writes to a memory page, no other processor writes to or reads from that page during the chunk. If this would have happened, one of the two processors would have been rolled back.

This means that during replay, it needs to be ensured that all chunks that write to a fixed memory address x are replayed in the correct order. If two there are two chunks  $c_{1,2}$  accessing the memory page of x and  $c_1$  was committed before  $c_2$ started, the writes of  $c_1$  need to be replayed before the replay of  $c_2$  can be started.

Since there can only be one active chunk writing to that page, this ordering is ensured if a chunk only starts to be emulated after all chunks that were executed prior to it during recording have finished.

An emulator can emulate parallel processors by running them in sequence and switching between them. This ensures that there are no direct race conditions between the processors.

For such a single-core replay, those constraints can be met if all chunks are executed in the order in which they committed. If the commit order was stored along with the chunk start event during recording, the processors are always yielded whenever a chunk ends. The event logs of all processors then contain chunk start events at their head. Since those chunk start events contain the commit index, one of them needs to contain the next commit index. The corresponding processor is then scheduled for execution.

That way, the replay can be done without any need for further, complex conflict logic.

# 4.3 Conclusion

A multi-core virtual machine can be recorded using the virtualization hardware extensions. During the recording, a transactional memory is simulated by splitting the program execution in chunks of instructions. The changes each chunk does to the main memory are then committed atomically. Conflicts are detected and rollback mechanism is used in this case to drop the conflicting chunk.

This recording can then be replayed in an emulator down to the exact instruction level. The emulator needs to be able to exactly emulate the behavior of the source system. For the multi-core support, only minor additions to a single-core emulator are required. The chunks of the individual processors can then be scheduled in their commit order on that single-core emulator.

# Chapter 5

# Implementation