# Prototypical Design and Implementation of L4-SMP Microkernel Mechanisms

Marcus Völp

Supervisor: Prof. Dr. Jochen Liedtke

Universität Karlsruhe

# 1 Einleitung

Speichergekoppelte Multiprozessorrechner finden ihren Einsatz als mittelgroße Serverrechner und Hochleistungs- Arbeitsplatzrechner. Symmetrische MultiProzessor (SMP) Systeme bilden aus der Sicht eines Programmierers die einfachste Architektur eines speichergekoppelten Multiprocessorrechners. Die einzelnen Prozessoren eines SMPs sind über den Speicherbus (oder eine Kreuzschiene) mit einem gemeinsam nutzbaren Hauptspeicher verbunden. Dies erleichtert die Entwicklung von Anwendungen und Betriebssystemen verglichen mit NUMA Architekturen oder nachrichtengekoppelten Multiprozessoren.

Gleichwohl ist die Entwicklung eines SMP-Betriebssystems, selbst für eine so einfache Architektur wie den SMP noch eine große Herausforderung. Der zusätzliche Grad an Parallelität wirft dabei Probleme auf, die mit konventionellen Lösungen nicht mehr zu lösen sind, da das Aus- / Anschalten von Unterbrechungen (interrupts) nur prozessorlokal wirksam ist.

Der L4 Mikro-kern ist einer der schnellsten derzeit verfügbaren. Er steht auf folgenden Einprozessorrechnern: MIPS, Intel x86, Alpha und Arm zur Verfügung. Verschiedene Partnerprojekte implementieren Anwendungen, Betriebssystemkomponenten bzw. eigenständige Betriebssysteme auf L4-Basis wie zum Beispiel:

- L<sup>4</sup>Linux<sup>1</sup> ist ein Linux Betriebssystem, welches als Applikation im Nutzermodus auf dem L4-Mikrokern abläuft.

- 2. DROPS <sup>1</sup> ist eine Echtzeiterweiterung zu L<sup>4</sup>Linux, welche den gemeinsamen Betrieb von gewöhnlichen, wie auch speziellen Applikationen, die Rechenzeitzusicherungen benötigen, ermöglicht. Für erstere wird L<sup>4</sup>Linux, als Betriebssystemserver verwendet. Letztere können auf spezialisierte Server zurückgreifen.

- 3. Saw Mill Linux <sup>2</sup> ist ein Multiserver Linux Betriebssystem. Bestimmte Betriebssystemdienste sind dabei als einzelne, eigenständige Server realisiert, die nach Bedarf zusammengefügt bzw. ausgetauscht werden können. Diese erhöhte Flexibilität kann u.a. dazu verwendet werden, auf besondere Situationen zu reagieren. So kann das Betriebssystem etwa auf den Verlust der Netzspannung, z.B: falls der Laptop vom Strom genommen wird, reagieren und von hoch performanten auf stromsparende Server wechseln.

- 4. *Mungi* <sup>3</sup> ist ein Einadressraum Betriebssystem. Alle Programme teilen sich dabei einen einzigen grossen Address-

raum. Dies hat zur Folge, da/3 Verweise auf Speicherbereiche globale Gültigkeit haben.

Diese Studienarbeit untersucht, welche Auswirkungen ein symmetrischer Multiprozessor auf das Design und die Implementierung eines L4 SMP Mikrokerns hat. Insbesondere wird der Einfluss des SMP auf die grundlegenden Abstraktionen des L4 Mikrokerns untersucht: Threads, Addressräume und Interprozess Kommunikation (IPC).

# 1 Introduction

In the past years, shared memory multiprocessors became widely used as midrange servers and even as high end workstations. Symmetric Multi Processors (SMPs) form the simplest architecture of shared memory computers from the programmers point of view. Several equally functioning processors are connected through the memory bus (or a crossbar) with memory modules. Accesses to those modules occurs in a unique manner for all processors. This makes the development of applications and operating systems much easier than in Non Uniform Memory Architecture (NUMA) processing or message coupled multiprocessors.

Never the less, the explicit parallelism of the applications and operating system servers, makes the multiplexing of the CPUs much more difficult because, first the number of CPUs are increased and second the invariant that when disabling the interrupts no other program beside the one disabling the interrupt will interfere is no longer true.

This problem leads to the challenge of how to design and implement efficient Operating Systems for SMPs in particular and Multiprocessors in general. However this thesis will deal with SMPs only.

The L4  $\mu$ -kernel has proven to be one of the fastest microkernels for several uniprocessor systems like MIPS, Intel x86, Alpha and Arm. Several partner projects are building applications and OS components or even whole operating systems on top of L4:

- L<sup>4</sup>Linux<sup>1</sup> is a user level implementation of the Linux operating system which runs as a normal application in user mode.

- 2. DROPS <sup>1</sup> is a realtime extension to L<sup>4</sup>Linuxthat allows to run a mixture of normal Applications and specialized ones, requiring certain guarantees of computation times to do their work, on the same CPU. The first kind of applications use L<sup>4</sup>Linux as the operating system server. The last kind can rely on specialized servers.

- 3. Saw Mill Linux <sup>2</sup> is a decomposed multi-server Linux operating system. Certain operating system services are implemented as several independent servers that can be composed and exchanged on demand. The increased flexibility of such a system can i.e. be used to adapt the system to special situations dynamically. When i.e. the Laptop is unplugged, the

<sup>&</sup>lt;sup>1</sup>TU Dresden:

http://os.inf.tu-dresden.de

<sup>&</sup>lt;sup>2</sup>IBM Watson, Universität Karlsruhe, TU Dresden:

http://www.reseach.ibm.com/sawmill

<sup>&</sup>lt;sup>3</sup>University of New South Wales:

http://www.cse.unsw.edu.au/ disy/Mungi

high performant servers can be swapped out and exchanged by special power saving ones.

4. *Mungi*<sup>3</sup> is a single address space operating system. All applications share a single huge address space which has the immediate consequence, that pointers holding an address are valid through the entire lifetime of the system.

Both, the increasing relevance of multiprocessors and the applicability of the microkernel approach motivates for a L4-SMP  $\mu$ -kernel. This thesis will describe the prototypical design and implementation of L4 SMP mechanisms. In particular it will try to answer the question which extensions have to be introduced to the basic uniprocessor concepts: threads, address spaces and inter process communication.

The following two sections give a brief introduction to the L4 uniprocessor  $\mu$ -kernel and to such parts of the Intel Pentium hardware that are relevant for SMP  $\mu$ -kernel design and implementation. Those two sections are included in the paper to give a brief introduction to the environment, the remaining part of this thesis is based on. Readers that are familiar with the Pentium hardware and the L4  $\mu$ -kernel should skip these sections and continue in section 4.

# 2 The L4 uniprocessor $\mu$ -kernel

Monolithic kernels suffer from their inherent complexity and inflexibility. Changing the behavior of a single component, like the paging policy for example, requires at least recompiling the entire system. Faults and errors in the new component might propagate to other components and thus may effect the whole system. Ensuring fault tolerance of the system, has to take into consideration the entire operating system and not only the changed parts. Even parts of the system that are not depending on the changed components might suffer. Frequent errors in the new component (like an uninitialized pointer) may result in a system crash.

Multiserver operating systems help to tackle this problem. Each component of the system is implemented as a server, running in user level like any application does. Almost every modern processor implements at least two modes: supervised and user level.

- User mode: Applications run in user level. They are protected from being modified by other applications and from modifying other ones. Only a subset of the instructions of the processor is available in user mode. None of these operations can be used to harm or to compromise other applications or to monopolize the operating system as a whole. I.e. disabling the interrupts (with cli) cannot be allowed to be used in user level, because if this instruction is used by an application, the timer interrupt is disabled as well and the operating system may not get control of the processor in time.

- Supervisor mode: Code running in supervisor (or kernel)

mode has full control of the entire system. It can use all processor instructions, even those that might compromise the system (when not handled with care like if the system runs in an

endless loop while interrupts are disabled with cli). In supervisor mode, the kernel code can switch between different

applications.

When an application generates an exception, i.e. dividing by zero, the processor switches from user to supervisor mode, invoking a kernel method to handle this error. The handler eventually aborts the application, whilst the remaining applications in the system stay alive. However, if the same exception would occur while running kernel code, the system will crash.

On an Intel Pentium exceptions in supervisor mode will invoke a handler method as well, but if the error cannot be repaired (i.e. a division by zero), the system will crash due to an abort of the kernel.

Figure 1: Monolithic Kernel vs. Microkernel

While monolithic operating systems run all their components in supervisor mode, multiserver OS components are executed in user mode. Just opposite to a monolithic kernel design we can place each component in a separated and protected address space <sup>4</sup>. Errors in one of the server components might crash this particular server but none of the others. Thus the rest of the system will survive. In particular a corrected version of the formerly crashed component can be installed on the fly and tested for correctness. Altogether, we have an environment, where we can test the components incrementally, making the system more robust.

The mechanism to exchange servers on the fly increases the flexibility of the system. Special servers can be loaded to adapt to new situations, like the power example described in the SawMill part of the introductory section 1, more than one server per OS function can coexist in the system at the same time, allowing the system to adapt to the requirements of specific types of application. The same system can be used to support a large database and a personal digital assistant PDA. In the first case high performing, large servers are combined, while in the second case lightweight, power and resource saving servers might be the better choice.

However two problems still remain: First, as described above, only a subset of the processor instructions are available in user mode and second, some part of the operating system has to remain in supervisor mode to multiplex the processor among the user level system servers and applications. Furthermore it has to handle exceptions and interrupts. This is exactly what a  $\mu$ -kernel does.

The first  $\mu$ -kernel approaches were constructed by extracting as much of the operating system's functionality out of the kernel and put this functionality into as many separate user level servers. The remaining part of the kernel should be as general and flexible as possible to allow a large variety of OS services to coexist. The separated components of the OS were protected against each other, in the same way as applications are isolated on top of a monolithic kernel. Provided the  $\mu$ -kernel is correct. Faulty servers may crash but they can no longer affect other correct ones.

However, the first generation  $\mu$ -kernels like Mach failed! The large communication overhead between the extracted components that was introduced by the  $\mu$ -kernel mechanisms like IPC, made its use for a multiserver OS unaffordable.

<sup>&</sup>lt;sup>4</sup>However, we can place more than one component into one address space if needed due to performance reasons.

Learning that lesson, the development of a second generation of  $\mu$ -kernels had begun. While the first generation tried to extract several parts out of an existing monolithic kernel, L4 was designed from the scratch. The goal was to find a minimal but high performing set of mechanisms, implemented in the  $\mu$ -kernel, with which any reasonable policy can be build on top. L4 implements only three basic abstractions to achieve this goal: Threads, Address Spaces and Inter-Process Communication (IPC). Threads and address spaces are used to multiplex the CPU and memory. Inter-Process Communication (IPC) is used to overcome these protection borders introduced by address spaces in a save manner. In the following subsections these three fundamental mechanisms and their usage for the uniprocessor L4  $\mu$ -kernel are described.

#### 2.1 Threads

In L4, threads are small entities of code that can be executed concurrently. In contrast to the event model, threads are created and live until they are explicitly deleted. Synchronization between different threads has to be done explicitly through IPC for example. The opposing model, the event model can be shortly described as follows. On an event, a thread is created, computes and dies when it has finished its work. In between or when dying the thread might trigger further events that leads to the construction of further event handling threads. Multiple of those events can coexist in the system and are handled in parallel. In the event model, the threads do not explicitly communicate with each other, they use the events instead to trigger the service needed. Instead of synchronizing with other threads implicitly, in the event model, those events implicitly synchronize concurrent activities. I.e. in a matrix multiplication, multiple events are triggered by the compute thread to activate the working threads. When finished computing its part of the multiplication, the working thread generates an "I am finished" event and the compute thread collects all this events and if all working threads finished, it can combine the results to the global result of the matrix multiplication. So what was achieved in this example is a barrier synchronization through events. In opposite to a thread model, the worker threads are created on the first and die on the second event. However, since the threads in the event model does not store state information at the time they die on an event, the state has to be included into those events. While in the thread model it makes a difference whether an IPC (i.e. a call to a server to trigger some action) is send in the if or in the else path of a client's code (i.e. if (condition) IPC: add (a, b) else IPC: subtract (a, b)). In the event model, dependent on the condition, one of two different events, representing the condition has to be triggered (i.e. condition true request add, condition false request sub events).

Because of this, L4 uses the thread model instead of the event model

The information needed to manage and control a thread is stored in its Thread Control Block TCB. In the TCB, the current state of a thread is stored, i.e. if it is ready to run, waiting for another thread or currently communicating to another thread through IPC. Within a thread switch, the general purpose registers, the stack and instruction pointer are stored into the TCB of the current thread and reloaded from the TCB of the thread to run next.

#### 2.1.1 Scheduling

To be flexible, L4 does not implement certain high level scheduling policies, but keeps this to the responsibility of a user level scheduling server. However due to performance reasons, fine grain scheduling is done by the kernel. The user level scheduling server can parametrise this fine grain scheduler for each thread under its control through the system call thread\_schedule. Those control

parameters for the  $\mu$ -kernel's dispatcher (fine grain scheduler) are located in the TCB as well.

A thread can voluntarily release the CPU by calling thread\_switch. This call can be parameterized to switch to a specific thread or to let the dispatcher decide for the next thread to run.

In this case the dispatcher will chose the ready thread with the highest priority in the system. The priority of a thread is one of those above described control parameters that is stored in its TCB.

In addition, each thread has a period of time, the timeslice, that limits the time, the thread is allowed to run on the CPU. When the timeslice expires, the dispatcher is invoked and will chose the next ready thread of that priority in a round robin manner. So to sum up, ready threads with the same priority share the CPU in rates specified by their timeslices as long as no higher priority thread gets ready.

#### 2.1.2 Thread Creation

Lthread\_ex\_regs is used to modify a thread's instruction pointer, stack pointer and pager (see below). Threads are created by setting the instruction pointer to a valid value (Note, address spaces are only the first 3GB of the available hardware space. So above 3GB a user level instruction pointer is invalid because this area is reserved for the kernel). Lthread\_ex\_regs works only for threads, sharing the same address space. So the first thread has to be created in different way. This is done when the address space is created. In the next  $\mu$ -kernel version, threads will be created through the explicit operation thread\_control.

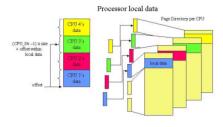

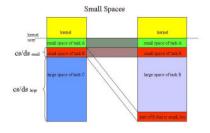

# 2.2 Address Spaces

"What is an address space? To answer this question we take a whole portion of nothing and call it an address space. In addition we let threads operate in it and if they touch somewhere in that nothing, it is up to the operating system to back the touched location with a page of physical memory."

When in the Intel Pentium processor the protected mode and paging is enabled, the memory management change from direct handling of physical memory to virtual memory. The physical memory is split up into equally sized portions called frames. Each frame is 4KB large and aligned, i.e. starts with an address that is a multiple of 4KB.

The addressable area (4GB for a 32 bit address bus) is split up in 4KB regions as well. Those regions are called pages. We now introduce another level of memory: Virtual memory that is the addressable area, so consists of pages. Note the size of the pages are processor dependent, the Intel Pentium offers two different sizes for example: 4 KB and 4 MB, but for simplicity reasons, address spaces and mapping is explained for 4 KB pages only.

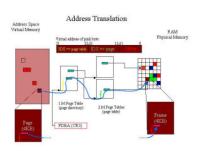

The page tables are used to store a map containing all information needed to translate an access to a virtual page, i.e a virtual address to a physical frame that backs that location. Accesses to a virtual page are automatically translated by the Memory Management Unit (MMU) into accesses to a physical frame by parsing the page tables. The Intel Pentium hardware for example has two level page table scheme. The virtual address (sometimes called linear address) is divided into three parts: an offset (the lower most 12 bits), and two indices (10 bits each) to address the first and second level page table entries. Starting from the Page Directory Base Address register (PDBA), that contains the offset of the first level page table, called page directory, the upper 10 bits of the address are used to find the page directory entry. This entry points to the starting address of the second level page table (simply called page table). The mid 10 bits of the virtual address index a page table entry that points to a 4 KB page frame. The lower most 12 bits of the page table entry are used to decode several page attributes i.e. if the page is read only, or if the frame is present at all.

Note, not all pages have to be backed by a frame (entry is not present). Neither has to exist a translation to all the physical frames. Each page may map to (i.e. be backed by) either zero or exactly one frame. In the first case, we say the page is not present and if accessed, the hardware will raise a pagefault. Multiple pages may point to the same frame but one page may point to no more than one frame.

With this, the entire address range of the processor can be used, though not all addresses need to be backed by a frame at the same time. In addition each thread or group of threads may have its own virtual memory, called address space. When switching to a thread that does not share this address space, the page tables are exchanged and with this a new mapping of pages to frames is established.

In the paragraph above, mapping is used in its mathematical context. The term mapping was used to describe pairs: page to frame. Now we will use the term mapping for an operation on pages. We will see, that there is not much difference. Above, the term described a relation between virtual to physical addresses, i.e. pages to frames. Now we use the term for describing a relation between two pages, i.e. between two virtual addresses and construct an initial mapping concerning the physical addresses.

Figure 2: Virtual to physical address translation

L4 reaps benefit of the virtual memory concept to construct its address spaces. In a monolithic system it is up to the operating system to ensure, that the mappings of two address spaces do not overlap involuntarily. When each address translates its pages to a disjunct set of frames, there is no way for the first to corrupt the data in the pages of the second address space.

In L4, the construction of address spaces is up to user level paging servers, threads that run itself in an address space. Assume by magic, these address spaces get some data, i.e. a mapping (mapping in the formerly described sense) of some pages, backed by frames, was established. Address spaces can now be constructed by sharing pages. The threads that share the pages with the new address space are called this address space's pagers. Those pagers can only share pages owned by themselfs, i.e. only those backed by a frame can be shared. This operation is called mapping. It is performed by the  $\mu$ -kernel on behalf of the pager. When a page is mapped to an address space, the  $\mu$ -kernel parses the page tables, like the MMU does, to find the frame of the page to be mapped and creates a corresponding translation in the target's address space's page tables to exactly that frame. As a result, the page is now visible in both address spaces. To avoid magic in the  $\mu$ -kernel (because this is really hard to im-

plement), we construct an initial address space called sigma 0 and establishes a mapping to all available frames (i.e. to those not used by the  $\mu$ -kernel itself) by hand.

From this point on mapping works from address space to address space and operates on pages, i.e. virtual addresses. For the user level pager, frames are no longer visible.

To sum up, address spaces cover the entire address range of the processor, the entire virtual memory. However not all virtual memory locations (pages) may be covered by physical memory (frames). They exist per thread or per set of threads and multiple address spaces may coexist in the system. Two address spaces, with non overlapping mappings, that is taken an arbitrary page from one and another from the second address space, these pages will not be backed by the same frame. In that case a protection border is established, because threads in the first cannot corrupt the second address space's memory.

#### 2.2.1 Mapping and Granting

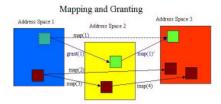

Figure 3: Mapping and granting pages

In L4 based systems, address spaces are constructed hierarchically by mapping (i.e. sharing) or granting (i.e. donating) pages from one address space to another. The entire hierarchy with sigma 0 as the root pager, is built up by mapping or granting pages from address space to address space, so from virtual to virtual address. Despite those operations, map and grant and an additional operation to undo a mapping: unmap, the construction of this hierarchy is done by user level threads. Mapping works such, that a thread in one address space, the mapper, invokes the  $\mu$ -kernel to map pages, that are in its address space to the destination's thread, the mappee's address space. To make this operation secure, both partners, the mapper and the mappee have to agree on the mapping, which makes this a synchronous operation. In addition, the mapper specifies the page that will be mapped and the mappee has to specify the destination where to map to. This has to be done to avoid interferences, i.e. a mapper maps a page to a location where it may harm the execution of threads of the mappee's address space, like when mapping a data page to a code page. Because of the similarity of the control requirements, mapping and granting are implemented as special message types of IPC (see below).

# 2.2.2 Unmapping and Pagefaults

By accepting a mapping, the mappee automatically agrees, that the mapper can revoke this mapping any time. A mapping can be revoked or weakened with the system call fpage\_unmap. Weakening a mapping means that the page is not removed, but that the access rights are changed to read only. Other architectures allow independent access rights for reading, writing and executing, so weakening in those architectures would allow write only, execute only, read execute, write execute and so on access right combinations

In contrast to mapping or granting, unmapping has to be asynchronous. This means that the unmap operation will be performed immediately and will not wait for the mappee's agreement. This is necessary to avoid that the client (the mappee) postpones the unmapping request for pages formerly mapped by the server (the mapper) because of a denial of service attack by the client or simply by not listening to unmap requests. The asynchronous unmapping is for example being used by pagers implementing swapping. Before the memory pages are swapped out to disk the pages are unmapped, so that the clients of that pager can no longer use the page.

With these three operations: mapping, granting and unmapping, any policy can be implemented for constructing address spaces. But one point remains open: What happens if a thread accesses a not present page? As described above, a pagefault is raised by the hardware when either the page is not present or was mapped read only and is written to. The  $\mu$ -kernel receives this page fault exception and translates it into an IPC to the pager of the faulting thread. This pager can be specified through the systemcall lthread\_ex\_regs and is a thread being established to handle pagefault messages. With this mechanism, any reasonable paging policy can be implemented.

#### 2.2.3 Address space creation

Address spaces can be created and deleted through the system call task\_new. This systemcall automatically initializes the data structures needed for an empty address space and creates the first thread in this address space, which then can create the other threads with lthread\_ex\_regs. L4 Version X was build around a task concept. A task is an address space with a set of threads, sharing this address space. The next  $\mu$ -kernel Version 4 X2 will weaken this concept by creating the address spaces of the threads implicitly. Threads that are supposed to share the same address space can be created by specifying the thread, whose address space to share with.

The first thing this newly created thread will do when being started is to raise a pagefault on its code page, since the address space was created empty. This pagefault is send to its paging thread which is now able to fill the address space with content using the mapping IPC.

Up to now, we have learned about how to multiplex the CPU and memory and how address spaces establish protection between threads of different address spaces. Threads within the same task can interact easily via their shared memory. However how to interact with threads outside an address space?

#### 2.3 Inter-Process Communication

Inter-Process Communication (IPC) is a mechanism to overcome the restrictions introduced by address spaces. An IPC enables that the two communicating threads can exchange data (a few bytes only, several strings, or map or grant memory pages). IPC is synchronous, which means both partners have to agree on the communication. In particular the first blocks until the second is willing to perform the communication. While waiting for the partner thread to start the send / receive phase of the IPC, this thread will be inactive. To avoid that one of the communicating thread can compromise the others data, the receiving partner has to specify the destination, where to map or copy the data, while the sender has to specify which data to transmit. In addition, both partners can specify two timeout values. The first one specifies the time that the sender / receiver is willing to wait for the partner to get ready for

the transmission.

The second timeout limits the time for the partner's pager to handle page faults that may happen during an IPC. While the first timeout allows to react to a never responding threads, the second is needed to avoid attacks by a never responding pager.

Figure 4: Uniprocessor IPC path

With this mechanism communication between untrusted partners (like a client with a server) can be established. A typical scenario is a call (i.e. an atomic send and receive operation) from the client to the server with timeout infinity, because the client trusts the server to do the job, followed by a reply and wait (a send to the specified thread followed by a receive from any thread) from the server with timeout 0. The server does not trust its clients and will discard the message if they are not listening to the answer (timeout 0). In this scenario, the send phase of the call from the client corresponds with the receive phase from a reply and wait operation from a previous job to trigger the job on the server side. When the work is done, the send phase from the server's reply and wait operation corresponds with the receive phase of the call. After answering, the server is waiting (ready to receive) the next job, while the client that was waiting for the servers answer is released and continues.

Though IPC is required for inter task communication only (intra task communication could also be handled though shared memory), IPC works for intra task communication as well. Since most client-server protocols require only very short messages, special optimizations are done for very short messages that fit into registers.

#### 2.4 Mirroring and Control of the Processor

The preceding sections showed how the CPU and memory of a processor can be multiplexed. However the  $\mu$ -kernel has to fulfill another purpose: mirroring the processor features.

Since these special features are highly platform dependent. Some are even processor stepping specific (like the performance monitoring facilities), I will describe only another two examples: Interrupt and Floating Point Unit multiplexing.

• Floating Point Unit: L4 multiplexes the Floating Point Units FPUs to enable concurrent accesses of several threads. This requires to save the state of the floating point unit including all registers on each thread switch. The next time, this thread gets the CPU, the registers have to be restored again.

The Intel x86 hardware allows the FPU to be secured from accesses through others. Any access to a secured FPU raises

a fault. L4 catches this fault and if the same thread has caused the fault, no registers have to be saved. Only when a different thread accesses the FPU, the registers are saved to the old thread's TCB and restored from the new one's.

Interrupts: In a monolithic operating system, the bottom half interrupt handler is directly attached to an interrupt. This handler is usually invoked in a disabled interrupt state to avoid another interruption before the handler can set-up the information for the upper half handler.

In a  $\mu$ -kernel based system, multiple of those handlers may coexist. Some may require direct control of the interrupt line, like the bottom half handlers or specialized interrupt handling routines. Some others may be satisfied with an acknowledgment that a specific interrupt has occurred, like the top half handlers.

L4 installs an internal interrupt handler for each line, that translates the interrupt into an IPC from a "hardware thread" to the handling routine, that waits for that interrupt (receive from hardware thread). With this mechanism, it is achieved that high priority threads are preferred compared to lower priority interrupt handlers. We may even distribute interrupts to a pool of handler threads. This is similar to a multithreaded server.

Up to now, we know how the uniprocessor L4  $\mu$ -kernel works and that it is easy to build operating system servers on top of L4 like user level pagers and drivers. We know threads and address spaces as two major  $\mu$ -kernel objects and IPC as a communication mechanism between threads. The next section should give an understanding of the SMP hardware features of the Intel Pentium processors which is the targeted platform for the implementation part. For the design section, the Pentium hardware is general enough to get a basic idea has to design a  $\mu$ -kernel for other architectures, too. Though certain parts may be different the behavior of the Intel Pentium hardware can be generalized to other SMP platforms, i.e. similar orders of magnitude in the latencies of memory accesses can be considered on cache coherent SMPs, though the exact implementation of the coherency protocol and of course the exact access times may differ a little bit.

# 3 Pentium Hardware Support for Cross-processor Communication

Intel x86 SMPs couple the 2 to 8 functionally identical CPUs through a memory bus with main memory modules. Bus accesses are guaranteed to be atomic. In addition, the bus can be locked to establish atomic read-modify-write operations. Memory accesses are not ordered with respect to the other processors, but the accesses of any single processor are observed by all the others (i.e. they are snooped by the cache coherency protocol).

#### 3.1 The Memory Hierarchy

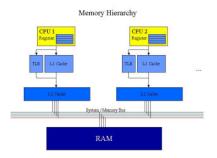

Two fast memory modules (Level 1 and Level 2) represent processor local caches. Whenever an access misses in the L2 cache, the request is transmitted through the bus and carried out in one of the memory modules. In addition, a bus snooping MESI protocol establishes cache coherency. Both caches have 32 byte wide cachelines which are usually organized in 8 banks of 4 bytes each.

Figure 5: Intel Pentium SMP memory hierarchy

The L1 caches are virtually indexed and physically tagged and in size and associativity exactly that large, that the index information can be extracted out of the physical bits <sup>5</sup> of the virtual address. On a read or write, the index of the address is put in parallel into the L1 Cache and the Translation Lookaside Buffer TLB, that caches the least recently used translations from virtual to physical addresses. When hitting in the TLB, the physical address is compared to the tags of the selected set of the cache and the data is delivered on a match. In the case that none of the L1 tags matches, i.e. the L1 cache misses, the address is put into the physically indexed and physically tagged level 2 cache. If the TLB misses, that is when no translation exists for this virtual address, the MMU is triggered to parse the 2 level deep page tables <sup>6</sup> and refills the line in the TLB. The page table entries itself are cached in the L1 and L2 cache and read from it on a TLB miss. This is possible because the L1 cache is at the same time virtually and physically indexed (see above).

#### 3.1.1 TLB Shootdowns

The processor local Translation Lookaside Buffers are used to cache the least recently used translations of virtual to physical addresses.

When switching to another address space, the same virtual page may point to a new physical page frame. Without TLBs, switching the page directory is sufficient, because an access to the virtual page requires to walk the page tables and translates to the correct, that is the new physical frame. Taking TLBs into account, a translation of the same virtual page to the old physical frame may be cached. Accessing the page would hit in the cache and finds the translation to the old frame, instead of walking through the page tables. This inconsistency may result in compromising the old address space. To avoid this, the cached TLB translations of the old address space have to be removed, i.e. the TLB has to be flushed.

To avoid this flushing, tagged TLBs were developed. In addition to the two addresses a number representing the address space ID is stored in the tagged TLB. Complemented by that ID, the virtual addresses differ and thus need not to be deleted explicitly. Untagged TLBs like offered by the Pentium processors do not store this additional information. Due to this lack, virtual to physical translations may be cached, though the corresponding entries in the page tables have been changed. To keep the TLB consistent, the modified translations have to be flushed so they are reloaded the next time, the page is accessed. Especially when switching to another address space, the TLB have to be flushed and reloaded.

<sup>&</sup>lt;sup>5</sup>the lower 12 bits of the virtual address specify the offset within a 4KB pages.

<sup>&</sup>lt;sup>6</sup>Intel calls these page tables page directory for the first and page table for the second level

The Intel Pentium offers two instructions, to invalidate parts of the TLB: invlpg invalidates a single line, mov cr3 reg loads a pointer to a page directory (specified in reg) into the page directory base register (PDBA or CR3) implicitly flushing the entire TLB. Both instructions work only processor local.

As an immediate result, deleting one or more page table entries (Mapping a page to an occupied location is specified to unmap the old page first. The implementation does no real unmap, but overwrites the old page table entry. Switching to a new address space can be viewed as deleting the entire page table.) has to result in triggering the invalidation of the corresponding translations in all TLBs. Even those of the other processors. This operation is called TLB shootdown.

#### 3.1.2 Cache Coherency

The Pentium processor has two caches L1 and L2 to hide memory latency. The caches are kept coherent even in SMPs. This means, that reading a value from the caches will always return the last modification, even when done by another processor. A bus snooping MESI protocol establishes this coherency.

MESI stands for the possible states of a cacheline: exclusive modified (M), exclusive unmodified (E), shared unmodified (S) and invalid (I).

Initially the cache is in invalid state (I). When reading, the line is filled and becomes exclusive unmodified (E). Writing to an exclusive or invalid line would change the state to exclusive modified. In the latter case the contents of the line is loaded from the underlying cache / memory before the write is performed. When a second processor P2 reads a line that is in exclusive unmodified (E) state in P1's caches, i.e. was read before, the read is snooped by both processors. Instead of P2 changing to exclusive unmodified, both processors will change the state to shared unmodified (S) noting this line is in some other processor's cache, too. When writing to a shared line or a line not in the local caches (exclusive unmodified in P1's cache when P2 is writing), any processor, that holds this line (P1), snoops the write and invalidates it before the write is performed. When reading or writing to a line that is modified in the other processor's caches, the write is snooped similar to the last example. But before invalidating, the processor holding the line (P1) writes it through to memory, so P2 can read or write to it. Modern chipsets no longer write through to memory and then read again from the memory chips, but in parallel snoop the contents written back to memory from the bus into the cache. For the read operation, both cachelines are in shared state afterwards.

# 3.2 MESI, Cache and TLB Performance

In the last sections we learned how caches work, how the MESI protocol establishes cache coherency and what to gain from TLBs. This section should give an overall idea of how that hardware performs. I will not describe any pathological cases since those special cases occur very infrequently if at all in reality.

The measurements were done on a dual PIII SMP with a 450MHz CPU, a 16 KB 4 way set associative level 1 and a 512 KB level 2 cache. The processors were plugged in a 440BX board with 100 MHz memory bus frequency and a 64 MB RAM.

#### 3.2.1 Cache and Memory access times

To get a feeling about the order of magnitude of accessing cached data compared to non cached date, I consecutively read a dword from memory addresses, that correspond to the first dword of different cachelines and measured the delay of that operation with a CPU internal cycle counter. To avoid side effects, I read one byte of each page in advance, assuring that a valid translation is cached

in the TLB. To generate L1, respectively L2 misses, the caches were flushed by reading some other data that clashes with one to be used for the measurement. To get the overhead of the measurements itself, I also read a dword directly from a register. After preparing the caches with loading the data, followed by to flushing of specific parts I measured:

- 1. reading 256 dwords from register

- reading 256 dwords that hit in the L1 cache. Each dword was read from a memory location that would be stored in a separate cacheline.

- 3. reading 256 dwords / lines that misses in the L1 cache, but hits in the L2 cache.

- reading 256 dwords / lines that misses in the L1 as well as in the L2 cache.

on a single processor while the other one was idling without accessing the memory bus in between. Table 1 shows the cycles spent for the entire loop, a single iteration of the loop, the time needed for reading the line, without the overhead of the measuring loop which are the cycles per iteration subtracted by the iteration cycles for register reads. The last column is added to get an idea what is happening on the memory bus. The cycles spend for reading a line are transformed according to the frequency of the memory bus. 1 memory bus cycle equals  $4.5 = 1*450 \, \mathrm{MHz} / 100 \, \mathrm{MHz}$  processor cycles. So while only one tick is available to transmit data for the memory bus,  $4.5 \, \mathrm{ticks}$  have to be spent in the CPU.

|          | cycles per | cycles per | cycles   | memory bus      |

|----------|------------|------------|----------|-----------------|

|          | 256 lines  | iteration  | per line | cycles per line |

| Register | 571        | 2,20       | 0,00     | -               |

| L1 hit   | 815        | 3,18       | 0,98     | -               |

| L1 miss  | 2491       | 9,73       | 7,53     | -               |

| L2 miss  | 11462      | 44,77      | 42,57    | 9,46            |

Table 1: Average times for cache and memory accesses of a dual PIII 450 MHz

The results show, that accessing data within the L1 cache can be done in one cycle. Actually two cycles are needed for L1 accesses, but two requests can be handled in parallel which results in a 1 cycle average. Missing in the L1 but hitting in the L2 cache takes about 8 to 10 cycles, delaying a program by one order of magnitude, if the reads are not hidden behind the computations. Data missing in the L2 cache, has to go through the memory bus to the RAM modules, leading to a delay of almost another order of magnitude (another factor of 5).

This result shows, that it really pays to reuse data in the L1 cache. In the PII and PIII processors, certain prefetch operations are included into the processor core that may be used to load data into the L1 or L2 cache in advance, provided the bus is free and the prefetch command can be setup early enough.

#### 3.2.2 MESI performance

Table 2 shows the performance of the MESI protocol for the same experiments like above with the difference that the same data is read or written to by two processors. In order to do the measurements, the cache on the first processor was prepared to hold 2 times 256 dwords exclusive unmodified in the L1 cache, i.e. a read on this processor would hit the line, and 2 times 256 dwords (lines) in modified state. Like in the experiments above, the addresses of the data is chosen such, that each of the dwords accessed would be

cached in a separate cacheline. Given that preparation the measurement code will find the data in the caches in the right states. One after the other, the following operations are performed by the second processor:

- 256 dwords are read, that were prepared to be in the first processor's caches in exclusive unmodified state. So the same 256 dwords were read before by processor one. The lines in both caches change to shared state. E to S.

- 2. As above, except that the 256 dwords, that formerly were in exclusive unmodified state in the first processor, are written by the second processor. This results in invalidating the lines in the first and setting them to modified state in the second processor's caches. **E to M**.

- The next two experiments operated on modified data, i.e. on data that was written to by the first processor. First, the dwords are read by the second processor, leading to change the state of the lines in both processor's caches to shared unmodified. M to S.

- Second, the dwords were written by the second processor, leading to an invalidation of the lines in the first processor and the caching in modified state on the second. M to M.

- 5. The last experiment operated on shared lines, i.e. the dwords are present because of former reads in both processor's caches. In this experiment, the second processor writes the dwords leading to an invalidation of the lines in the first cache, and changing the lines to modified state. In contrast to the M to M case, the lines have not to be read into the caches before. S to M.

|        | cycles per | cycles per | cycles   | memory bus      |

|--------|------------|------------|----------|-----------------|

|        | 256 lines  | iteration  | per line | cycles per line |

| E to S | 16902      | 66,02      | 63,82    | 14,18           |

| E to M | 13212      | 51,43      | 49,23    | 10,94           |

| M to S | 23482      | 91,72      | 89,52    | 19,90           |

| M to M | 23448      | 91,59      | 89,39    | 19,90           |

| S to M | 13211      | 51,43      | 49,23    | 10,94           |

Table 2: Measurement of the MESI protocol timings for the same loop

The results show, that snooping a read on a unmodified line requires about 1.5 the time of a L2 miss, because the cache has to read the line from memory and to wait for the second cache that is snooping the read, to modify the state of its lines from exclusive to shared. When a modified line is involved, the costs double. In that case, the line has to be written back to memory when snooping the write, even if the second cache would modify the line again. Note that the dirty lines have to be written to memory, before they can be read into the second processor's cache in the 440 chipset, the written data cannot be snooped from the bus in parallel. Writing a line results in reading it first, because the modifications may be done to parts of the line only.

In the last experiment, writes to a shared line were measured. In this case, the contents of the line has not to be written back to memory, but the cache lines have to be invalidated in the first processor's caches.

#### **3.3 APIC**

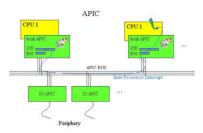

The Advanced Programmable Interrupt Controller (APIC) extends the hardware interrupt mechanism by additional interrupt lines, a clock and the possibility to trigger software interrupts in other CPUs. To accomplish that, the APIC network consists of three different units: the local APIC, the IO-APIC and a three line APIC-Bus. Each CPU has a build in local APIC that allows to handle processor local devices and contains a cycle counter derived from the memory bus clock that can be programmed to trigger timer interrupts. Each IO-APIC chip receives additional 240 hardware interrupts (int 0 .. 15 are reserved) and delivers them through the APIC-BUS network to the least loaded or one selected CPU's local APIC. Least loaded in this case means that the processor with the lowest priority is selected. When receiving an interrupt, this priority is raised. Compared to the 21 cycle short message for delivering interrupts to a fixed location (see below), a 34 cycle bus message is used that is send to all processors. Each processor's local APIC publishes its inverted priority for this case and that with the lowest priority wins and receives the interrupt. In the same way that the IO-APIC triggers an interrupt in a CPU, the local APIC chips deliver Inter Processor Interrupts (IPIs) to other processors

For our purpose, IPIs are the most interesting feature of the APIC, because they can be used to trigger some action in the other processors. The sender, processor A initiates the inter processor interrupt by writing its number into the Interrupt Command Register (ICR). The destination processors can be selected through a mask in the upper most byte of the ICR. Setting the  $n^t h$  bit selects the  $n^t h$ processor as the target. In this mode, any group of the at most 8 processors can be selected as a target for the IPI. There are further modes for machines with more than 8 processors, but in those, the any-cast facility is lost, so either the APIC can deliver the interrupt to one specific or all processors. The local APIC hardware acquires the APIC bus, selects the target and initiates the interrupt. On the target processor B, the currently running thread is interrupted (provided the interrupt was not masked) and the interrupt handler code is activated. Though IPIs are software initiated, for the target processor they are identical to hardware interrupts because they happen asynchronously to the executing code. To acknowledge the interrupt, the handler code on B can send an End of Interrupt (EOI) message back to A, however A has to poll for this answer if it is required. If A does not need an acknowledgment it may continue.

Figure 6: The Intel Pentium APIC and its network

#### 3.3.1 IPI Performance

To evaluate the IPIs, two numbers are of interest: obviously 1. the time required to deliver the IPI and 2. the time, the target processor is interrupted for handling the IPI interrupt.

1. IPI delivery time: The APIC bus is three lines wide and runs at a frequency of 16 MHz. One of the lines is used as a clock, the remaining two for data. A short interrupt message, i.e. a message to a fixed destination requires 21 cycles on the APIC Bus: 4 for Arbitration, 3 to specify the mode, 4 (8 bits) for the interrupt number which can be up to 256, 4 (8 bits) to specify the destination plus some checksum, status idle and normalize cycles. On a 450MHz PIII this would sum up to roughly 590 processor cycles (Note one APIC bus cycle corresponds to 450 / 16 ≈ 28 processor cycles).

I measured the time needed until the interrupt is delivered to the target. To achieve this, the destination processor B polls for the interrupt request register (IRR) in which a bit per interrupt is set, if the request comes in. The target processor B copies this information into some memory location, where the sender polls for. While polling and copying, the interrupts are disabled, so that the polling is not interrupted. A measures the time between writing the ICR, i.e. sending the IPI and receiving the acknowledge in the memory location updated with the IRR contents.

But why not measure in the interrupt handler? At first it is not for sure that the cycle counter is synchronized. So reading at the same time from the two processor local counters (on A and B) may return different values. On the other hand, the destination processor B has to finish the currently executed instructions, flush the pipelines, refill the pipelines with the interrupt handler code that has to be looked up first in the interrupt descriptor table, change the privilege level and so on. All this activity take quite some time (roughly YYY cycles) and varies because of many reasons. Compared to that, triggering the send in the ICR takes about 40 cycles plus another 20 for polling for the IRR to change. Additionally we have to modify a shared line on B and reread it on A, but for this we already know the time needed, which sums up to 50 + 90 = 140 cycles. This sums up to additional 200 cycles.

The measurements resulted in 1230 - 1250 cycles to deliver an IPI and detect this in the above described manner. The estimated value was 590 + 200 = 790 cycles. The remaining 450 cycles (note this are 16 APIC Bus cycles only) can be explained by the work, done in the APIC state machine, before the IPI is send over the APIC bus.

2. **Interruption time:** the second value of interest is the time, the destination processor B needs to handle the interrupt triggered by the sender A. To measure that, a thread reads the clock in a closed loop. When being interrupted, the interrupt handler stores the value read by the user level thread before being interrupted and sets the loop condition to finish after the clock was read one more time. The difference of the two values minus the time needed to store the first and set the break condition is the time spent to enter and exit supervised mode and invoke the interrupt handler. If in addition, the handler code itself reads the cycle counter, a distinction between the two phases: enter kernel mode and activate handler, and returning to the interrupted thread again, can be distinguished. In the Pentium processor, the hardware pushes the eflags register, stack and instruction pointer of the user level thread on the kernel stack. The EFLAGS register contains the state of the processor immediately before the interruption. For the loop break condition, the carry flag is used. The handler can modify this flag by resetting it on the kernel stack, where it was pushed when entering supervisor mode. When returning to the user level thread, the EFLAGS register is popped automatically. In contrast to the EFLAGS register, the general purpose registers are not pushed on the stack automatically. So they can be modified by the handler code directly when being used. The current system timestamp is read into the processor registers immediately before the interrupt and immediately after entering the handler code giving the cycles needed to switch from user level code to kernel mode into the handler code.

For the kernel entry phase I measured between 120 to 160 cycles. The exiting phase costs between 170 to 250 cycles. Including the privilege level change from user to kernel and back to user mode.

In total roughly 1030 (1230 - 200 for the polling) cycles after the sending processor A writes its ICR to trigger the IPI, the interrupt arrives on the destination processor B. B then enters supervisor mode (provided the interrupt was not masked) and activates the interrupt handler 120 to 160 cycles later. So about 1200 cycles after processor A triggered the IPI, the handler code gets activated. The currently running thread on processor B is interrupted for 290 to 410 cycles plus the time needed for executing the handler code. No further interrupts of a lower or equal priority can be received by B's local APIC until B ends A's interruption by writing an arbitrary value to the End Of Interrupt EOI register of the local APIC. So to sum up, every 1200 cycles (2  $\mu$ s) an IPI can be received by the target processor B, that interrupts the currently running thread for about 400 cycles ( 1  $\mu$ s). All at all, up to one third of the available processor cycles may be spent in handling inter processor interrupts. Two things can be concluded from this:

- 1. Inter processor interrupts should not happen more frequently than once per 100  $\mu$ s to get no more overhead than 1% of the processor cycles.

- 2. Kernel entries and exits should be avoided if possible.

# 4 Outlook of the Paper

The last two sections gave a brief introduction to the L4 uniprocessor  $\mu$ -kernel, on which the following design is based on, and to the Pentium hardware that is relevant mainly for the implementation part of this thesis (see Section 8).

The remaining part of this paper is structured as follows: Section 5 describes the major design goals of the L4 SMP  $\mu$ -kernel and section 6 the design itself. Section 7 summarizes the changes to the system calls that are effected by the design decisions. In section 8, the implementation issues on a Intel Pentium hardware are described. Sections U and V explain the open points and conclude the paper.

#### 5 Goals

There are six major goals for the SMP  $\mu$ -kernel design:

- 1. Flexibility

- 2. Generality

- 3. Performance

- 4. Compatibility

- 5. Transparency

- 6. Non Transparency

The *Compatibility* and *Transparency* goals are required to provide backward compatibility to existing uniprocessor code. Such software should not need to be modified to run properly on the SMP  $\mu$ -kernel. The *compatibility* goal ensures the interface compatibility, while the *Transparency* goal ensures the compatibility of the SMP  $\mu$ -kernel mechanisms compared to the uniprocessor ones. In particular this means that a task designed for an uniprocessor  $\mu$ -kernel should not have to care about SMP extensions.

The *Non Transparency* goal, however, enforces the support of SMP specific applications (like parallel numeric programs - for example matrix multiplication) and servers (like network or load balancing servers).

# 5.1 Flexibility / Generality

The basic idea of the  $\mu$ -kernel approach was to provide basic mechanisms to implement any reasonable policy in user level servers. To achieve this, the  $\mu$ -kernel mechanisms have to be as flexible and as general as possible.

This particular goal has already lead to the design of the uniprocessor L4  $\mu$ -kernel and hopefully will hold as well for SMP  $\mu$ -kernels.

#### 5.2 Performance

An application or server, designed to run on a uniprocessor, should have the same execution time running on the uniprocessor machine as well as on a specific processor of a SMP.

The bottleneck of tightly coupled SMP architectures is the memory bus. It connects the processors and DMA chips with the memory modules, but only one processor or DMA chip may acquire the bus at one time. Because of memory bus contention, tasks accessing memory on an SMP may lead to even worse results than if running on two separate uniprocessor machines. Some preliminary ideas dealing with these effects are presented in [1, 3]. The solution of this problem however is out of the scope of this paper.

Never the less, the  $\mu$ -kernel mechanisms should not suffer from SMP side effects and therefore have to be carefully designed and implemented.

#### 5.3 Compatibility

Existing L4 application and OS servers should run on the SMP  $\mu$ -kernel without modification. This means that the system calls have to keep their functionality and binary interface or at least we have to provide backward (uniprocessor) compatible interfaces.

Some applications may rely on uniprocessor specific synchronization mechanisms, like disabling interrupts. Those unconsciously designed applications will not be supported any longer in the SMP  $\mu$ -kernel and may fail.

#### 5.4 Transparency

In the large, it should be possible to construct and implement applications and system servers such, that how its threads are assigned to the processors of an SMP does not effect their functionality. In the small, a thread should see no functional difference whether its partner thread is on the same or a different processor.

#### 5.5 Non Transparency

Though at the first look, this goal contradicts to the *transparency* goal, both have to be taken into consideration when designing a SMP  $\mu$ -kernel. While the *transparency* goal requires to hide SMP specific situations from existing uniprocessor applications to avoid modifications in the code, the *non transparency* goal requires to

give user-level programs access to SMP specific features (like the migration of threads) in a secure and comfortable way.

# 6 SMP specific $\mu$ -kernel Design

The measurements of the cache MESI protocol show that the latency of accesses to shared data structures differ only slightly, assuming the data reads have to fetch from main memory. For cached data instead, the delay for cross-processor reads and writes cannot be neglected. This holds in particular for performant critical kernel mechanisms like IPC. Additional synchronization overhead adds to this, when synchronization is required.

In the Pentium processors, only read and write operations are guaranteed to be atomic. Some read-modify-write operations can be made atomic by locking the memory bus during their execution. However with none of those operations, more than one dword (4 bytes) can be modified <sup>7</sup>. So software synchronization primitives like spin locks and semaphores are needed when having to synchronize complex operations.

In the L4  $\mu$ -kernel only few "global" i.e. shared  $\mu$ -kernel data structures, can be identified. Basically only mapping data including the page tables and the coarse-grain wakeup queues are of such type and have to be protected against cross-processor access. None of those structures are used by time critical operations.

Thread Control Blocks (TCBs) and the ready queues, require similar cross-processor access synchronization only if we decide to have fine-grain inter-processor scheduling (dispatching) of threads, that is if the dispatcher selects the next thread from a global pool of ready threads. In that case, we would have to explicitly synchronize every dispatching access to a TCB, even to the current TCB to avoid inconsistencies. If not, per-processor dispatching data structures and some IPC tricks (see below) would enable us to manage TCBs such that cross-processor accesses can be restricted to very special cases: cross-processor IPC, explicit migration to a new processor and cross-processor TCB accesses by the system calls lthread\_ex\_regs and thread\_schedule. None of those operations – remember only cross-processor operations are listed – seems to be first-class time critical.

# 6.1 Processor Scheduling Granularity and Migra-

When pinning a thread – from its birth to death – to one specific CPU, fine grain scheduling automatically works locally only. However, restricting a  $\mu$ -kernel to this simple design contradicts the *flexibility* goal. In multiprocessor operating systems, several load balancing policies have been proposed, making use of thread migration in case of overload situations. To support those kind of policies, the  $\mu$ -kernel has to offer some basic mechanism to migrate threads. At first the granularity of such a migration mechanisms is examined. This inflame when and how frequently threads may migrate. (The discussion of how to migrate threads is postponed for the time being.)

#### 6.1.1 Implicit transfer through the dispatcher

Some older SMPs with small cache memories permitted quite inexpensive transfers, nowaday SMPs do not. Transferring a thread with a working set of 50 dirty lines and 50 read only lines – we

<sup>&</sup>lt;sup>7</sup>Note: the Pentium string operations are implemented as a loop of a single operation. Each iteration can be set to be atomic, but not the entire loop

assume that these lines are at least in the L2 cache – would require roughly 90 cycles per dirty and 65 cycles per read only (exclusive) line which sums up to 7750 cycles (see section 3.2). Between 4500 and 7750 cycles (  $10 - 20\mu s$ ) on a PIII dual 450 MHz SMP are required to transfer only the dirty (minimum time) or all (maximum time) lines of this thread's working set. It can be assumed that the threads to be migrated have most part of their current working set at least in the L2 cache. If not, it means that either this thread is not scheduled for a long time, or that its working set was replaced due to clashes with other frequently used threads. For the first case, this thread will not be the primary target to reduce the load of one processor. The latter case should be avoided by system design or by cache coloring techniques.

The cycles needed to transfer the working set can even be worse on machines with 4 or more processors because of memory bus contention, i.e. due to concurrent bus accesses of the remaining three processors (the source processor is not actively involved in this transfer and may run another threads in between). Caches contravene this delay, because accesses hitting in one of the caches and not triggering cache coherency actions, do not require to access the memory bus. In addition to that, there exists data that cannot be cached effectively (i.e. video stream data or accesses to a large database in a randomly or hashed manner). This analysis is e.g. corroborated by the analysis and experiences of the K42 project [5].

To sum up, executing a thread transfer more often than ones per  $200\mu s$  seems to be unreasonable. This leads to

• Design decision 1: Fine grain scheduling will not implicitly transfer threads to other processors. Migration has to be initiated by a user level scheduler.

There are three immediate conclusions from design decision 1:

- Dispatching and fine grain scheduling works processor local, this implies that ready lists and "short wakeup queues" have to exist per processor.

- The system call thread\_switch switches to processor local threads only. Specifying a non local thread works as if nilthread was specified. In that case, the next ready and local thread is selected to run.

- 3. The  $\mu$ -kernel has to offer some mechanism to let a user level scheduler migrate threads.

# 6.1.2 How to migrate threads

Concluding from *design decision 1*, the migration requests will be initiated by a user level server. On the other hand it is obvious, that some  $\mu$ -kernel intervention is required, because threads are  $\mu$ -kernel objects. We still have to decide what type of intervention is required for migrating threads.

The symmetry of the SMP architecture makes the decision on which processor to run a thread independent from special features of some processors in the system. Processor local vector computing units for example need not to be taken into account.

The load of the system is controlled by user level scheduling servers, that have to keep track of all relevant information i.e. indicators of the load of the processors by themselves.

Because migration decisions are triggered by user level schedulers, an in kernel migration mechanism has to consider the thread transfer, only.

When migrating a thread from one CPU to another, its TCB has to be deleted from all local data structures on the source processor and reinserted into the destination processor ones. Note, *design*

decision 1 lead to processor local ready and short wakeup lists for example.

One possible way is not to support a special migration mechanism, that moves existing threads around, but instead to use the thread creation and deletion mechanism. Migration would then mean to delete a thread on one CPU and create a new thread on the destination processor. When implementing migration in that way, the current state of the thread would be lost, so it has to be saved before the deletion and restored afterwards. However the kernel internal state is not available in user level, i.e. the list of sending threads, that are waiting for the thread to enter the receive path, is present inside the kernel only. A second counterargument is the time needed to create and delete a thread. Creating a thread requires to build up and initialize a new TCB, which costs some time. Additionally, the old TCB information cannot be reused without restricting the delete operation.

Third, the current kernel implementation does not support real thread deletion. A thread can be aborted by the  $\mu$ -kernel or through lthread\_ex\_regs, but its TCB will never be released. This leads to

• Design decision 2: Migration has to be initiated by a system call

A system call is needed to migrate threads. Obviously this call has to be somehow protected to avoid attacks against the load balancing and scheduling system (i.e. by migrating all threads to one CPU). We extend the system call thread\_schedule, that already controls the other scheduling parameters like timeslice and priority by a parameter to specify the current processor. Changing this parameter will migrate aimed thread to the specified processor.

The thread\_schedule can only be used by threads with a higher MCP. The maximum controlled priority (MCP) value of the scheduler thread specifies the highest thread priority it is allowed to control. Only the scheduling parameters of threads with a lower priority than the MCP value can be modified with thread\_schedule. Normal, non scheduler threads, will have a MCP of 0, so they are not allowed to modify the scheduling parameters of any thread in the system. In the next  $\mu$ -kernel version, a specific scheduling server is specified for each thread. Only this thread is allowed to modify the scheduling parameters and by this to migrate.

So far, a thread can be migrated by a system call, initiated from a user level scheduler. It will not be migrated by the dispatcher of the kernel. Next we have to discuss some situations where the thread itself may want to migrate, i.e. to be mobile.

#### 6.2 Thread Mobility at $\mu$ -kernel Level

Mobility is a thread's ability to migrate itself between several processors.

Design decision 1 already rejects that  $\mu$ -kernel dispatching migrates threads and also concludes in a way to let user level scheduling and load balancing servers migrate threads by extending thread\_schedule.

However, two possible scenarios remain: restricted explicit thread transfer and implicit mobility on IPC.

#### 6.2.1 Restricted Explicit Thread Transfer

Explicit thread mobility would enable application threads to migrate to other processors by themselves. Though nice to have, i.e. to automatically parallelize a problem for computation and join again to compute the results, this functionality has to be restricted to protect certain processors (i.e. those dedicated to realtime threads).

However since migration costs are about 1 to 2 orders of magnitude higher compared to a call to a local scheduling server and since more frequent migrations than once per  $200\mu s$  result in drastically

down performing the system, the additional short IPC per migration to contact a user level scheduler is neglectable. From the policy point of view it is always preferable to contact a user level server when this additional performance loss does not hurt. This server can implement an arbitrary migration policy and i.e. protect processors dedicated to realtime threads from being burdened with additional load.

To sum up, explicit mobility will not be implemented by the  $\mu$ -kernel. Instead a user level scheduling server should be contacted which is able to migrate the thread using the thread\_schedule systemcall.

#### 6.2.2 Implicit Mobility on IPC

A somehow similar scenario is implicit mobility due to an IPC. For performance reasons, a server or a client thread may want to automatically migrate to the partner's CPU to be able to process on local and presumably cached data. Another reason might be to improve the performance of following IPCs to the partner. If both partners have to communicate frequently in the near future, the higher startup costs for cross-processor IPCs can be saved, when migrating to the partners processor at the first IPC. Especially for short IPCs, where the startup costs dominate the overall performance of the IPC, avoiding cross-processor IPC pays. For very long messages, which means that probably not the entire message fits into the caches and that some pagefaults may happen in between the transfer, the higher startup costs for cross-processor IPC are neglectable.

Implicit mobility would allow a thread to specify whether to automatically migrate to the partner's processor on IPC. A server thread that migrates on a receive would always migrate to its clients processors before executing its task. A migrate on send server would migrate to the client thread's processor after it processes its request on the last clients processor. The next obvious idea is to let the server decide on a case by case basis whether to migrate or not.

This example shows that mobility on send / receive is insufficient and that any other, more complicated mechanism would include policy. This makes the mechanism either to restrictive or not general enough and therefore contradicts to the *flexibility and generality goal*.

Provided the kernel implements an efficient detection mechanism for cross-processor IPC, an arbitrary mobility on IPC policy can be implemented by calling the scheduling server after cross-processor IPC was detected. This mechanism should even be preferred from the policy point of view, because the additional knowledge of the desired communication can be taken into consideration for the schedule. I.e. the scheduler may avoid to distribute communicating partners to different CPUs for load balancing reasons. This leads to:

Design decision 3: The μ-kernel will not implement implicit mobility on IPC, but support a fast cross-processor IPC detection mechanism.

#### 6.2.3 Detecting Cross-Processor IPC

Detecting cross-processor IPC is like a "two sided blade". On the one hand it is required to implement arbitrary mobility policies and fast adaptation to the new environment for mobile threads, on the other hand it opens a covert channel by allowing threads to mors a message only by the information on which processor they reside. Section 9.1 describes the problem of covert channels a little more detailed. But since we currently do not know how to deal with

covert channels while having an acceptable performance independent of a fixed security policy, we will ignore the problem for the time being.

When talking about cross-processor IPC detection, two questions have to be answered: When to inform the IPC partners, and what information to deliver?

When to inform the IPC partners? The IPC operation is implemented as a systemcall which means that usually supervisor mode is entered and the kernel IPC code performs the operation on behalf of the threads. The next kernel Version will implement an IPC path for some special flavors of the IPC in user level, but fall back to the within kernel IPC mechanism whenever needed. This means that independent of when to inform the partners, the current  $\mu$ -kernel has to enter and exit supervisor mode. In Version 4, some cross processor IPCs may be detected in user mode, saving the time needed for the switch.

In general, cross-processor IPC can inform the communicating partners before the message is copied or afterwards. In between the copy sequence does not make sense, because no additional benefit can be gained compared to informing before the message transfer. A partly copied message is of no use and has to be copied again. So two potential ways remain when to detect cross-processor IPC: a) IPC signals the invoker that it has been a cross-processor IPC

after the transfer is completed, and b) IPC fails in the cross-processor case before it happens. Conceptionally a) is a trap, while b) is a fault.

XP-IPC detection after the message transfer Mechanism a) extends IPC such, that it reports cross-processor IPC after it happened. Despite the additional costs for moving the message data to the destination processor's cache, the major overhead of cross-processor IPC is in the startup phase. For long messages, this startup costs becomes less relevant, so detection after the message transfer is not critical in those cases, assuming the message has to be delivered anyway. For short messages, the additional overhead of cross-processor versus processor local IPC has to be taken into account. In those cases, detecting cross-processor IPC after the transfer might be to late.

XP-IPC detection before the message transfer Compared to a), mechanism b) informs the invoker before the IPC happens. In the startup phase, the kernel checks whether IPC is going to cross the processor boundaries and fault in this case. If b) is implemented, any thread, even those that do not care about cross-processor IPC, has to implement a recovery mechanism for the cross-processor case. But this contradicts to the compatibility goal and requires code modifications to existing uniprocessor applications, which is unacceptable. To avoid this, the invoker has to specify whether cross-processor IPC should fault or not, so when enabled, the IPC will fail in the cross-processor IPC case. When disabled, this mechanism degenerates to a). Obviously, mechanism b) works only for the send phase of the IPC, that is on a send or a call. For a receive only IPC this mechanism degenerates to a). To avoid the additional overhead of mechanism a), we will implement mechanism b) which can be degenerated to a), by disabling the faulting feature explicitly.

What kind of information will the detection mechanism supply? Basically there are three different levels in the amount of information that is useful to retrieve through such a mechanism:

- the information whether this IPC was cross-processor or not.

A single bit is retrieved that indicates if the IPC was cross processor.

- the partner thread's processor number.I.e. the number of the processors that are participated in the IPC.

- 3. the partner's processor number plus some guaranteed time in which the partner is pinned to this processor. Which means that the processor number of the partner will not be changed within the specified time.