# **Towards Fast and Portable Microkernels**

zur Erlangung des akademischen Grades eines

# Doktors der Ingenieurwissenschaften

von der Fakultät für Informatik der Universität Fridericiana zu Karlsruhe (TH)

genehmigte

**Dissertation**

von

**Uwe Dannowski**

aus Dresden

Tag der mündlichen Prüfung: 12. Dezember 2007

Erster Gutachter: Prof. em. Dr. Dr. h.c. Gerhard Goos

Universität Fridericiana zu Karlsruhe (TH)

Zweiter Gutachter: Prof. Dr. Hermann Härtig

Technische Universität Dresden

# Zusammenfassung

Mikrokerne müssen maximal effizient sein. Als Basis feingliedrig komponentisierter Betriebssysteme stellen sie den Kommunikationsmechanismus zwischen den Komponenten zur Verfügung und spielen damit eine besonders leistungskritische Rolle im Gesamtsystem. Minimale Ausführungszeit und minimale Cachebenutzung des Mikrokerns sind dabei Schlüsselfaktoren. Gleichzeitig sollen Mikrokerne als zentrale Systemkomponente jedoch auch portabel und leicht wartbar sein. Traditionell werden diese Ziele als unvereinbar angesehen, da Mikrokerne für die jeweilige Systemkonfiguration optimiert werden müssen, um ausreichend effizient zu sein.

Aus der hohen Zahl möglicher Systemkonfigurationen eines portablen Mikrokerns ergibt sich ein Komplexitätsproblem. Durch Modularisierung und die damit erreichbare Konfigurierbarkeit kann der Umfang der notwendigen Optimierungen jedoch reduziert werden. Allgemein verwendbare und konfigurationsspezifische Teile des Kerns werden voneinander getrennt, in verschiedenen Modulen platziert und bei der Erzeugung eines Kerns entsprechend der Konfiguration zusammengefügt. Dieses Vorgehen wird bereits erfolgreich im portablen Mikrokern L4Ka::Pistachio angewandt. Durch Unzulänglichkeiten heutiger Programmiertechniken für Mikrokerne — hauptsächlich durch unzureichend feingranulare Konfigurierbarkeit — lassen sich jedoch Probleme wie übermässiger Präprozessoreinsatz und Quelltextduplikation oder, als Alternative, suboptimale Leistung nicht gänzlich vermeiden.

Der Einsatz objektorientierter Programmierung und speziell der Vererbung zum Zwecke der Konfiguration und Komposition von Kerndatenstrukturen ist ein Erfolg versprechender Ansatz, diese Strukturprobleme zu lösen. Konfigurationsspezifische Aspekte der Kernfunktionalität und die dafür benötigten Daten werden in relativ kleinen Klassen gekapselt, die je nach Zielsystem durch Vererbung zu vollständigen Klassen zusammengefügt werden. Jedoch verursacht die flexible Implementierung von Objektorientierung oft einen zusätzlichen Laufzeitaufwand, der in einem Mikrokern nicht tolerierbar ist. Zum einen werden zur Unterstützung dynamischer Polymorphie manche Funktionen durch indirekte und somit nicht vorhersagbare Sprünge realisiert und behindern dadurch eine zügige Ausführung der Instruktionsfolge durch den Prozessor. Zum anderen wird durch die Vererbungshierarchie die interne Struktur von Objekten in einer Weise festgelegt, die eine optimale Cache-Ausnutzung auf dem kritischen Pfad des Mikrokerns verhindert.

Diese Arbeit stellt ein automatisiertes Optimierungsverfahren vor, das es erlaubt, Objektorientierung zur Komposition von Datenstrukturen im Mikrokern einzusetzen, ohne die traditionell damit verbundenen Laufzeitkosten tragen zu müssen. Wissen, das dem Kernprogrammierer bekannt ist, jedoch nicht in geeigneter Weise an den Compiler weitergegeben werden kann, wird dazu verwandt, den Quelltext automatisch so umzuformulieren, dass der Compiler optimalen Code und optimale Datenstrukturen erzeugen kann. Die Transformationsschritte im Einzelnen sind:

1. Das Umwandeln der Vererbungshierarchien ausgesuchter Klassen in einzelne Klassen ohne Vererbung unter Beibehaltung der Schnittstelle der Klassen. Dadurch wird

verhindert, dass der Compiler unnötigerweise Code zur Laufzeitunterstützung für Polymorphie generiert. Da keine Vererbung stattfindet, kann die interne Struktur von Objekten der resultierenden Klasse nun gezielt beeinflusst werden.

2. Das Umordnen der Datenelemente innerhalb der Definition ausgesuchter Klassen, so dass die resultierende Anordnung der Daten innerhalb der Objekte dieser Klassen zu optimaler Cache-Benutzung auf dem kritischen Pfad führt.

Diese Schritte werden — für den Kernprogrammierer transparent — zur Übersetzungszeit vor Aufruf des Compilers durchgeführt. Damit ergibt sich trotz separater Übersetzung der einzelnen Quelltextdateien effektiv eine Optimierung des Gesamtprogramms Mikrokern. Durch die Realisierung der Transformationen auf Quelltextbasis wird kein speziell angepasster Kern-Compiler benötigt, und es wird weitestgehende Unabhängigkeit vom eingesetzten Compiler erreicht.

Bislang war automatisches Umordnen der Felder einer Klasse nur in typsicheren Sprachen gefahrlos möglich. Für Objekte, deren Struktur nicht durch kern-externe Spezifikationen vorgegeben ist, lässt sich die Manipulation der Objektstruktur jedoch auch in typunsicheren Sprachen voll automatisieren, ohne dabei die Korrektheit des Kerns zu gefährden.

Die Entscheidung über die Auswahl der leistungskritischen Klassen im Mikrokern ist unabhängig vom Zielsystem und kann daher statisch erfolgen. Der kritische Pfad und die Zugriffsfolge sind jedoch einsatzabhängig und müssen deshalb während eines Profiling-Laufs bestimmt werden. Dabei kann durch gezielte Ausnutzung von mikrokernspezifischen Eigenschaften eine sehr kompakte und leicht auswertbare Darstellung der Zugriffsinformationen erreicht werden. Beispiele für solche Eigenschaften sind der extrem kurze kritische Pfad sowie die geringe Anzahl der referenzierten Kernobjekte und eine sehr hohe Ähnlichkeit der Zugriffsmuster auf dem kritischen Pfad.

Über die Vermeidung des Laufzeitaufwands der Vererbung hinaus erlaubt das Verfahren, leistungskritische Klassen automatisch für den spezifischen Einsatzfall des Mikrokerns zu optimieren, so dass die notwendigen Anpassungen nicht mehr manuell vom Programmierer vorgenommen werden müssen. Die automatische Transformation des Quelltextes beschränkt sich dabei auf die Definitionen der laufzeitkritischen Klassen. Teile des Kerns, die diese Klassen lediglich benutzen, bleiben somit unangetastet.

Das vorgestellte Verfahren wird exemplarisch auf den L4Ka::Pistachio Mikrokern angewandt und evaluiert. Die Leistung eines Kerns mit Vererbungshierarchie und optimierten Klassen wird der des für eine Architektur handoptimierten Originalkerns ohne Vererbung gegenübergestellt. Dabei zeigt sich, dass das Verfahren die Laufzeitkosten der Vererbung vollständig beseitigt und darüber hinaus bisher ungenutztes Optimierungspotential ausschöpfen kann.

# Acknowledgements

Some say I am a man of few words, so I could do away with this section by thanking all who helped making this work happen. Yet, I would like to express my thanks to some people in particular.

I am indebted to Jochen Liedtke, the father of the L4 microkernel, in many ways. He offered me a Ph.D. position in Karlsruhe and made the System Architecture Research Group a fun place to work, learn, and do research. Jochen introduced me to the Sherlock Holmes debugging style and to Dr. Wagner Riesling, and his fantastic cooking let me eat fish again after years of abstinence. His wit made even the toughest disputes enjoyable. Jochen was a visionary, a great researcher, an excellent teacher, and a friend. He inspired me and many other people for years, and he still does.

I would like to thank my advisor Prof. Gerhard Goos for "adopting" me after Jochen passed away in 2001, for his guidance and especially for his patience over the years. Also, I would like to thank Hermann Härtig, my second reviewer, for the confidence he had in me and for freeing a few hours for my defense in his busy sabbatical calendar.

I am thankful to Volkmar Uhlig, Espen Skoglund, Joshua LeVasseur, and Jan Stöß, with whom I enjoyed working on the Pistachio kernel, as well as to Stefan Götz and Andreas Häberlen, for the creative years with many interesting technical discussions. I also thank the students at UNSW/NICTA who ported the kernel to so many other architectures.

Thanks to Sebastian Biemüller for asking many many questions, for proofreading this thesis, and for the irregular quiz nights at Scruffy's Irish Pub. I would like to thank James McCuller for the most professionally managed IT infrastructure ever and for his critical view on many things. I have to thank Frank Bellosa for supporting my research for a year and for keeping an office for me to work in even after I had left university. I would also like to thank AMD, my employer, for providing plenty of distraction during the last year of this work.

Special thanks go to Adelheid, Jochen's wife, for her friendship and support over the years, and for the lovely evenings with long conversations over experimental cooking and excellent wine. I thank Ahmad for his friendship and support, for advice in so many areas but this thesis, and for the supply of excellent coffee and food during my off-university thesis writing hours at Café L'île. I am grateful to my parents for their constant support from my very beginning, for the occasional nudge, and truckloads of chocolate. Last but not least, a very special Thank You to Sinéad for her love and understanding. Being in thesis write-up mode herself she knew very well what I was going through.

# **C**ontents

| 1 | Intr | oductio                      | on                                       | 1  |  |  |  |  |  |

|---|------|------------------------------|------------------------------------------|----|--|--|--|--|--|

| 2 | Bac  | ackground and Related Work   |                                          |    |  |  |  |  |  |

|   | 2.1  | Cache                        | S                                        | 7  |  |  |  |  |  |

|   |      | 2.1.1                        | Cache Architectures                      | 8  |  |  |  |  |  |

|   |      | 2.1.2                        | Reducing Cache Misses                    | 10 |  |  |  |  |  |

|   |      | 2.1.3                        | Reducing Miss Latency                    | 11 |  |  |  |  |  |

|   | 2.2  | Data S                       | Structure Layout                         | 12 |  |  |  |  |  |

|   |      | 2.2.1                        | Classes                                  | 12 |  |  |  |  |  |

|   |      | 2.2.2                        | Inheritance                              | 13 |  |  |  |  |  |

|   | 2.3  | Progra                       | am Transformations                       | 18 |  |  |  |  |  |

|   |      | 2.3.1                        | Build Process                            | 18 |  |  |  |  |  |

|   |      | 2.3.2                        | Class Flattening                         | 19 |  |  |  |  |  |

|   |      | 2.3.3                        | Field Reordering                         | 21 |  |  |  |  |  |

|   | 2.4  | Kernel                       | l Portability Aspects                    | 24 |  |  |  |  |  |

|   |      | 2.4.1                        | Hardware                                 | 24 |  |  |  |  |  |

|   |      | 2.4.2                        | Software                                 | 27 |  |  |  |  |  |

|   |      | 2.4.3                        | Tools                                    | 30 |  |  |  |  |  |

| 3 | Cas  | se Study: L4Ka::Pistachio 33 |                                          |    |  |  |  |  |  |

|   | 3.1  |                              | ,<br>4 X.2 API                           | 33 |  |  |  |  |  |

|   | 3.2  | Impler                       | mentation                                | 35 |  |  |  |  |  |

|   |      | 3.2.1                        | Configuration Management                 | 35 |  |  |  |  |  |

|   |      | 3.2.2                        | Data Types                               | 37 |  |  |  |  |  |

|   |      | 3.2.3                        | System Topology                          | 37 |  |  |  |  |  |

|   |      | 3.2.4                        | Mixed Programming Languages              | 38 |  |  |  |  |  |

|   |      | 3.2.5                        | Tools                                    | 39 |  |  |  |  |  |

|   | 3.3  | Impro                        | ving L4Ka::Pistachio with Inheritance    | 39 |  |  |  |  |  |

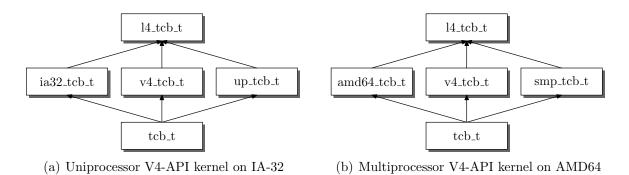

|   |      | 3.3.1                        | Configuration-specific class composition | 40 |  |  |  |  |  |

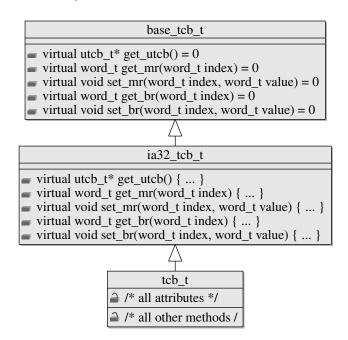

|   |      | 3.3.2                        | Class Properties                         | 42 |  |  |  |  |  |

|   | 3.4  | Inherit                      | tance-related Overheads                  | 42 |  |  |  |  |  |

|   |      | 3.4.1                        | Virtual Function Calls                   | 43 |  |  |  |  |  |

|   |      | 342                          | Object Layout                            | 44 |  |  |  |  |  |

# Contents

| 4 | Elim | ninating Portability Overheads                    | 47 |  |  |  |  |  |  |

|---|------|---------------------------------------------------|----|--|--|--|--|--|--|

|   | 4.1  | Optimizing Performance-Critical Classes           | 47 |  |  |  |  |  |  |

|   | 4.2  | Transparent Class Flattening for Field Reordering | 50 |  |  |  |  |  |  |

|   |      | 4.2.1 Transparent Flattening                      | 50 |  |  |  |  |  |  |

|   |      | 4.2.2 Preconditions                               | 51 |  |  |  |  |  |  |

|   |      | 4.2.3 Flattening Fidelity                         | 52 |  |  |  |  |  |  |

|   |      | 4.2.4 Enforcing Restrictions                      | 53 |  |  |  |  |  |  |

|   | 4.3  |                                                   |    |  |  |  |  |  |  |

|   |      | 4.3.1 Object Roles                                | 55 |  |  |  |  |  |  |

|   |      | 4.3.2 Field Access Mode                           | 55 |  |  |  |  |  |  |

|   |      | 4.3.3 Field Alignment                             | 56 |  |  |  |  |  |  |

|   |      | 4.3.4 Locks and Data                              | 57 |  |  |  |  |  |  |

|   | 4.4  | Determining Field Access Patterns                 | 57 |  |  |  |  |  |  |

|   |      | 4.4.1 Method Review                               | 58 |  |  |  |  |  |  |

|   |      | 4.4.2 Microkernel Specifics                       | 60 |  |  |  |  |  |  |

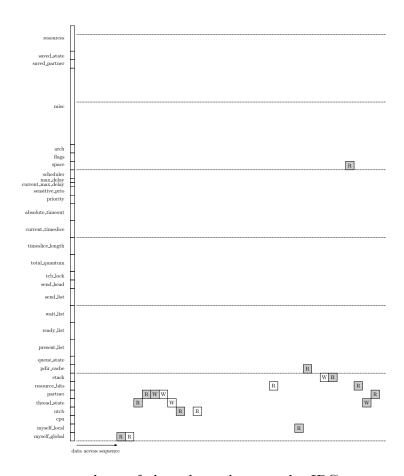

|   |      | 4.4.3 Precise Tracing for Field Reordering        | 62 |  |  |  |  |  |  |

|   | 4.5  | Field Reordering Algorithms                       | 65 |  |  |  |  |  |  |

|   | 4.6  | Optimization Process                              | 66 |  |  |  |  |  |  |

|   |      | · · · · · · · · · · · · · · · · · · ·             |    |  |  |  |  |  |  |

| 5 | Eva  | luation and Discussion                            | 69 |  |  |  |  |  |  |

|   | 5.1  | Evaluation Environment                            | 69 |  |  |  |  |  |  |

|   | 5.2  | Automatic Class Optimization Results              | 73 |  |  |  |  |  |  |

|   |      | 5.2.1 Virtual Functions                           | 73 |  |  |  |  |  |  |

|   |      | 5.2.2 Cache Footprint                             | 74 |  |  |  |  |  |  |

|   |      | 5.2.3 Performance                                 | 75 |  |  |  |  |  |  |

|   |      | 5.2.4 Side Effects                                | 76 |  |  |  |  |  |  |

|   | 5.3  | Optimization Costs                                | 77 |  |  |  |  |  |  |

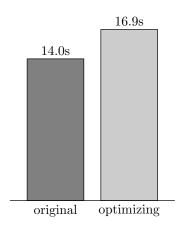

|   |      | 5.3.1 Build Time Overhead                         | 77 |  |  |  |  |  |  |

|   |      | 5.3.2 Code Size                                   | 78 |  |  |  |  |  |  |

|   |      | 5.3.3 Retargeting                                 | 78 |  |  |  |  |  |  |

|   |      | 5.3.4 Maintenance                                 | 79 |  |  |  |  |  |  |

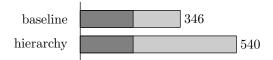

|   | 5.4  | Comparison with Manual Optimization               | 79 |  |  |  |  |  |  |

| 6 | Con  | clusions                                          | 81 |  |  |  |  |  |  |

|   | 6.1  | Contributions of This Work                        | 81 |  |  |  |  |  |  |

|   | 6.2  | Suggestions for Future Work                       | 82 |  |  |  |  |  |  |

| 7 | Bibl | iography                                          | 85 |  |  |  |  |  |  |

# 1 Introduction

Microkernels can and must be fast. A successful microkernel must have minimal cache footprint and execution time. Any overhead in the microkernel reduces the performance of the system on top. Early microkernels failed to deliver on the performance promise, so that despite their conceptual superiority microkernel-based systems suffered from poor acceptance outside a small research community. Lessons learned, today's microkernels are designed and often hand-optimized to add as little software overhead as possible to the bare hardware costs of microkernel operations.

Microkernels must also be portable and maintainable. The complexity of the systems built on today's rapidly evolving hardware forbids write-once software. Even a component as small as a microkernel is too complex (i.e., too expensive) to be completely re-written, re-tested and re-verified from scratch for every new piece of hardware.

These two requirements are traditionally considered to be contradictory. Liedtke [35] even argued that microkernels are inherently nonportable and need to be designed and implemented from ground up for every new processor to achieve the necessary performance. Later he accepted that even a microkernel designed for multiple architectures and written mostly in a high-level language can perform sufficiently well. Key to the excellent performance of such kernels was, however, to avoid the powerful but expensive (in terms of run-time overhead) features of the high-level language.

I argue that object-oriented programming techniques such as inheritance for composition can be introduced to a microkernel to improve its portability whereby its initial performance is at least maintained if not even improved.

A microkernel is a rather contained software environment. The kernel typically is configured statically at build time and no additional code is loaded or generated at run time, so that all the code that can possibly be executed is already known at build time. Such a closed environment allows to make simplifying assumptions that enable various optimizations. The internal implementation of the kernel can be changed rather freely provided the kernel's interface and behavior remain constant.

The root cause of the portability problem is the diversity of target configurations. A target configuration traditionally includes one or more external aspects such as the processor architecture, the hardware platform, and the operating system (OS) or run-time environment. A target configuration may also include internal aspects such as different selections of program features or alternative algorithms. Each configuration requires specific handling of its particular features, which is implemented in configuration-specific code. Naively, every new configuration could be implemented in a completely separate code base. However, target configurations naturally have more in common than what they differ in so

#### 1 Introduction

that configuration-specific code often amounts to only a small fraction of the active code. Large amounts of code can be reused across configurations.

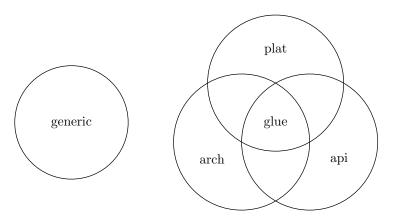

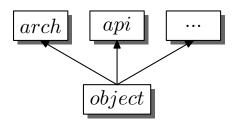

Modularity is the key to reuse and configurability and thus to portability. Code is either specific to one configuration, can be used for a set of configurations, or is generic and can be used for all configurations. Each of these groups contributes a set of modules of which selected modules can be combined accordingly to produce the code base for a particular target configuration. There are three hardnesses of modularity: identifying dependencies of code on configurations so as to minimize code duplication and maximize reuse; finding the right interface for modules such that they can be combined in any required way; and combining modules in an efficient way to achieve acceptable run-time performance.

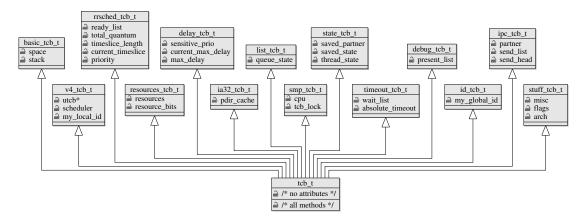

Object-oriented programming strongly encourages modularity [10] by encapsulating data and functionality in classes with well-defined interfaces. Inheritance allows to compose classes from one or more other classes. New methods and data members can be added and methods and data members inherited from a base class can be overridden, enabling fine-granular combination and stepwise refinement of functionality. In earlier work I showed how inheritance can be used to compose classes for kernel objects from configuration-specific classes to manage the configuration diversity in a portable microkernel written in C++ [15].

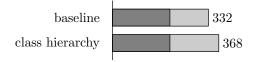

Efficient cache usage is of paramount importance to microkernel performance. Besides generating compact and well-scheduled code, frequently accessed data structures must be optimized for minimum cache footprint on the critical path. However, the optimal layout of those data structures heavily depends on many factors such as the processor architecture [35, 40], the particular choice of algorithms in the kernel, and the workload running on top of the kernel. There is no one-fits-all layout. Consequently, performance-critical data structures are often optimized manually for a particular, expected to be common configuration by rearranging the order in which their data members appear in the structure definition. Other configurations either suffer performance losses from suboptimal layout or are considered important enough to justify their own manual layout optimization. The latter then results in multiple configuration-specific definitions of the same data structure in the code base, which reduces the maintainability of the code.

Inheritance addresses many problems with regard to code duplication and code selection. However, the language implementation of inheritance often imposes considerable run-time overhead — mostly in support of dynamic polymorphism — which stems from two sources: inefficient method invocation and suboptimal object layout. Firstly, the implementation of virtual function invocations often uses indirect calls. Such calls are problematic because their target depends on the actual object that the function is invoked on, creating a hard to predict data dependency in the control flow. This overhead can amount to as much as 40 percent in applications [33] and more than 120 percent in a microkernel [15]. Secondly, the object memory layout of classes using inheritance is primarily governed by the inheritance relationship [25], i.e., members of base classes form subobjects in a derived object. Furthermore, meta-data may be added to the object to help finding subobjects and virtual functions. Thus the programmer has only limited control over the resulting objects' memory layout and cannot achieve optimal cache usage by designing the kernel objects

properly. Suboptimal data structure layout of kernel objects can result in overheads of 11 percent or more in a microkernel. In this thesis I devise a methodology to eliminate the overheads of inheritance inside a microkernel.

Support for dynamic polymorphism is not necessary when inheritance is solely used as a tool to efficiently compose classes, an approach that perfectly lends itself to managing modularity: A class for a kernel object inherits from a number of small, configuration-specific classes the selection of which is determined for each particular configuration by the kernel configuration framework. By convention, only the most-derived class is instantiated and its objects are never treated as base-class objects. Then the exact type of all that class' objects is known at compile time and various optimizations can be applied.

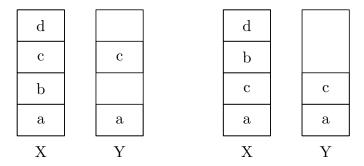

Class flattening [37] creates a representation of a derived class that directly contains all inherited members. Transparent class flattening is a variant of class flattening that translates the class hierarchy of a derived class into a simple, flat class without visibly changing the class' interface. The definition of the original class is thereby replaced with the definition of the flattened class. Code using a transparently flattened class does not need to be adapted to accommodate for flattening. A compiler will generate code for invoking methods using direct instead of indirect calls and will also not generate any inheritance-related meta-data. I identify the properties of a class hierarchy that make it suitable for transparent class flattening and describe an approach to safely automate the transparent flattening process as a source-to-source transformation in a microkernel environment.

Field reordering [60] changes the placement of fields inside an object to optimize the memory layout of the object according to certain criteria such as cache usage. This reordering can take place at various locations: at runtime, through an indirection mechanism; in the compiler or runtime system of a type-safe language; or before compilation. Applied after class flattening, field reordering can eliminate the overhead of inheritance that relates to suboptimal object memory layout caused by encapsulation of subclass objects. For performance reasons and based on the assumption that kernel usage in a microkernel-based system will not drastically change during execution, only a static reordering at build time is feasible. In this thesis I devise a profiling-based approach to automatically optimize the internal layout of performance-critical data structures in a microkernel.

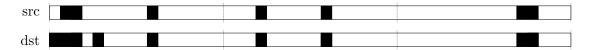

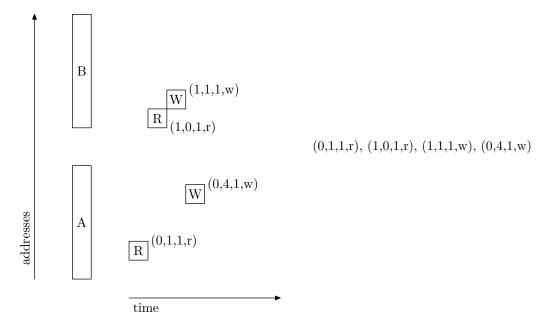

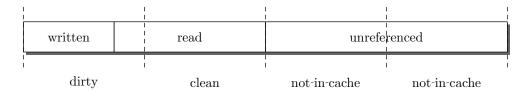

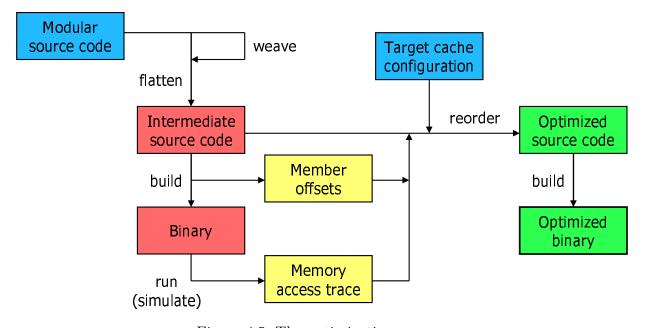

The optimal layout of kernel objects is derived from access patterns observed while the kernel is executing the envisaged workload. Profiling in an extensible full-system simulator is the least intrusive and most precise method compared to instrumentation and in-target statistical profiling. A profiling extension in the simulator collects information about memory references to data members of performance-critical kernel data structures and provides input to a layout optimizer that produces an optimal ordering of the data members in the data structure definition. To minimize the overhead of profiling, the extension exploits characteristics of microkernels such as execution in privileged mode, extremely short and similar paths through the kernel, and a small number of performance-critical objects being involved in every kernel operation. The optimal ordering is applied automatically and transparently in a source-to-source transformation.

First flattening performance-critical classes and then reordering their members eliminates the run-time overheads of inheritance, so that inheritance can be used to improve the

#### 1 Introduction

structure of the code base with no negative effect on performance. Both flattening and reordering can be automated and integrated into the kernel build process as transparent optimization steps. Whereas manual layout optimizations of kernel data structures target exactly one configuration and require both time and strong specific kernel expertise, the proposed optimizations apply to any configuration and thus are immediately usable for all kernel programmers.

Prototypically applied to the L4Ka::Pistachio microkernel, the combination of class flattening and field reordering completely eliminates the run-time overhead of inheritance. Performance of a kernel with a performance-critical class implemented as a class hierarchy, flattened, and reordered, matches that of the original kernel with a simple, hand-optimized class. In several configurations the automatic optimization even improves performance, because the hand-optimized class is not optimal for those configurations.

# Names and Notations

This thesis discusses optimizations of kernel data structures that are instances of compound data types. Throughout this document these compound data types will be referred to as *classes* and instances of them will be referred to as *objects*, following the naming as used in the C++ specification [25]. The terms *data member* and *field* are synonyms.

Throughout this thesis, the term x86 architecture refers to the common subset of the Intel 64 and AMD64 instruction set architectures implemented by processors of Intel and AMD, respectively.

In this thesis, the initialism TCB always refers to the Thread Control Block kernel data structure holding the state of a thread. In the literature this initialism also stands for the trusted computing base of a system. Should this thesis ever refer to the trusted computing base it will do so by using the unabbreviated name.

This work was applied to and evaluated in the L4Ka::Pistachio microkernel, a project of the System Architecture Research group at the University of Karlsruhe, Germany. Throughout this document, the names Pistachio, Pistachio kernel, and Pistachio microkernel shall all refer to said microkernel.

# **Organization**

This thesis is structured as follows: In Chapter 2, I provide background information that helps understanding the remainder of the thesis. Section 2.1 discusses caches and strategies for reducing cache misses and cache miss latencies. Section 2.2 illustrates how an inmemory object representation relates to its type specification, especially in the presence of inheritance. In Section 2.3, I introduce program transformations, in particular class flattening and data member reordering. I also discuss related work in these two areas. Section 2.4 presents portability considerations for kernel code.

Chapter 3 introduces the Pistachio microkernel and its portable application programming interface (Section 3.1) and describes how it addresses portability at the source code level (Section 3.2.) I propose inheritance as a solution to structural problems in Section 3.3 and provide experimentally determined estimates of how severely the introduction of inheritance will reduce the performance of the kernel in Section 3.4.

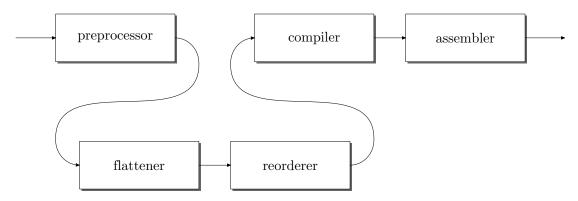

In Chapter 4, I detail my approach to eliminating the overheads of portability. Section 4.2 describes transparent class flattening to enable data member reordering for complex class hierarchies. Section 4.3 discusses novel strategies for data member reordering that are motivated by observations on object usage in a microkernel. In Section 4.4, I present a profiling approach to determine data member access patterns that is aggressively optimized to leverage microkernel specifics. I give an example of a data member reordering algorithm in Section 4.5. Section 4.6 illustrates how transparent class flattening and field reordering can be seamlessly integrated into the kernel build process.

I evaluate my approach in Chapter 5. Section 5.1 describes the evaluation environment, including hardware and software tools. In Section 5.2, I show by means of a cache analysis and several microbenchmarks that the proposed optimization technique can completely eliminate the overheads of inheritance and beyond that can optimize object layouts for a particular configuration and workload. Section 5.3 provides an insight into the costs of the optimization, and Section 5.4 compares automated optimization to a manual approach.

Finally, Chapter 6 concludes my thesis with a summary of its contributions and gives directions for future work.

# 1 Introduction

# 2 Background and Related Work

This chapter provides background information for the remainder of the thesis and discusses related work in the following areas:

- I optimize the cache footprint and thus execution performance of operations on data structures. In Section 2.1, I describe cache architectures, cache misses, and strategies for reducing or hiding cache latency.

- I optimize the memory layout of data structures by changing their definition. In Section 2.2, I describe how a structure's memory layout relates to its definition, and especially in the presence of inheritance.

- I employ and specialize the program transformations class flattening and field reordering. I describe program transformations in general and both techniques in particular in Section 2.3 and discuss related work.

- I present a technique that can be used to improve portability of kernel code. In Section 2.4, I describe aspects that need to be considered when writing portable kernels.

# 2.1 Caches

A cache is a place for storing items for easier or faster access. To use an item, a *cache lookup* is performed first. If the item is found in the cache, the lookup resulted in a *cache hit*, and the item from the cache can be used. Otherwise, a *cache miss* is said to have occurred and the item is to be found somewhere else.

The uses for caches are manifold. Buffer caches in an operating system store recently accessed disk blocks; web caches store documents recently retrieved from the network; DNS caches store network addresses of recently resolved host names. Processors are often equipped with memory caches to store frequently used information such as data or instructions for fast access.

Caches exploit the *principle of locality*. Two types of locality can be observed in programs: *Temporal locality* means that an item used recently is likely to be used again soon. *Spatial locality* means that items placed near each other are likely to be used close together in time.

Over the decades, the performance of processors has improved much faster than the performance of memory. In recent years, this disparity worsened by approximately 42

percent every year [20]. Ideally, one would desire huge memories accessible at the full speed of the processor. However, hardware needs to be small to be fast, and fast hardware also tends to be expensive.

Caches are small but fast memories. Building on the principle of locality, they allow to maintain the illusion of huge, fast memories. They hold only a tiny subset of main memory's contents but make this subset accessible with a fraction of main memory's latency. Until the 1980s, processors often did not have any caches, whereas today two levels of caches are a commodity, and a third level can be found in larger servers systems. The size of the caches increases with their distance from the processor, but so does also the time to access them. Die photos of today's general purpose processors show that caches consume approximately 50 percent of die real estate.

## 2.1.1 Cache Architectures

A cache holds copies of portions of main memory's contents for fast access. The unit of data that is transferred between the cache and memory (or the next cache level) is called a *cache block*. The optimum size of a cache block has been found to be 32 or 64 bytes, depending on cache size. Memory can be thought of as an array of cache blocks or memory blocks.

The locations in the cache where a cache block can be stored are called *cache lines*. The process of loading a cache block into a cache line is called a *line fetch*; the process of removing a block is called *eviction* or *flushing*.

Associated with each cache line is the block's address in memory, called the tag, and various status bits. A typical status bit is the *valid bit* indicating whether the cache line is currently holding a cache block. A cache is organized as a number of sets of a fixed number of cache lines. The cache lines in a set are also called *ways*, and their number defines the cache's *associativity*. A cache with n cache lines in n/m sets of m cache lines per set is called an m-way set-associative cache. The two special cases m = n and m = 1 are referred to as a fully-associative and direct-mapped caches, respectively.

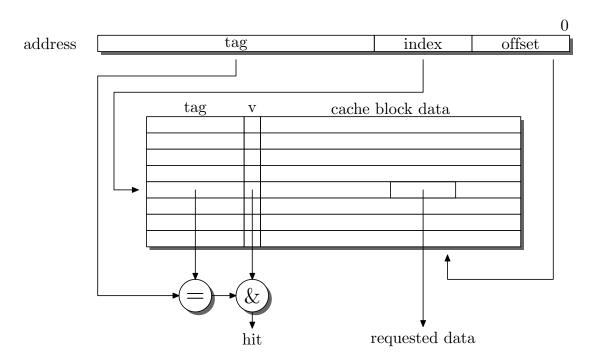

Figure 2.1 illustrates the process of a cache lookup. The address of the data requested is used as input for the cache lookup process. The index bits of the address select a set. The tag bits of the address are compared in parallel with the tag bits of each line in the selected set if that line's valid bit is set. If a match is found, the offset bits of the address locate the requested data within the matching cache line. Due to the use of parts of the address for selecting a set, the mapping of memory locations to cache sets is known. Neighboring memory blocks map to different cache sets unless the cache is fully-associative.

Depending on where the cache is positioned relative to the address translation hardware, the addresses used for indexing and tag comparison can be virtual or physical addresses. Virtually addressed caches remove address translation from the critical path of a cache lookup. However, they need to be flushed when address translations change, for example during an address space switch. Physically addressed caches avoid this at the expense of a generally higher access time. Virtually-indexed physically-tagged caches determine the

Figure 2.1: Cache lookup in a direct-mapped cache.

cache set using bits of the virtual address but then match the physical address against the tags, allowing indexing and address translation to proceed in parallel.

Except for direct-mapped caches where the decision is trivial, the replacement policy of a cache determines the line in a set a new cache block should be fetched into and thus replace that line's old contents. Ideally, the line that is least likely to be used in the near future, i.e., whose next use is the farthest into the future, should be replaced. However, such a prediction is usually impossible to make. Common policies that are nevertheless reasonably effective are *Round Robin* or *First-In First-Out*, (*Pseudo-)Least-Recently-Used*, or (*Pseudo-)Random*.

In a write-through cache, a cache hit on a write updates both the cache and memory. In a write-back cache, the same access updates only the cache; cache and memory become inconsistent, and the cache line is marked dirty by setting the respective status bit. The contents of a dirty cache line that is about to be replaced must be written back to memory before a new cache block can be loaded into the cache line. Replacement of dirty lines is therefore more expensive than replacement of clean lines which can simply be discarded.

A miss on a write in a *write-allocate* cache causes the respective cache block to be fetched into the cache. In a *no-write-allocate* cache, a write miss goes to memory and does not affect the cache. Write-back caches usually perform write-allocation in the hope for future accesses to hit in the cache. Write-through caches usually follow the no-write-allocate policy because future writes still need to update memory.

Multi-port caches can handle more than one request at a time, such as accepting a second request while the first request's data is being fetched from memory through a second port.

A cache may also serve requests in parallel through multiple request ports. To allow for such simultaneous accesses, caches may be organized in separately addressable banks with bits of the offset inside the cache line selecting the bank. Bank conflicts may arise from requesting data in the same bank but in different indices and may prevent simultaneous accesses.

In systems with more than one entity accessing memory, such as multiple processors with private caches or active devices, coherence between caches must be maintained for system correctness. Clean cache lines held in one cache whose contents are requested by another entity for modification must be invalidated; dirty cache lines must be written back to memory (or transferred to the remote cache) before their content can be accessed remotely. If all entities share a common memory bus, coherence can be achieved by monitoring or snooping the other bus agents' accesses. Each agent checks its local cache for blocks being requested remotely. In contrast, directory-based coherence protocols maintain information about the caching location and status of a block in one place, the directory.

# 2.1.2 Reducing Cache Misses

Unfortunately, not all memory accesses always hit in the cache. Various approaches in hardware and software have been devised to reduce the rate of certain types of cache misses. Hill and Smith [21] categorized cache misses as follows:

**Compulsory misses** occur when data is not found in the cache because it is being referenced for the first time. This situation arises after starting a program or after a cache flush, for example due to an address space switch.

**Capacity misses** occur when data is not found in the cache and all cache lines already hold valid data, i.e. when the cache is full. This situation arises when the working set of the program is too large to fit completely in the cache. Capacity misses would not occur in a cache of infinite size.

**Conflict misses** occur when data is not found in the cache and all ways of the set in which the data should be found already hold data but other sets still have unused lines. Conflict misses would not occur in a fully-associative cache of the same size.

Compulsory misses can be reduced by increasing the cache block size. However, with larger cache blocks the time to fetch a block into the cache increases as well. Capacity misses can be reduced by increasing the cache size, thereby also increasing hit time and power consumption. Conflict misses can be reduced by increasing associativity, which again may result in higher hit time and power consumption.

Alternatively, cache miss rates may be reduced by changing the software to best utilize the cache. Calculations on arrays can often be rearranged without affecting program correctness. *Loop Interchange* exchanges inner and outer loops such that the inner loop operates on array elements within a cache block rather than striding through the array. Nested loops that work on both rows and columns of arrays can in some cases be broken

down into several smaller loops that operate on subsets of the elements; this technique is called *blocking* or *tiling* and can, like loop interchange, be performed by the compiler.

Cache-conscious data placement arranges non-array objects such as global variables, constants, and stacks globally to minimize cache misses. Cache-conscious allocators exploit domain knowledge to collocate and reallocate objects that are accessed together, for example the nodes in a tree. Structure splitting gathers the hot parts of objects and allocates the cold parts separately which are then referred to from their hot counterparts. Reordering functions within the program image can reduce conflict misses. Aligning functions and basic blocks with the beginning of cache blocks can reduce cache misses for sequential code by increasing utilization of a cache block.

# 2.1.3 Reducing Miss Latency

Cache misses are expensive. First, the next lower, slower level of the memory hierarchy must be informed of the access. Then it takes several bus transactions to fetch the block into the cache, because the data bus width is most often much smaller than a cache block. The parts of the cache block are transferred either in sequential order or according to some interleaving scheme. Several techniques reduce or hide the latency of a cache miss: On one hand, enhanced line fetch strategies reduce the time between the request of a datum and its availability to the processor. Prefetching, on the other hand, tries to hide the latency of the memory hierarchy by requesting data before they are accessed.

A straightforward implementation of a cache might stall the processor until the complete block has been fetched into the cache. The *Early Restart* strategy releases the processor as soon as the requested data has been fetched, even though parts of the cache block are still in transfer. A subsequent request to data in the same block will be stalled until the block has been fetched completely. *Streaming* applies Early Restart also to subsequent requests to the line being fetched. *Requested Word First* transfers the part of the cache block first that contains the requested word, thereby minimizing the latency for the requested word. *Nonblocking caches* support out-of-order execution cores by continuing to serve requests to other cache lines while handling a miss.

Hardware prefetching looks for regularities in the addresses of memory accesses in order to detect streams and requests cache blocks before the program accesses the data. Often, multiple independent streams can be tracked concurrently. With software prefetching, the compiler or developer inserts special prefetch instructions to request the data. In contrast to hardware prefetching, software prefetching can avoid prefetching beyond the end of a stream and the resulting unnecessary bus traffic. Software prefetching can also benefit irregular access patterns if the distance between the prefetch instruction and the actual access is large enough. Prefetching too early, however, can be counterproductive by replacing other data that are needed between fetch and use of the prefetched data.

# 2.2 Data Structure Layout

Computers store the information they process in data structures. A *data type* is the description of a data structure whereas an *object* is an instance of a data type. The description of a data type is called *type definition*.

Data types can be classified into elementary types and compound types. *Elementary types* describe the basic data types of the language such as characters, integer and floating point numbers. Objects of elementary type are stored in consecutive bits of storage such as in a register or in one or more bytes in memory.

Compound types are constructed from a finite number of components, each of which can be of elementary type or of compound type again. Examples for compound types are arrays and classes. A known or bound number of objects of the same type can be stored in an array. With the help of object references, objects can also be arranged in lists or trees, which are suitable for managing an unknown number of objects. A class type groups a set of objects of elementary or compound type and a set of associated functions.

Type-unsafe languages, such as C and C++, allow the programmer to reason about the internal structure of an object. This is one of the reasons why C is popular for system programming where externally defined data structures need to be manipulated. In contrast, type-safe languages generally hide the details of object representation from the programmer, leaving the object layout to the compiler or the run-time system. In some cases, however, extensions to type-safe languages allow the precise definition of compound types' object representations, for example in the Common Intermediate Language [17].

This section describes the in-memory representation of compound C++ objects of class type and illustrates how this representation is influenced by the various methods of type construction.

## 2.2.1 Classes

A class groups related variables and functions. The variables are called data members or fields; the functions are referred to as member functions or methods. Data members represent the attributes (or the state) of an object, whereas member functions define the behavior of an object. A class defines a has-a relation between the class and its data members. Each object of a class contains all nonstatic data members of the class. In contrast, static data members exist only once per class; they are shared between all instances.

The following extract from the C++ specification [25, clause 9.2, Class members, paragraph 12] defines how the internal memory layout of an object is derived from the structure of the class definition:

Nonstatic data members of a (non-union) class declared without an intervening access-specifier are allocated so that *later members have higher addresses* within a class object. The order of allocation of nonstatic data members separated by an access-specifier is unspecified (11.1). Implementation alignment requirements might cause two adjacent members not to be allocated immedi-

ately after each other; so might requirements for space for managing virtual functions (10.3) and virtual base classes (10.1).<sup>1</sup>

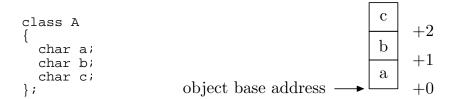

Access specifiers are the keywords private, protected, and public that define the accessibility of members from non-member functions of the class. Figure 2.2 shows an example of a simple class definition and the corresponding object memory layout.

Figure 2.2: A simple C++ class and its memory layout.

Alignment requirements of members may cause insertion of unnamed space, padding, in the object. Furthermore, the alignment requirement for objects of the class is derived from the maximum alignment requirement of all data members [25, clause 3.9, Types, paragraph 5].

Often, however, alignment requirements for members of a class can be overruled. With the GNU C++ compiler, for example, the attribute(packed) type attribute added to a class specification forces the compiler to assume the minimum alignment for all members: one byte for members, one bit for bitfield members. As a result, no padding larger than or equal to a byte will occur in objects of that class. The same can be achieved by placing #pragma pack(1) before the class definition. Packing can also be specified globally as a command line option-fpack-struct[=<n>]. The pragma specification is the most portable as it is consistently supported by most C and C++ compilers [19, 22, 24, 39].

Using the packing mechanism, a programmer has complete control over the object representation of a simple class type.

## 2.2.2 Inheritance

Inheritance allows to form new classes based on classes that have already been defined. The new, derived class (or subclass) inherits all data members and member functions from the base class (or superclass.) An object of the derived class is often referred to as a derived object.

A derived class can add new data members or methods, thereby enabling extension. It can also *override* inherited methods or *shadow* inherited data members to modify the behavior, thereby enabling specialization. Code reuse is enabled by inheriting methods from the base class that have identical implementations for derived and base classes instead of duplicating the implementation in the derived class.

<sup>&</sup>lt;sup>1</sup>Italic typeface not present in original.

### 2 Background and Related Work

Inheritance defines an *is-a* relation between a derived class and its base class. Since a derived class inherits all members from its base class, an object of a derived class (*actual type*) can serve as an object of a base class (*current type*), for example through an explicit type cast or by assignment to a base class pointer. This concept is called *polymorphism*.

Inheritance can be applied recursively, forming a class hierarchy. The class that a derived class inherits from, i.e. that is listed as a base class in the derived class' specification, is referred to as a direct base class. Base classes of direct base classes are indirect base classes. A class can serve as a direct base class for zero or more derived classes. Likewise, a derived class can inherit from one or more direct base class. A mixin is a class that cannot stand by itself but provides functionality to be inherited by a derived class. The effects of different types of inheritance on object layout are discussed below.

# Simple Inheritance

Inheriting from a base class places an object of the base class as a compact subobject into the derived object. The layout of the base class subobject is most often identical to that of an object of the base class, although the C++ specification does not mandate this. By placing the subobject at the start of the derived object and any additional data members declared in the derived class behind it, a derived object can be treated as an object of its base class at the same address. For example, a pointer to the derived object can be assigned to a pointer to a base class object without any address calculation required.

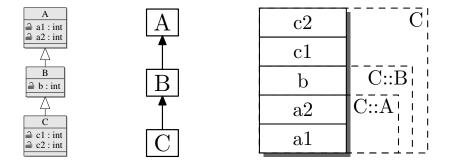

Figure 2.3: A simple C++ class hierarchy, the object lattice, and the memory layout of a most derived object. Inherited members form compact base class subobjects within the derived object. Members added in a derived class follow.

Figure 2.3 shows an example of a class hierarchy and the memory layout of the most derived object. Placement of data members in a derived object is first governed by the inheritance chain, then by the order in which added members are declared.

## **Polymorphic Functions**

A derived object can be treated as an object of a base class; a derived class can override functions defined by a base class. If a method is invoked on such a derived object while

it is being treated as a base class object, the version of the method defined by the base class will be called. In contrast, polymorphic functions, also known as *virtual functions*, allow to invoke the implementation defined in the derived class. The keyword **virtual** in a method declaration is used to explicitly request this behavior. For a virtual function, the version of the method that should be called depends on the actual type of the object. Therefore, the object needs to carry some sort of type identifier with it.

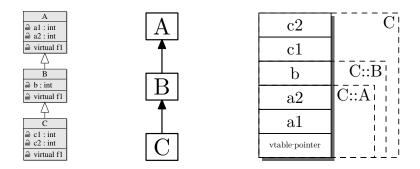

The address of a virtual function must be found dynamically at execution time. This process is referred to as *late binding*. A common implementation of late binding uses a virtual function table, the *vtable*. Such a vtable contains the entry points of all virtual functions of a class. Since the entry points are the same for all objects of a derived class, the vtable can be shared among all objects of a class. The vtable is referenced from each object via a *vtable pointer* which effectively acts as the type identifier of the object.

The vtable pointer is a hidden data member in the object; it is neither declared as a member nor can it be addressed from within the language. It is usually placed at the start of the object, but sometimes also at the end (for example, in Cfront [55].) A derived object and its base class object can share the vtable pointer, because their vtables contain pointers to the very same function implementations. Virtual functions introduced in the derived class are appended to the vtable. Those functions will never be invoked from the base class as it is not aware of the derived class.

Figure 2.4: Object memory layout of a class with virtual functions.

Figure 2.4 shows an object layout of a class with virtual functions. Compared to an object of an otherwise identical class with no virtual functions, the object size increases. Also, depending on where the implementation stores the vtable pointer within the object, data members may be located at different offsets.

Given an object's address, invoking a virtual function on this object then involves the following three steps:

- 1. Read the vtable pointer from the object;

- 2. Read the address of the function from the vtable at the virtual function's index;

- 3. Call the function<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>Depending on the architecture this step and the previous step could be combined in one instruction.

### 2 Background and Related Work

Two indirections via memory are necessary to reach a virtual function, whereby the first indirection is dependent on the object address. The dynamic selection of the actual implementation also makes virtual functions unsuitable for inlining. Research has been performed to improve the performance of virtual function invocations. Several approaches favor replacing the dynamic function call with a switch statement and a number of static calls [2, 11, 29].

# Multiple Inheritance

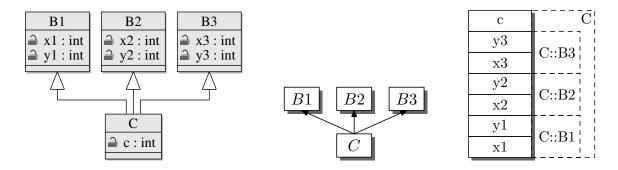

Multiple inheritance refers to a situation where a derived class has more than one direct base class. Subobjects of all direct base classes are placed in the derived object. The placement of those subobjects is not defined by the C++ standard. However, most compilers place base class subobjects in the order in which the base classes are listed in the derived class' specification. Figure 2.5 shows a class hierarchy with multiple inheritance and a possible object layout.

Figure 2.5: A C++ class hierarchy with multiple inheritance and the resulting memory layout of an object of the most derived class C.

In addition to the most derived object's vtable pointer, each base class object may have its own vtable pointer, too (not shown in Figure 2.5). The derived class can, however, share its vtable pointer with one of the base classes. Especially for small objects with many base classes the storage overhead for vtable pointers may be significant.

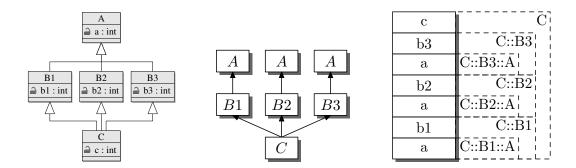

## Multiple Inheritance with Common Base Classes

A class can be a direct base class of a derived class only once. However, it can be an indirect base class more than once. In such a scenario, multiple subobjects of the base class exist in the derived object, as is shown in Figure 2.6.

Each of those subobjects can be manipulated independently. Naming ambiguities, which arise when addressing members inherited from the common base class, must be resolved using the scope resolution operator :: to identify the intermediate base class whose subobject is meant.

Figure 2.6: A C++ class hierarchy with multiple inheritance and a common base class and the resulting memory layout of an object of the most derived class C.

# Multiple Inheritance with Virtual Base Classes

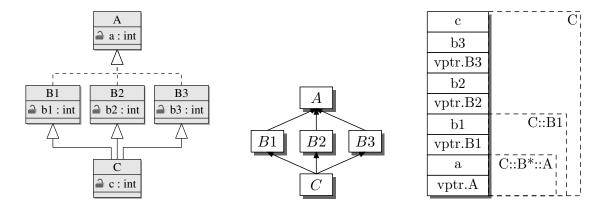

A class becomes a *virtual base class* when it is prefixed with the keyword **virtual** in a derived class' inheritance specification. Being a virtual base class is not an attribute of the base class; it is determined by how the class is inherited. Subobjects of virtual base classes exist only once in the derived object and are shared between all derived classes that inherit them. Figure 2.7 shows an example of virtual base classes.

Figure 2.7: A C++ class hierarchy with virtual inheritance and the resulting memory layout of an object of the most derived class C. Subobject A is shared among objects of all classes that virtually inherit from A, directly or indirectly.

Subobject A is shared between the objects of B1, B2, and B3. Only one instance of A exists in C. C's subobjects B1, B2, and B3 each contain a pointer to a vtable. The subobjects of B2 and B3 span noncontiguous memory locations. A is part of B2, yet neither b1 nor B1's vtable pointer belong to C::B2; likewise for B3. Besides pointers to virtual functions the vtables contain the displacement of subobject A relative to the containing object (B1, B2, or B3). A reference from B2 (or B1 or B3) to A::a thus requires an indirection and an address calculation.

### 2 Background and Related Work

To complicate matters, a class can be a virtual base class and a nonvirtual base class at the same time, so that shared and unshared base class subobjects exist.

# Summary

For simple classes, data members appear in the object in the same order as they appear in the class specification. Data members of derived objects, however, are first placed according to inheritance relationships and then by order of appearance. Furthermore, metadata may be included in the object. Consequently, the placement of members in objects of complex class hierarchies can not be influenced by the programmer as freely as in a simple class.

# 2.3 Program Transformations

Program transformation is the process of transforming one program into another. Two variants of program transformation can be distinguished: *rephrasing* transforms the program within the language whereas *translation* changes the language of the program. Compilation translates a program given in a high-level language into machine code so that the program can be directly executed by a processor. Rephrasing aims to improve a certain aspect of a program while maintaining its behavior.

This section describes the build process for C++ programs and the two program transformations class flattening and field reordering. It also discusses related work in the area of those transformations.

## 2.3.1 Build Process

For more than 25 years, the approach to turning OS source code into an executable has not changed much. C has been and still is the predominant programming language in all major desktop and server operating system kernels today [9, 36, 52, 53].

The build process for operating system kernels written in C or C++ does not differ much from the process of building applications in those languages. The most notable difference is that operating system kernels are highly self-contained whereas applications often rely on functionality provided in libraries.

Many programming languages support separate compilation. Source code modules or units, often stored in a separate file, are translated one-by-one into object files. All object files are then combined to the final program. Separate compilation can significantly reduce the build time of large programs by compiling only the modules that were modified or whose dependencies were modified.

The common build process for C and C++ programs (and OS kernels) consists of the following four stages:

**preprocess** Starting with the source file that is to be translated, the preprocessor replaces #include directives with the contents of the file they refer to. This process is recursive. The result is a single, linear representation of (at least) all the code that is

necessary to perform the translation, such as data types, base classes, and declarations of functions or variables implemented in other source files that are referred to from the source current file. **#include** directives allow to share common code among multiple source files.

In a second step, macros are expanded. Macros can also take parameters that are substituted during expansion. Furthermore, the presence or value of macros can be tested using the #if directive. Depending on the expression used, all text between an #if directive and its corresponding #endif directive are included or removed, allowing for conditional compilation.

compile The compilation stage transforms source code from the high-level language to assembly language. This stage itself consists of several steps. A front end for the high-level language performs lexical, syntactical, and semantical analysis of the input and generates an intermediate representation of the program. A middle end performs further analysis (e.g., dependence analysis, alias analysis, pointer analysis) and optimizations (e.g., inline expansion, dead code elimination, constant propagation, loop transformation, register allocation.) Finally, a back end for the target emits assembly code for the optimized intermediate representation, involving instruction scheduling, selection of addressing modes, register and memory allocation, etc.

assemble The assembler translates assembly code into blocks of binary instructions, blocks of data, and address information, the symbol table. Symbolic local jump targets turn into offsets of jump instructions; function entry points and global data appear as public symbols; references to nonlocal memory objects or jump targets are marked as external symbols requiring relocation. The output of the assembler is an object file.

link During the link phase, all object files are combined into the final binary. External symbols of one object file are matched with public symbols of other object files. Code and data of all object files are merged into common sections. Object-file relative addresses are assigned addresses relative to the final binary, and addresses for external symbols are filled in. External symbols that cannot be found in the object files of the program are looked up in libraries for linking at program load time. The complete program is emitted as a final binary file that can then be loaded by the operating system for execution.

# 2.3.2 Class Flattening

Class flattening is a rephrasing program transformation. From a derived class in a class hierarchy (the *source class*), it creates a simple class (the *target class*), which does not use inheritance. The flattened target class directly contains all direct and inherited members of the source class and has no base classes itself, as illustrated in Figure 2.8.

Class flattening includes all direct and inherited members of the source class into the target class. This can be achieved by walking the inheritance graph, beginning at the

```

class A {

public:

int a;

void f() { /* A::f */ };

void g() { /* A::g */ };

class FlatB {

};

public:

class B : A {

int a;

public:

int b;

int b;

void f()

/* A::f */

void g() { /* B::g */ };

void h() { /* B::h */ };

/* B::g */ };

/* B::h */ };

void g()

};

};

(b) Class B flattened into FlatB

(a) Class hierarchy for B

```

Figure 2.8: Class flattening creates a stand-alone class without base classes from a derived class' hierarchy. All members accessible in the derived class appear in the flattened class.

source class, in a breadth-first manner. All members that do not yet exist in the target class are copied there whereby the language's rules for hiding and overriding of inherited members define whether a member already exists.

The *flat form* of a class was introduced by Meyer [37]. Meyer sees two uses for the flat form: inspection of the full feature set of a class by a developer, and distribution of a class without its history. A first brief description of the flattening process was given by Meyer in 1997 [38] whereas a command line utility to create a flat form of Eiffel classes was already available in 1998 [37].

Independent of Meyer, Bellur et al. describe a class flattening tool for C++ [5]. The flattener manipulates preprocessed source code. The authors target class flattening as a means to eliminating virtual functions for which they describe two alternative approaches: In the stand-alone approach, the flattener copies all relevant member functions and data members from a selected class K and its base classes into a new class FlatK and removes the inheritance relationship. In the parallel hierarchy approach, a separate class hierarchy with Flat-prefixed class names is created where all virtual functions are de-virtualized while the inheritance relationship is maintained. To use the flat version of a class, the programmer and/or the flattener can turn selected variables of type K or related types into the respective type for FlatK (variable flattening). The flattener can also create copies of client functions, i.e., functions that have at least one parameter of type K or related type (client function flattening). These functions with parameters of type FlatK instead of K overload the original client functions. They will be used whenever a client function is called with the flattened version of the class. An automated approach for variable flattening is suggested by the authors, but considered infeasible due to the high cost of a full data flow analysis. They report a 4.25-5.58 times faster execution for two example programs that are best cases for flattening: short, inlinable virtual functions; no use of dynamic polymorphism.

A second use of class flattening proposed by Bellur et al. [5] is *enhancing program understanding* by presenting a flat form of a class in a source code browser, like suggested by Meyer. Furthermore, the authors mention that class flattening can also ease debugging, because execution no longer jumps up and down in the class hierarchy.

Another use of class flattening can be found in the area of software quality measurement. A very detailed description of the class flattening process for C++ by Beyer et al. [6] has been implemented in the Crocodile measurement tool [34]. Beyer et al. also discuss the impact of inheritance on software metrics like size, coupling, and cohesion [7]. Comparing values for original and flattened versions of classes led the authors to an improved interpretation of values for the unflattened version. Furthermore, the additional data allowed to detect more candidates for restructuring, and gave insights into the use of inheritance, be it for source code sharing, definition of interfaces, or creation of type hierarchies.

Binder [8] applies class flattening to reduce complexity in the context of *software testing*. There, only a flattened class allows to define a reasonably sized class test plan for all features inherited.

All instances of class flattening in previous work create a second, flattened variant of the class definition, which coexists with the original. This work proposes *transparent class flattening* which *replaces* the original class definition with the flattened variant.

# 2.3.3 Field Reordering

Field reordering arranges fields of a compound data structure according to an optimization criterion. It is commonly used to improve the spatial locality of compound data structures to optimize cache usage when accessing them. Field reordering can be performed in the run-time system, in the compiler, or as a source-to-source transformation. The latter relies on a correlation between the order of fields in the type specification and the resulting object layout, such as described for C++ in Section 2.2.1.

In type-safe languages, field reordering is automatically safe because the object's inmemory representation is left to the compiler or run-time system. In other languages, for example in C or C++, the programmer can reason about the internal structure of an object and make static assumptions about the placement of fields. Arbitrarily reordering fields could therefore negatively impact program correctness.

Truong et al. [60] present field reordering as a technique to improve the cache behavior of dynamically allocated data structures in C. With field reordering, "fields of a data structure often referenced together are grouped together to fit into the same cache line." Truong et al. exploit the fact that nonstatic data members of a C data structure are assigned increasing addresses in the order they appear in the data structure declaration. This behavior is defined in the C language specification [26]. Consequently, changing the field order in the declaration influences their mapping to memory addresses and thus to cache lines. Truong et al. leave determining the optimal layout to the programmer, because "At present, the automatic detection of the most frequently used fields of a structure is beyond the possibility of current compiler technology." In combination with another

optimization technique, instance interleaving, Truong et al. obtain speedups of 1.08–2.53, reducing cache or TLB miss ratios by 35 to 96 percent.

# Semi-Automatic Field Reordering

Chilimbi et al. [14] automate field reordering for C programs in so far that a tool produces recommendations for new field orderings. These recommendations need to be checked and eventually implemented by the programmer, because the authors deem automatically determining whether layout manipulations are safe with respect to program correctness impossible. Profiling information from a previous program run is combined with static analysis in order to, in the end, construct a field affinity graph for every structure type. In these graphs, nodes represent fields and edge weights are proportional to the frequency of the fields being accessed contemporaneously, with contemporaneously meaning being accessed within a certain time (100ms). All instances of a type are treated identically, as most instances were found to show "similar access characteristics (i.e., consecutive accesses to the same field in different (indistinguishable) instances, rather than different fields)." Chilimbi's approach places fields with high temporal affinity near each other; no assumption is made about structure alignment on cache-line boundaries, as this "can only be determined at run time". Chilimbi et al. reports performance improvements of 2 to 3 percent after reordering five of the most frequently used data structures in Microsoft's SQL Server.

Kistler and Franz [28] call field reordering "data member clustering". A second technique, referred to as "data member reordering" attempts to optimize the order of fields within a cache line. Memory interleaving and cache line-fill buffer forwarding are identified as source of different latencies for the words in a cache line after a cache miss. Like Chilimbi et al., Kistler and Franz build temporal relationship graphs (TRGs) for objects. Nodes in the graph correspond to fields in the object. The weights of the edges reflect the number of times fields were accessed subsequently within a specific number of disjunct memory references. "The TRG is created by collecting path profiling information and then stepping through each program path returned by the profiler." These graphs are then subjected to a graph partitioning algorithm that associates fields with cache lines. It is, however, left unclear how multiple potentially different TRGs for objects of the same class lead to an optimized layout for the class. "Finding an optimal order of fields within cache lines is done with an exhaustive search..." By limiting the application to type-safe programming languages such as Oberon, the optimization process can be fully automated. Kistler and Franz also discuss optimizing the layout of derived objects. Subobjects inherited from supertypes are considered inseparable. Layout optimizations are thus restricted to how fields introduced in the derived object are placed behind the inherited subobject. The likely but unstated reason for this limitation is polymorphism. The paper also states that, "Encapsulation of object types often leads to subtypes having only minimal access to their inherited fields, thereby reducing temporal relations between fields from different derivation levels." However, access patterns to fields of a data structure are actually not related to accessibility of inherited fields from derived types. Kistler and Franz report speedups of 3 to 96 percent for their layout optimization. How much of this speedup can be attributed to "data member reordering" (inside a cache line) on top of "data member clustering" (of fields into cache lines) is not described.

Zatloukal et al. [65] present a slightly different algorithm for finding an optimized field ordering. A program's access behavior is modeled in a per-structure member transition graph (MTG). The nodes in the graph represent the members. The edges between any members i and j carry transition and survival probabilities. The transition probability describes how likely member i is accessed immediately before member j. The survival probability describes how likely a cache line that was in the cache when member i was accessed is still in the cache when member j is accessed. The graph is built from data collected during the program's execution. Access to the compiler's type information allows gathering traces that include each memory address accessed, and for each access to a structure member, the name of the structure and its member. From the MTG, cache hit probabilities can be determined for any member ordering by a set of equations. The optimization algorithm uses a Branch-and-Bound algorithm [30] that considers all possible orderings for small structures, and a Local Search algorithm [1] that iteratively improves the initial ordering for larger structures. Finally, the ordering suggested by the optimization algorithm is subjected to a simulation step that reports cache miss rates for the reordered structures based on the initially collected trace. The result of the optimization is a new ordering for members that the programmer may choose to implement. Zatloukal et al. report a performance improvement of 1.3 percent after reordering seven data structures in Microsoft's SQL server. This is less than the results reported by Chilimbi et al. [14], because a limitation in the profiler did not allow to reorder any of the five most frequently used structures that were optimized by Chilimbi.

None of previous work on field reordering in type-unsafe languages has completely automated the process of field reordering. At best, a new ordering is suggested, which then still needs to be verified and — if found safe — be performed manually by a programmer by modifying the structure definition. Furthermore, field reordering has been applied to C, but not to C++ and therefore not to C++ class hierarchies either.

#### Complexity

There has been considerable research into the complexity of field reordering. For complete access traces an algorithm can find the optimal layout in exponential time: it simply tries all possible placements. Thabit [58] showed that optimal data packing using pairwise frequency information is NP-hard and that the optimal packing also depends on the cache's replacement policy. Likewise, Kennedy and Kremer [27] showed that the problem is NP-hard. Petrank and Rawitz [44] showed that no polynomial time method can guarantee a data layout whose number of cache misses is within  $O(n^{1-\epsilon})$  of that of the optimal data layout, where n is the length of the trace. In addition, if only pair-wise information is used, no polynomial algorithm can guarantee a data layout whose number of cache misses is within O(k-3) of that of the optimal data layout, where k is the size of the cache. The results hold even when the computation sequence is completely known, objects have the

same size, and the cache is set associative. These general results, however, do not preclude effective optimization targeting specific (rather than all) data access patterns [66].

# 2.4 Kernel Portability Aspects

Porting is the process of bringing a software to an environment different to the one(s) it has been written for. Porting often requires modifications to the software in order to adapt to the new environment. Such modifications are either generalizations or (partial) reimplementations. Generalization replaces parts of the software that are incompatible with the new environment with a more generic variant whereas partial reimplementation adds variants that are compatible with the new environment. In contrast to rewriting a piece of software from scratch for every new environment, porting promises less effort through the reuse of parts that need not be adapted. Portability is a software metric expressing the ease of porting.

The challenge for portable software is configuration diversity. A configuration is characterized by numerous aspects. The most notable aspects are instruction set architecture, word width, and run-time environments. However, several more hardware properties as well as diversity of software and development tools add to the configuration space. This section discusses various aspects of the environment that a portable kernel needs to address.

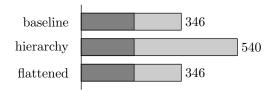

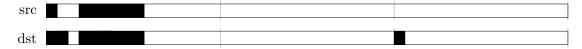

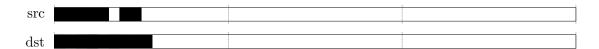

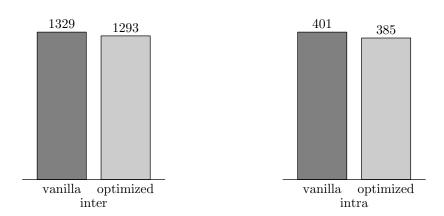

#### 2.4.1 Hardware