# µ-Kernel Construction (5)

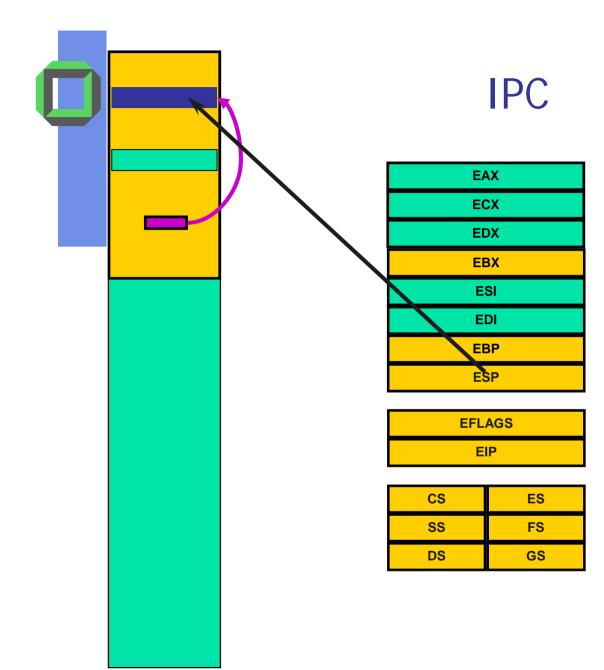

# **IPC Implementation**

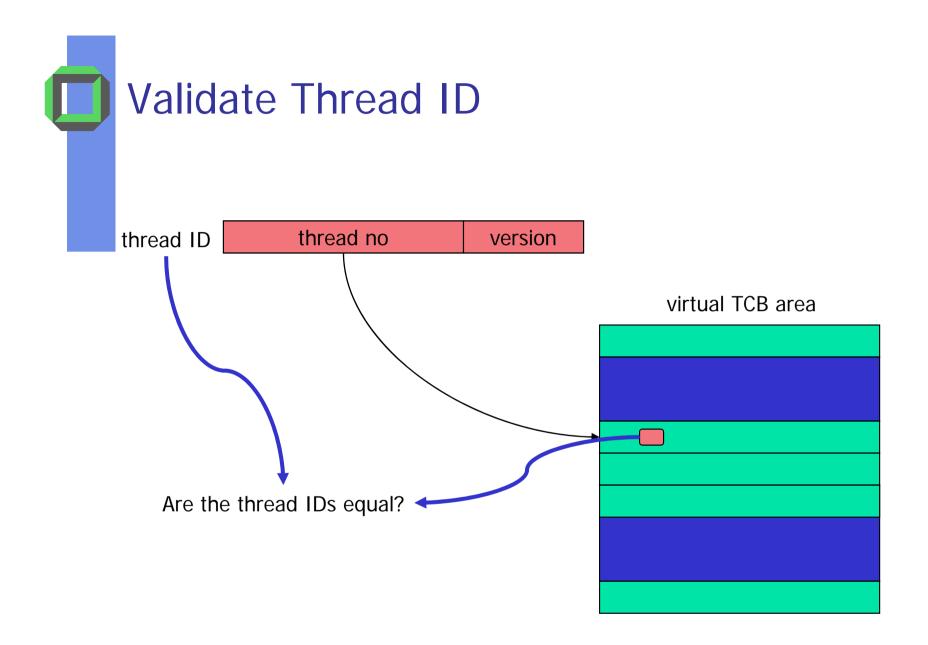

- Validate parameters

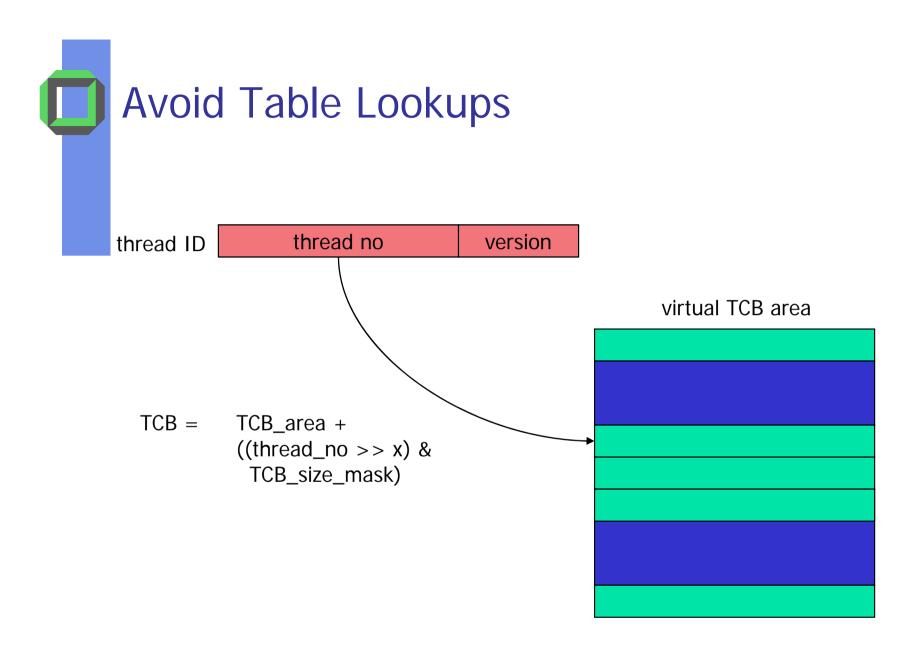

- Locate target thread

- Return error if unavailable

- Transfer message

- Untyped items (short IPC)

- Typed items (long IPC)

- Schedule target thread

- Switch address space as necessary

- Wait for IPC (reply/next request)

# **IPC Implementation**

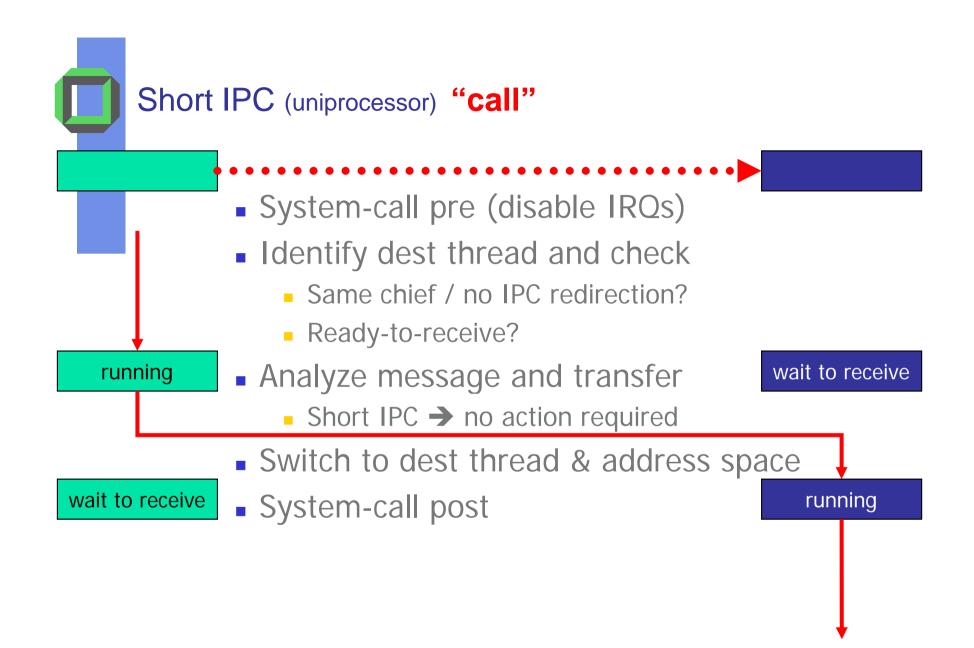

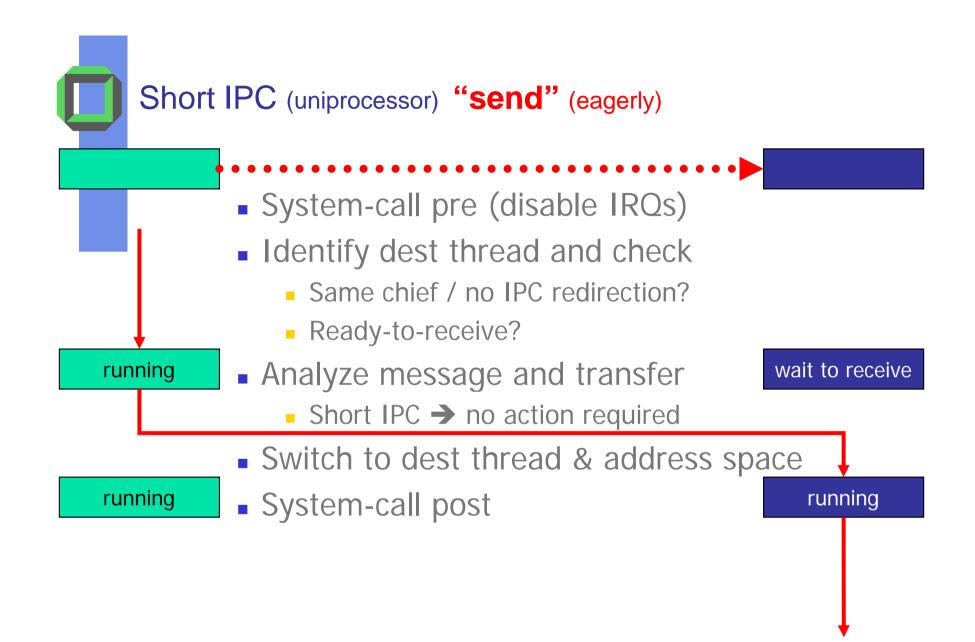

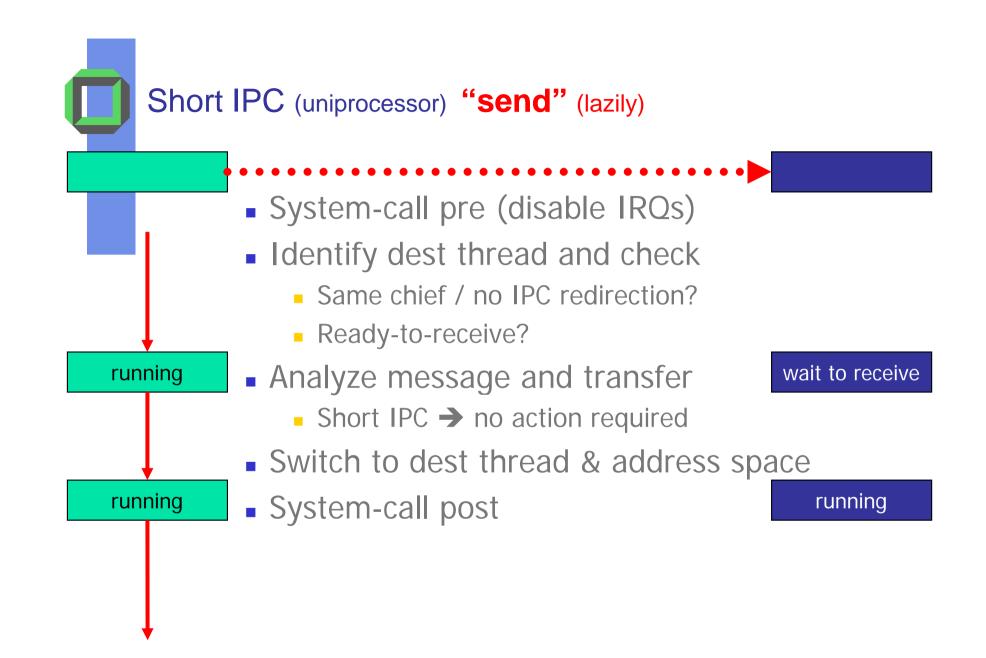

### Short IPC

- System-call pre (disable IRQs)

- Identify dest thread and check

- Same chief / no IPC redirection?

- Ready-to-receive?

- Analyze message and transfer

- Short IPC → no action required

- Switch to dest thread & address space

- System-call post

#### The critical path

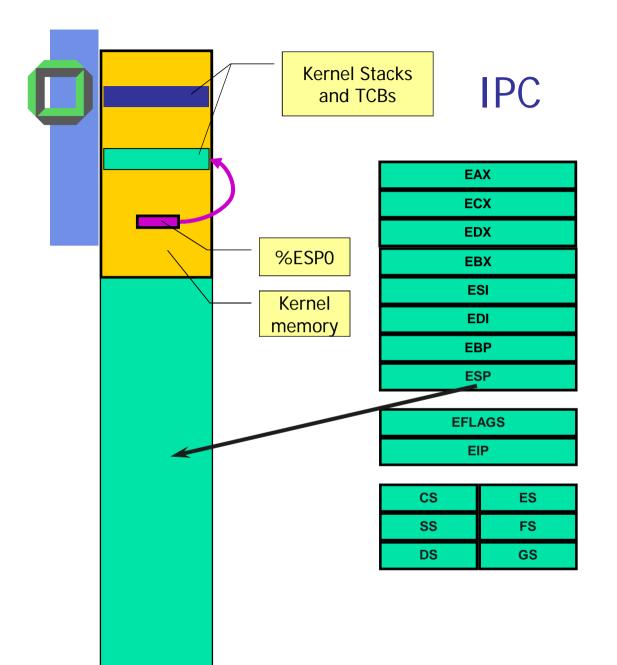

| EA<br>EC |     |  |

|----------|-----|--|

| EC       | ЭХ  |  |

| EE       | 3X  |  |

| E        | SI  |  |

| E        | DI  |  |

| EE       | BP  |  |

| EŚ       | P   |  |

| EFL      | AGS |  |

| E        | Р   |  |

| CS       | ES  |  |

| SS       | FS  |  |

| DS       | GS  |  |

|          |     |  |

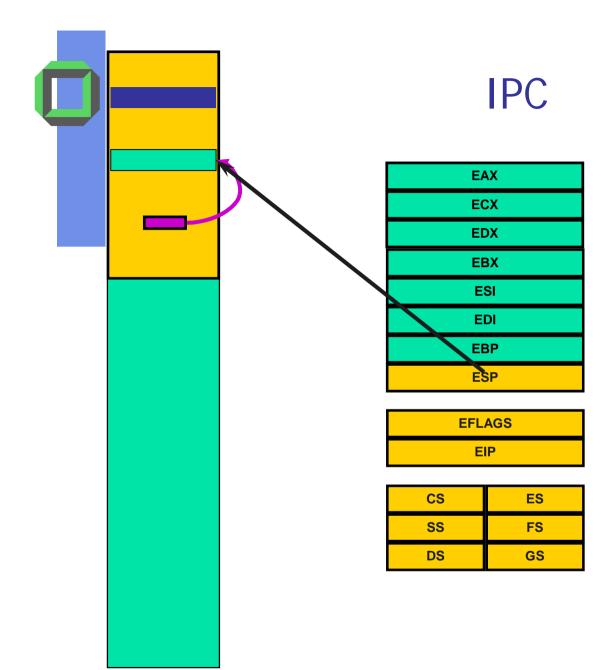

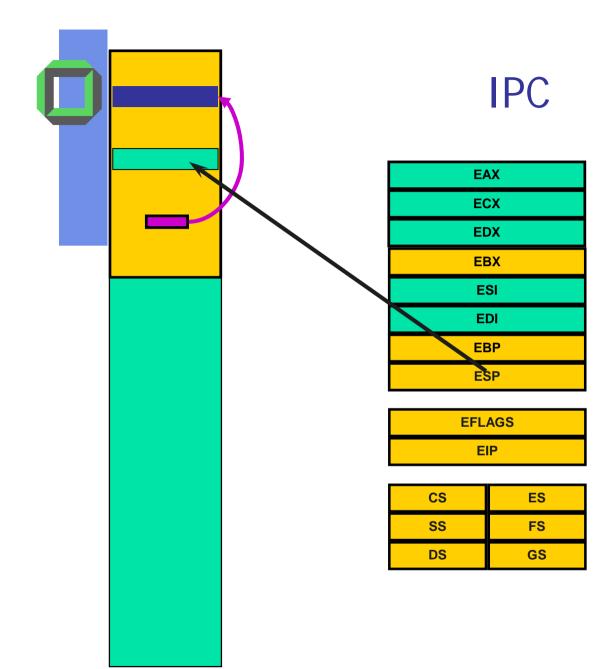

| EAX           |    |

|---------------|----|

| ECX           |    |

| EDX           |    |

| EBX           |    |

| ESI           |    |

| EDI           |    |

| EBP           |    |

| ESP           |    |

| EFLAGS<br>EIP |    |

| CS            | ES |

|               | FS |

| SS            |    |

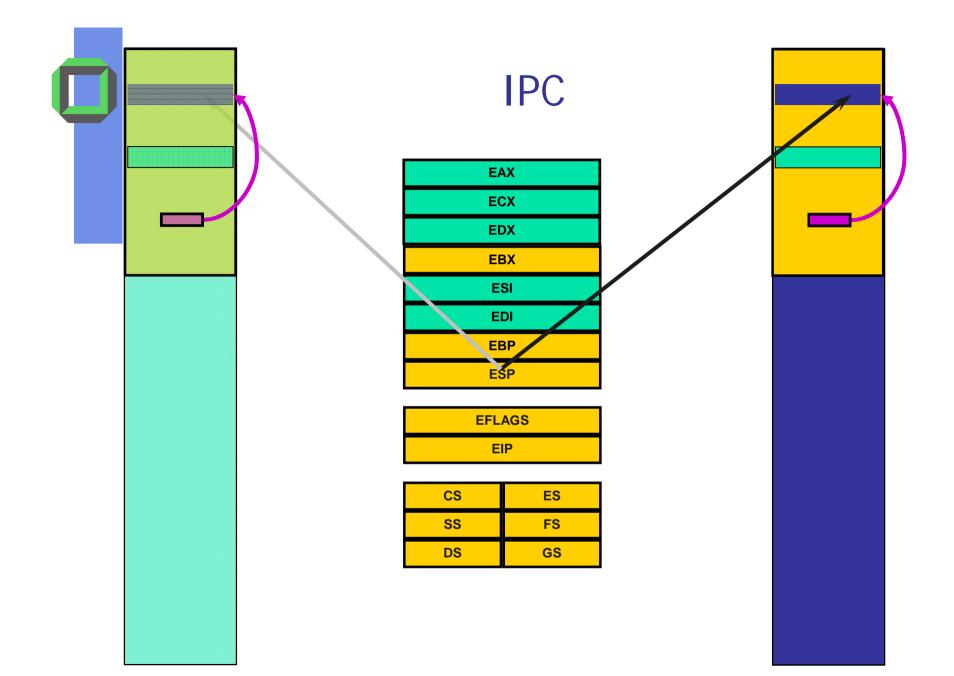

# IPC via sysenter/sysexit

- Real register use

- EAX: dest. TID ⇒ sender TID

- ECX: timeouts ⇒ user IP (sysexit)

- EDX: receive TID ⇒ user SP (sysexit)

- EBX: (scratch) ⇒ MR<sub>1</sub>

- EBP: (scratch) ⇒ MR<sub>2</sub>

- ESI: MR<sub>0</sub> [only unchanged register]

- EDI: UTCB(sender) ⇒ UTCB(receiver)

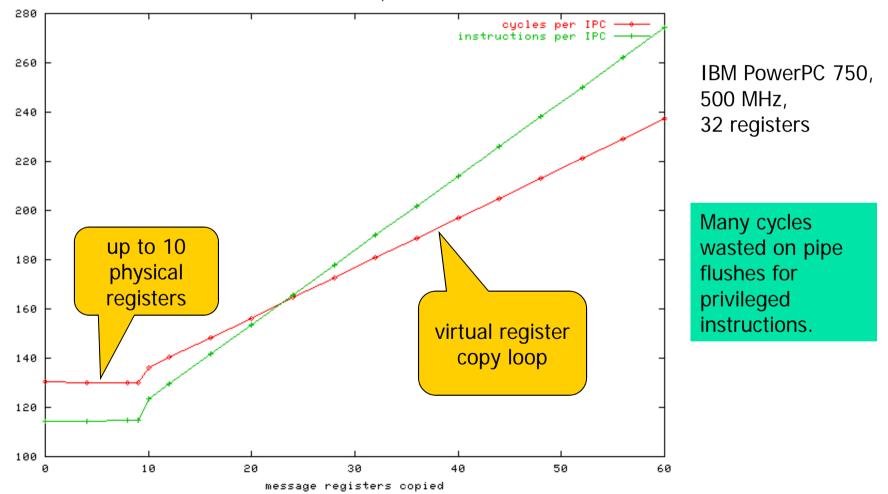

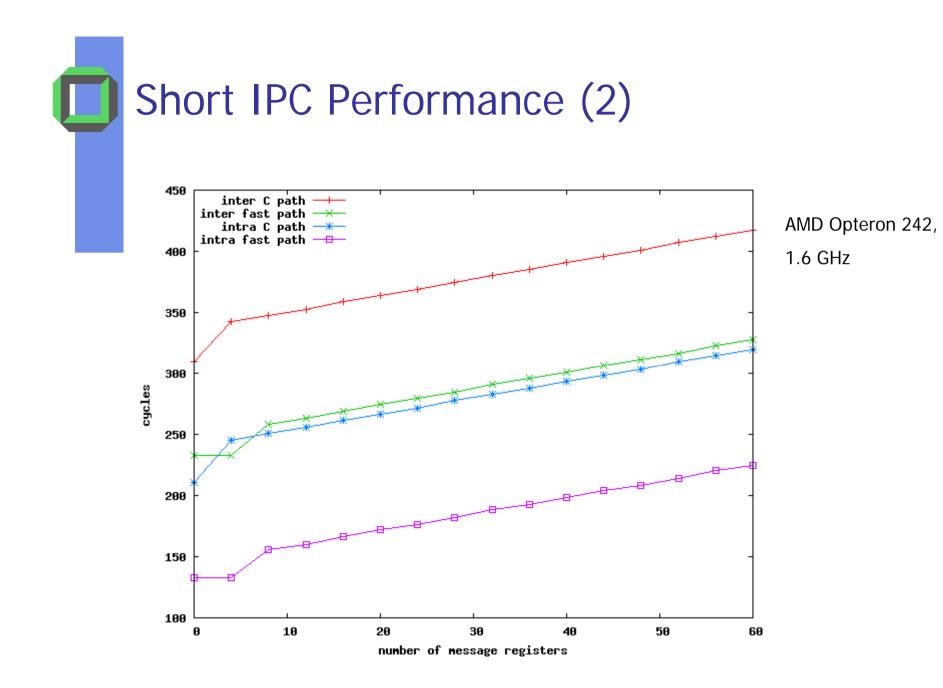

# **Implementation Goal**

- Most frequent kernel op: Short IPC

- Thousands of invocations per second

- Performance is critical

- Structure IPC for speed

- Structure entire kernel to support fast IPC

- What affects performance?

- Cache line misses

- TLB misses

- Memory references

- Pipe stalls and flushes

- Instruction scheduling

### Optimize for common cases

- Write in assembler

- Non-critical paths written in C++

- But still fast as possible

- Avoid high-level language overhead

- Function call state preservation

- Incompatible code optimizations

- We want every cycle possible!

- At least sometimes ...

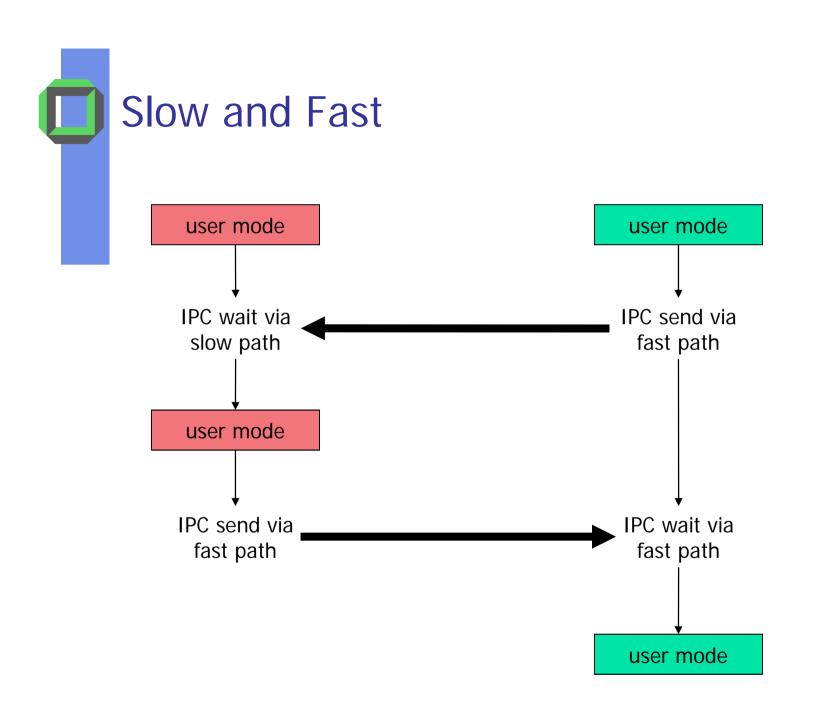

# **IPC Requirements for Fast Path**

- Untyped message

- Single runnable thread after IPC

- Must be valid call-like IPC

- Send phase

- Target is already waiting

- Receive phase

- Sender is **not** ready to couple, causing us to block

- Switch threads, originator blocks

- No receive timeout

- Send timeout can be ignored: receiver is waiting

- Xfer timeouts do not apply for untyped messages

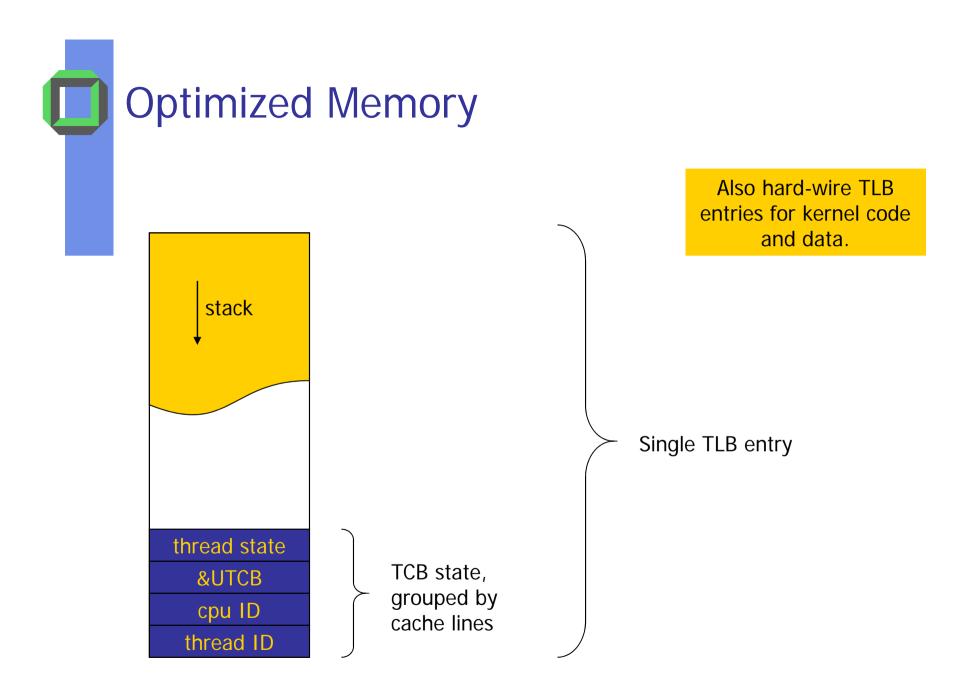

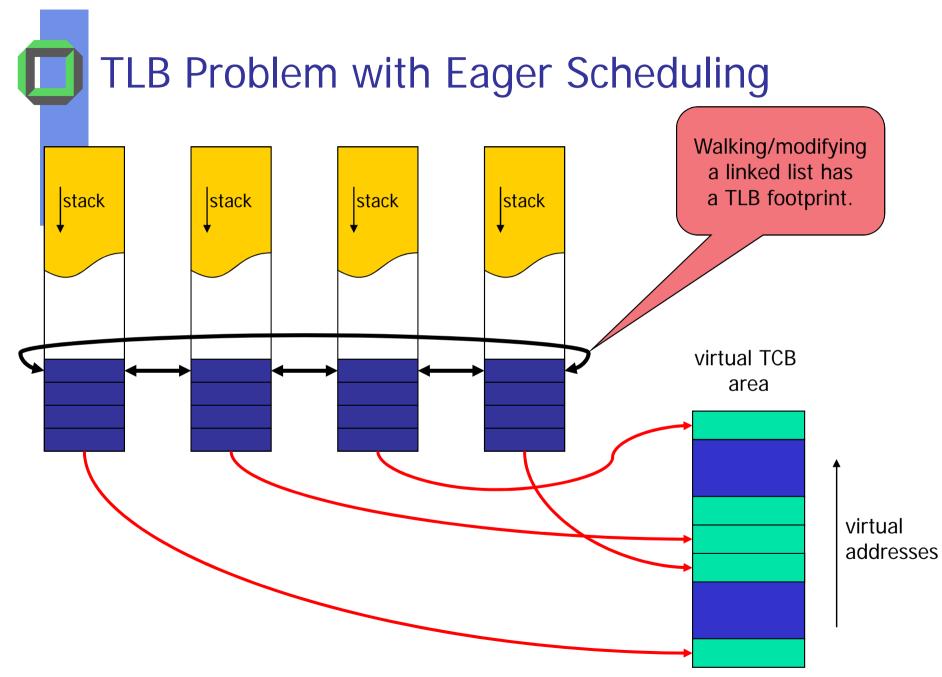

# Memory is Forbidden

- Memory references are slow

- Avoid in IPC

- E.g., use lazy scheduling

- Avoid in common case

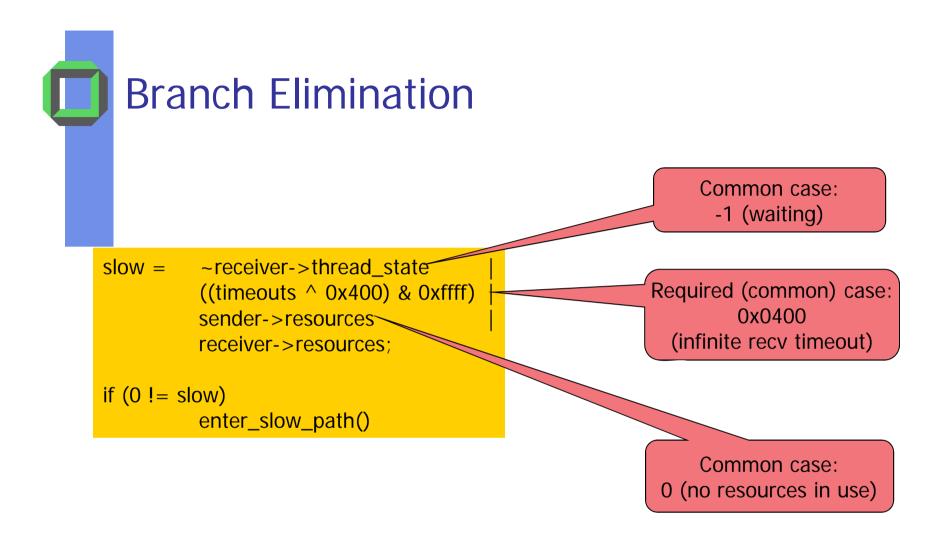

- E.g., (xfer) timeouts

- Microkernel should minimize artifacts

- Cache pollution

- TLB pollution

- Memory bus

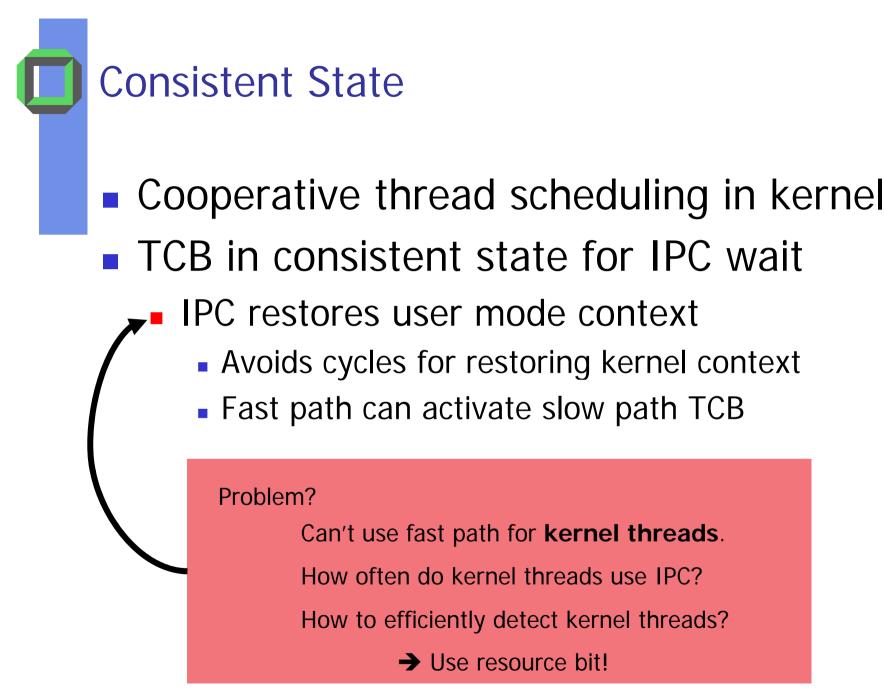

- Do not update the scheduling lists

- Blocked sender remains in ready list

- Check real thread state when dispatching

- May be released before being scheduled

avoids list manipulations

- Unblocked receiver not added to ready list

- Appended to ready list at end of timeslice

- May block before

- ⇒ avoids list manipulations

- Reduces branch prediction foot print

- Avoids mispredictions, stalls, and flushes

- Slightly increases latency for slow path

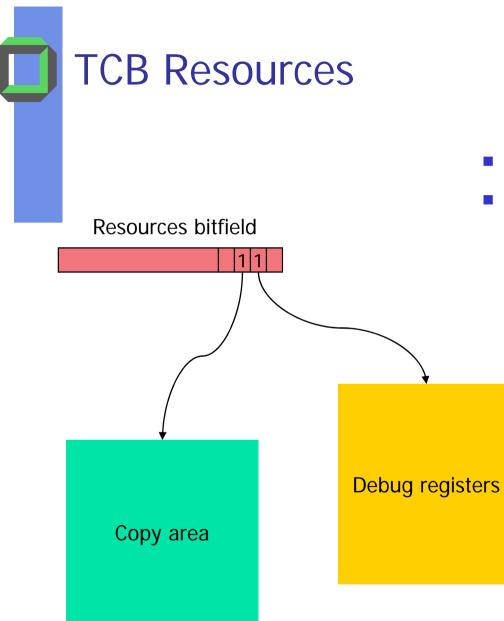

- One bit per resource

- Fast path checks entire word

- If not 0, jump to resource handlers

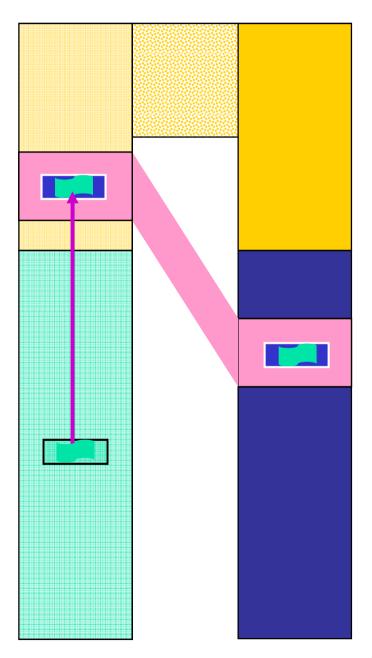

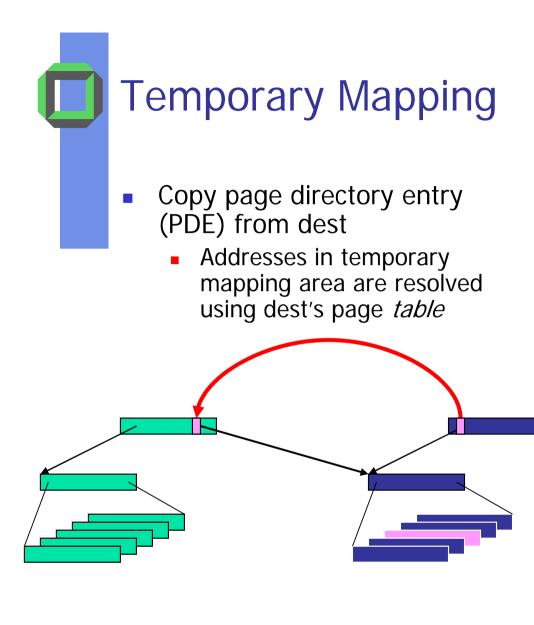

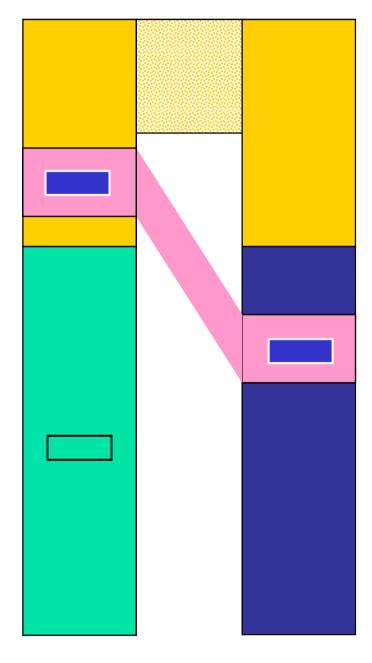

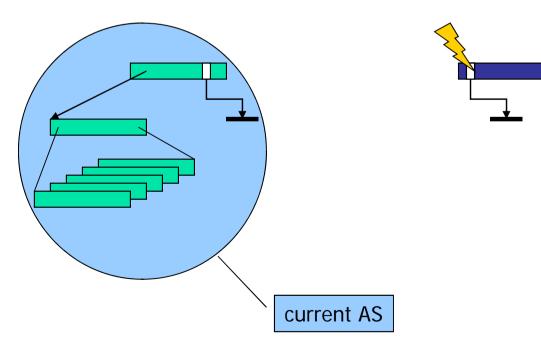

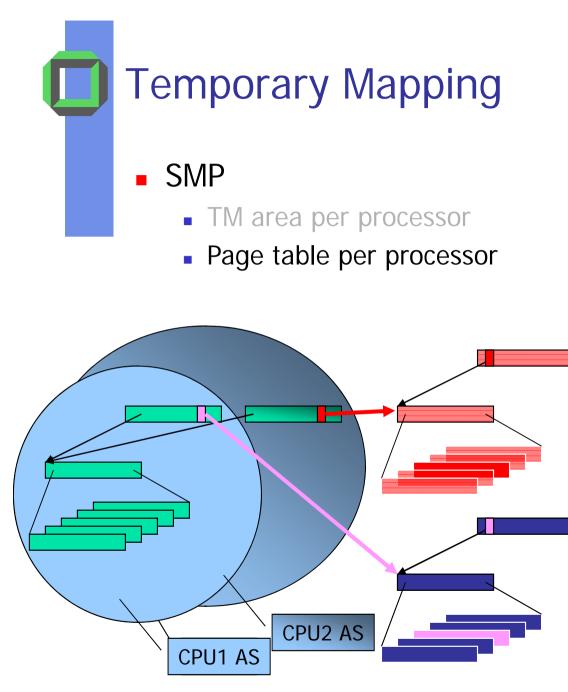

inter-address space IPC

# IPC Implementation

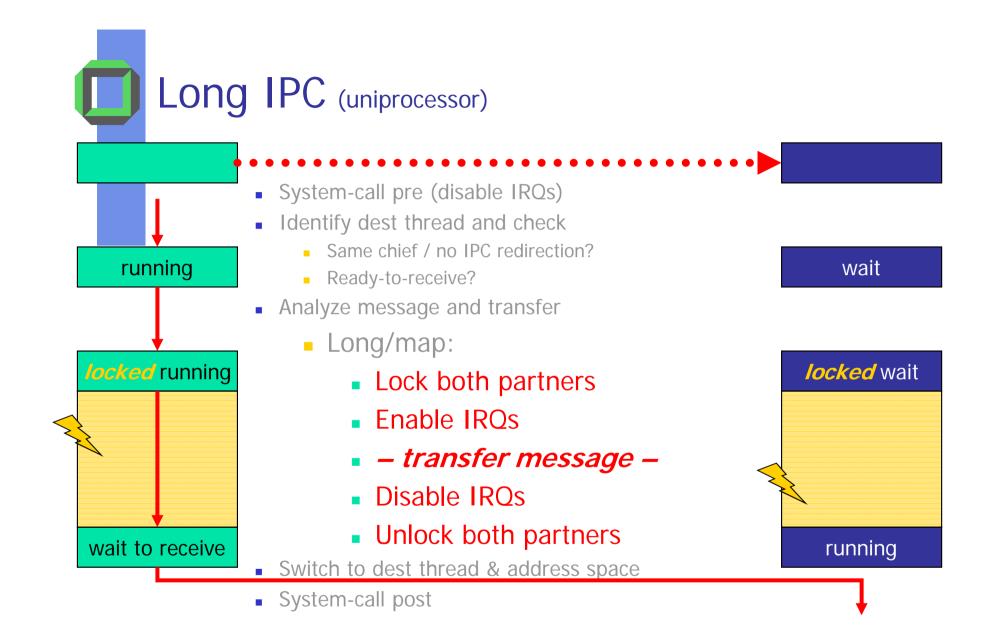

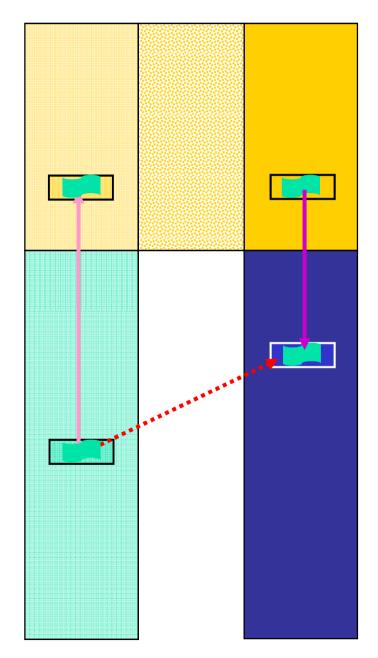

# Long IPC

- System-call pre (disable IRQs)

- Identify dest thread and check

- Same chief / no IPC redirection?

- Ready-to-receive?

- Analyze message and transfer

- Long/map:

Preemptions possible! (end of timeslice, device interrupt...)

Pagefaults possible! (in source and dest address space)

• Switch to dest thread & address space

In transfer message –

System-call post

- System-call pre (disable IRQs)

- Identify dest thread and check

- Same chief / no IPC redirection?

- Ready-to-receive?

- Analyze message and transfer

- Long/map:

- Lock both partners

- transfer message –

### Unlock both partners

- Switch to dest thread & address space

- System-call post

Preemptions possible! (end of timeslice, device interrupt...)

Pagefaults possible! (in source and dest address space)

- System-call pre (disable IRQs)

- Identify dest thread and check

- Same chief / no IPC redirection?

- Ready-to-receive?

- Analyze message and transfer

- Long/map:

- Lock both partners

- Enable IRQs

- transfer message –

- Disable IRQs

- Unlock both partners

- Switch to dest thread & address space

- System-call post

Preemptions possible! (end of timeslice, device interrupt...)

Pagefaults possible! (in source and dest address space)

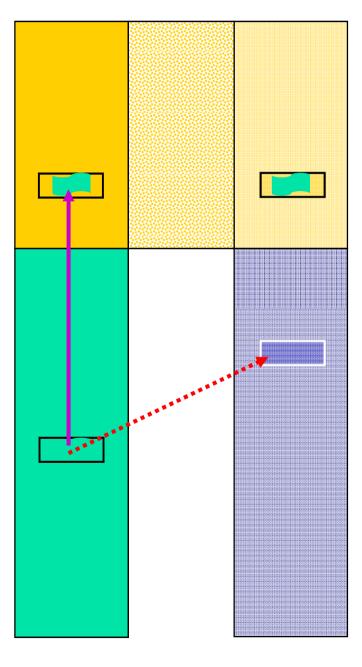

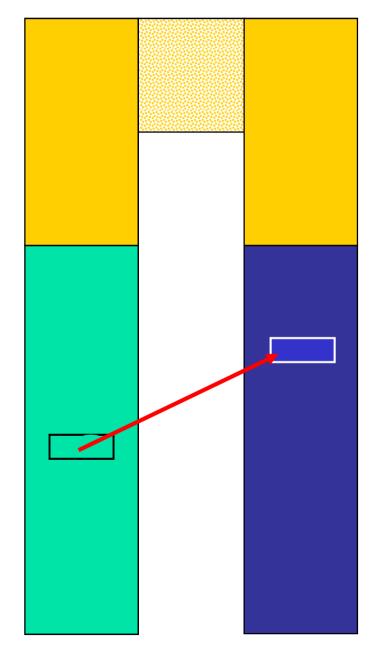

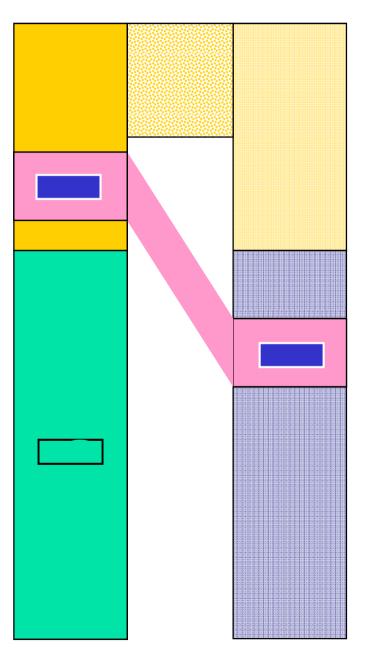

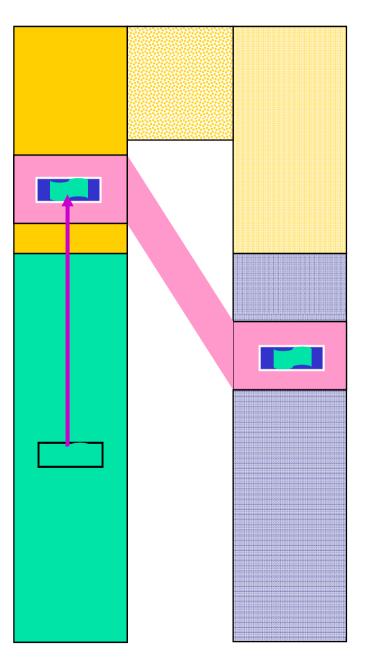

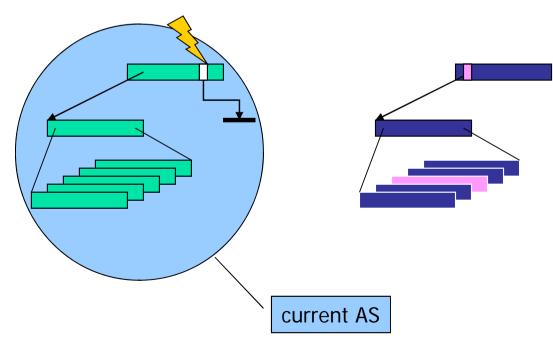

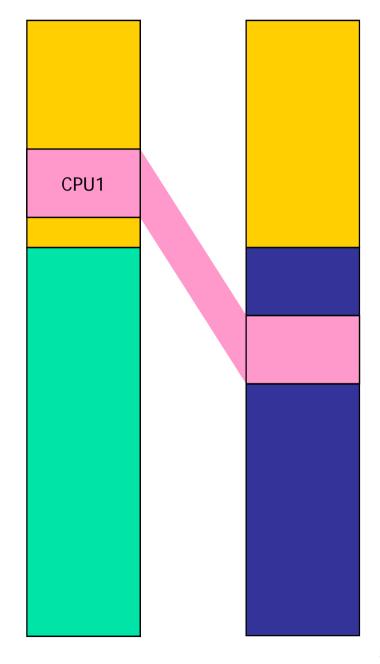

- Switch spaces

- Copy into kernel buffer

- Switch spaces

- Copy out of kernel buffer

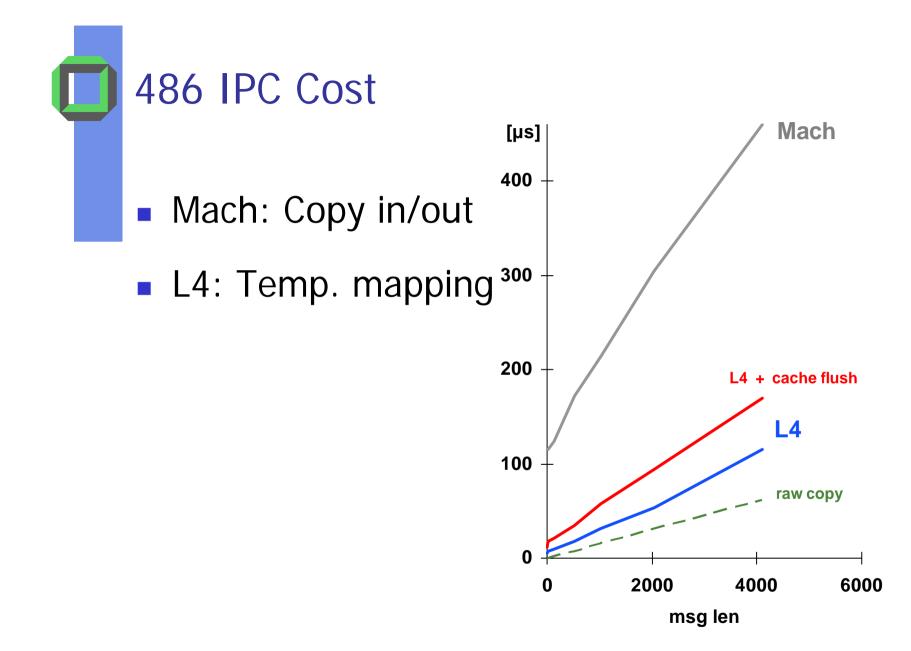

- Costs for *n* words

- 2×2n r/w operations

- $3 \times n/8$  cache lines

- 1×n/8 cache misses (small n)

- 4×n/8 cache misses (large n)

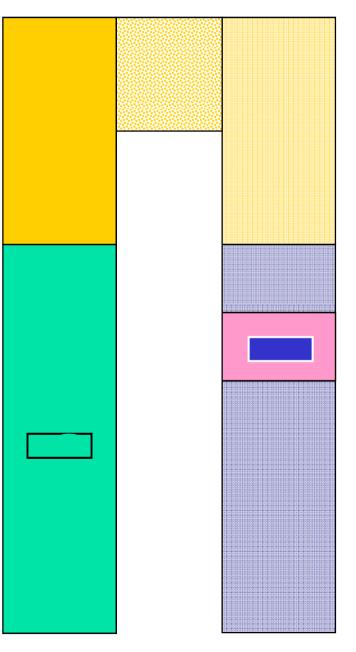

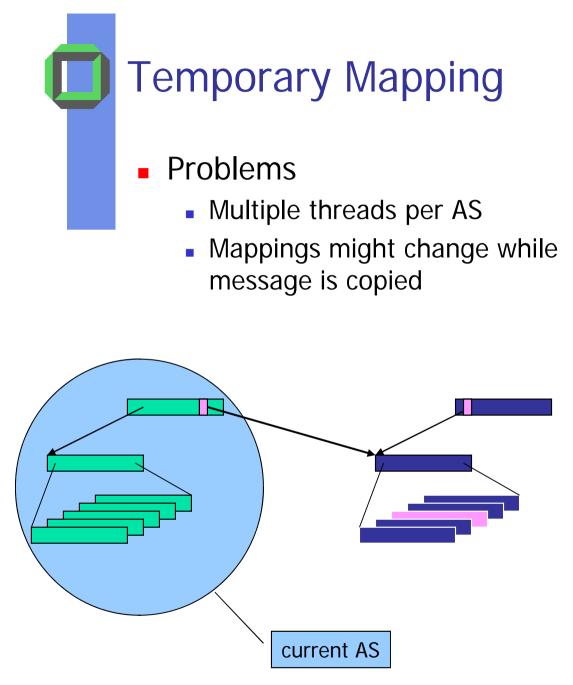

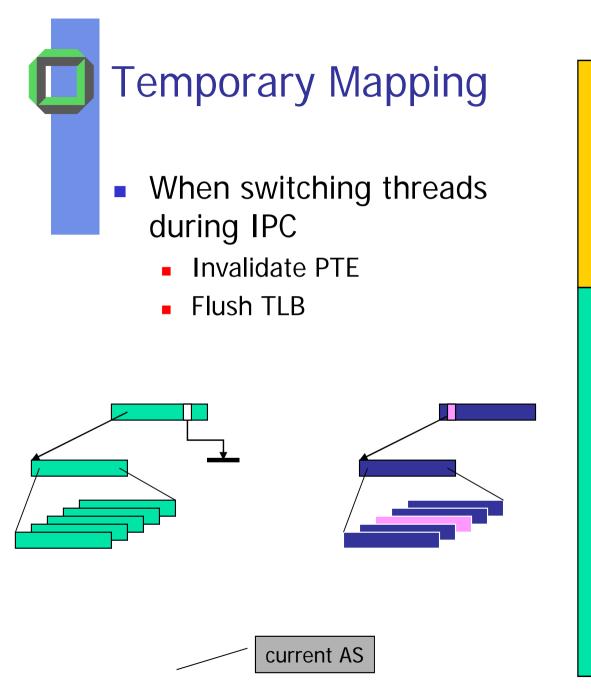

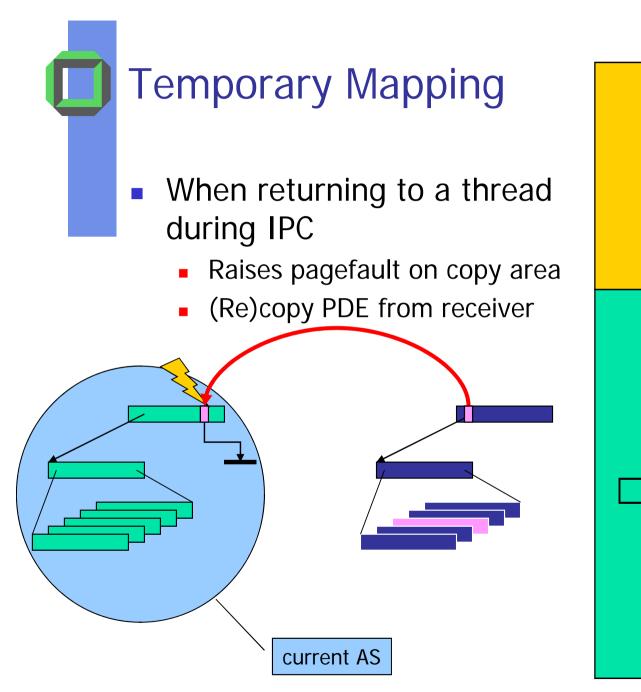

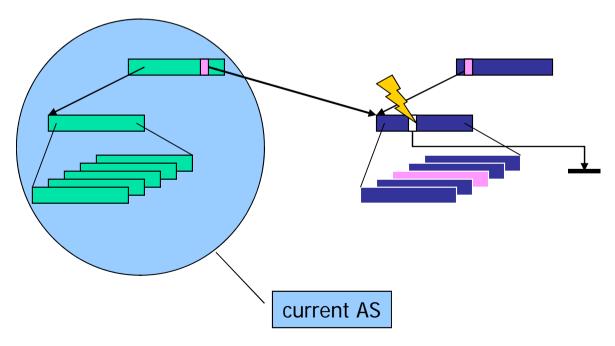

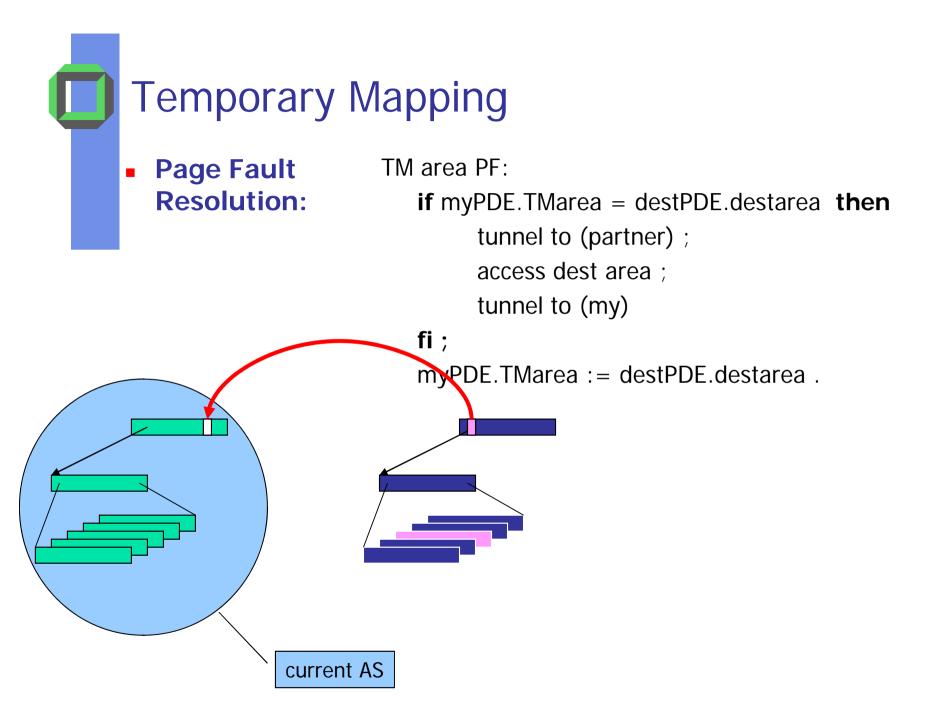

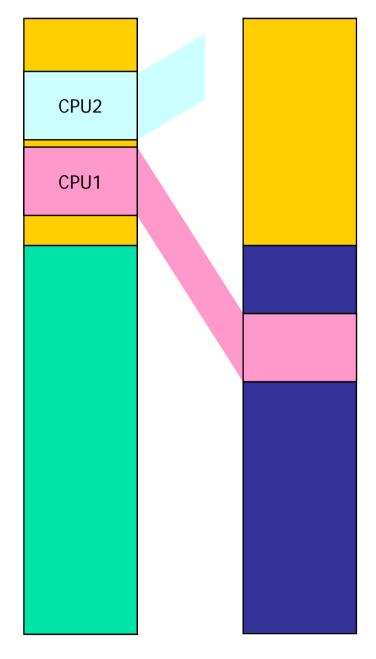

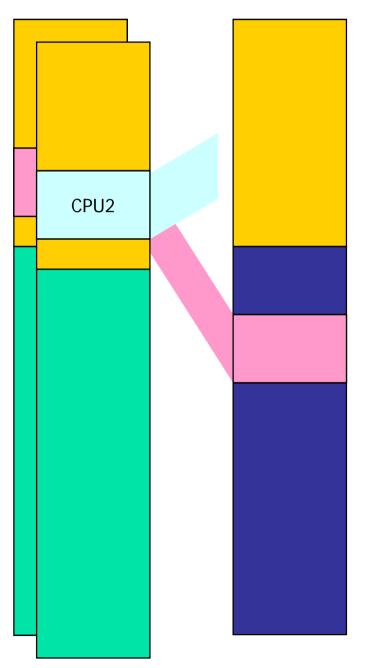

Map into source AS (kernel)

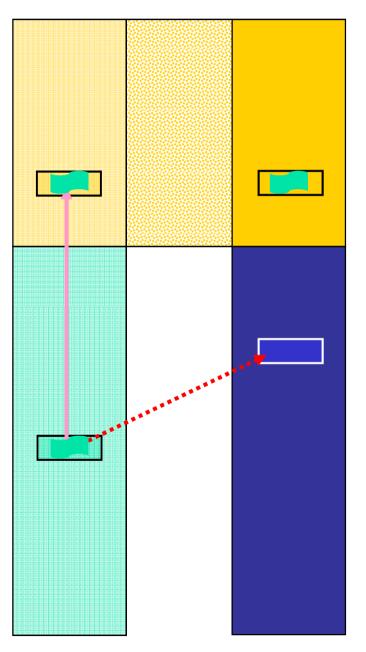

- Map into source AS (kernel)

- Copy data

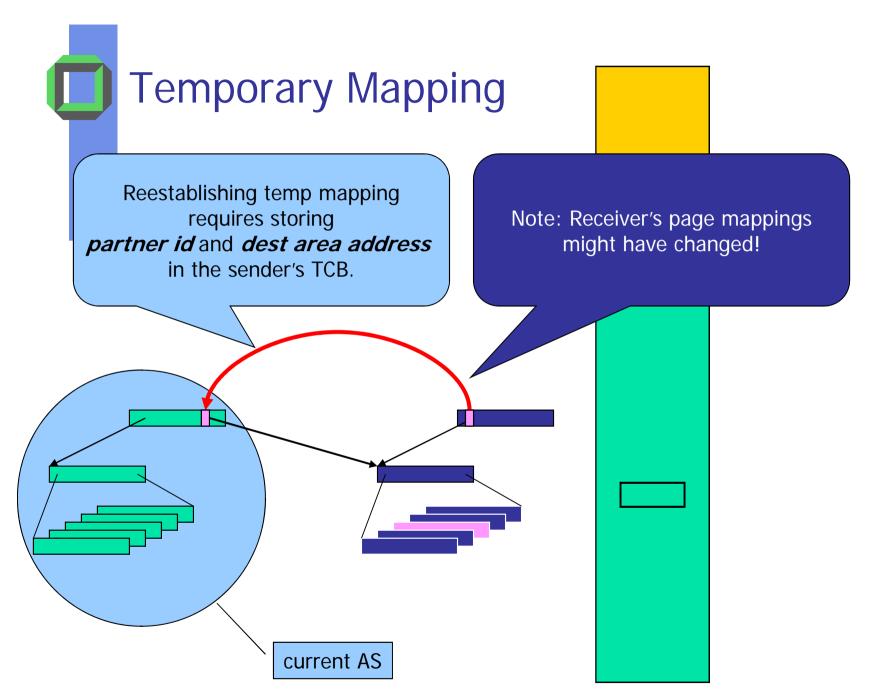

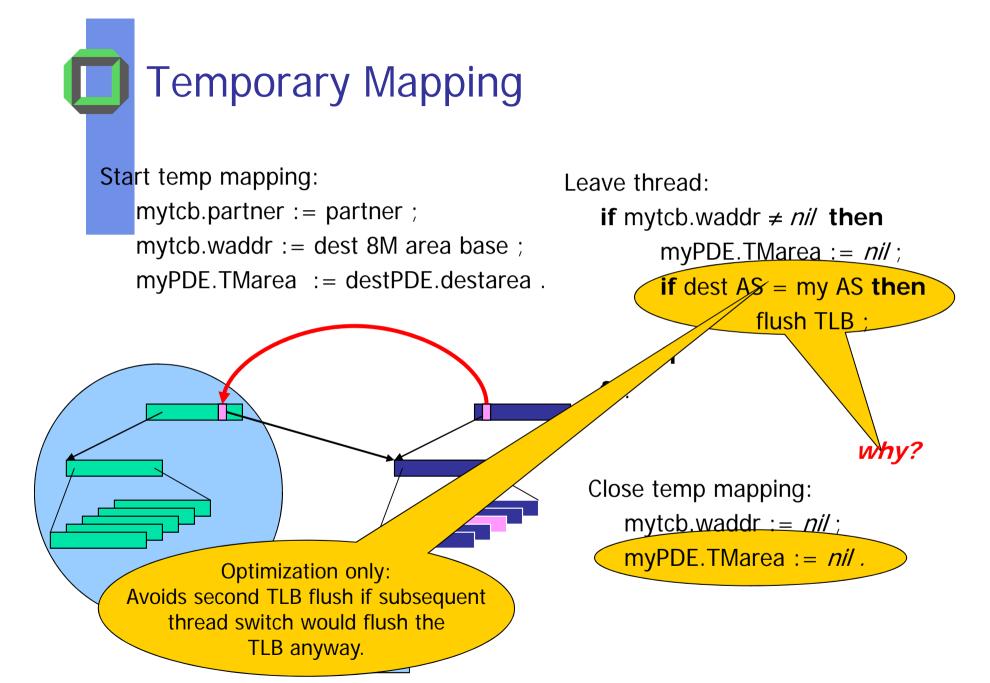

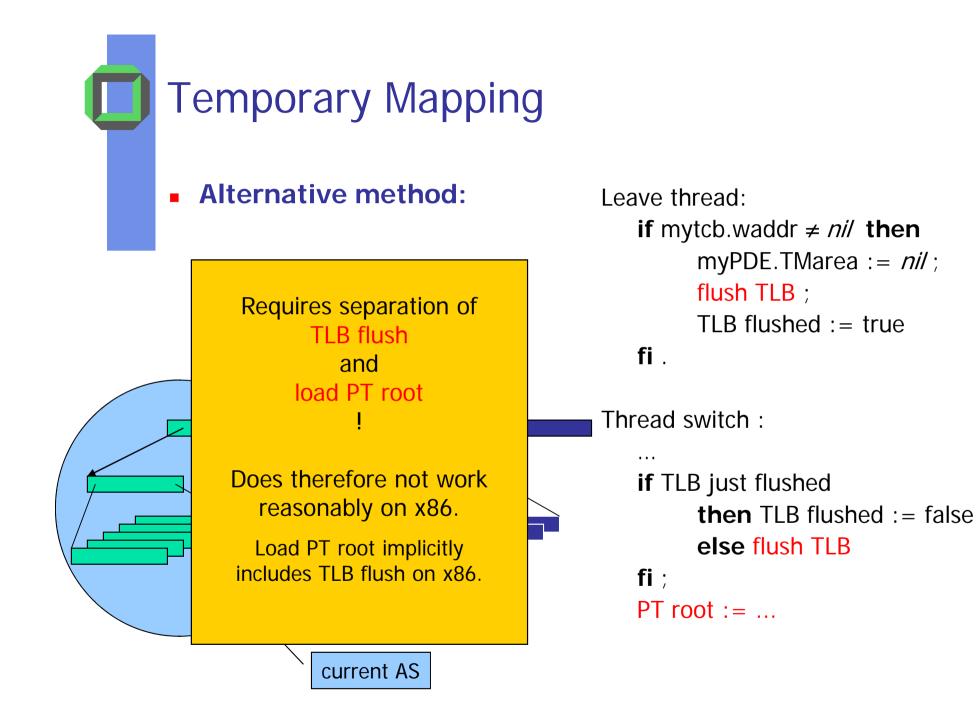

- Map into source AS (kernel)

- Copy data

- Switch to dest space

How long to keep PTE?What about TLB?

## Cost Estimates for Copying *n* Words

|                               | Copy in - copy out | Temporary mapping    |

|-------------------------------|--------------------|----------------------|

| R/W operations                | 2 × 2 <i>n</i>     | 2 <i>n</i>           |

| Cache lines                   | 3 × <i>n</i> /8    | 2 × <i>n</i> /8      |

| Small n overhead cache misses | <i>n</i> /8        | 0                    |

| Large n cache misses          | 5 × <i>n</i> /8    | 3 × <i>n</i> /8      |

| Overhead TLB misses           | 2                  | n / (words per page) |

| Startup instructions          | 0                  | 50                   |

(assuming 8 words/cache line)