Universität Karlsruhe (TH) Institut für Betriebs- und Dialogsysteme Lehrstuhl Systemarchitektur

# Multi-Architecture Operating Systems

Ovidiu Dobre

Diplomarbeit

Verantwortlicher Betreuer: Prof. Dr. Alfred Schmitt Betreuende Mitarbeiter: Dipl.-Inf. Espen Skoglund

4 October 2004

Hiermit erkläre ich, die vorliegende Arbeit selbständig verfasst und keine anderen als die angegebenen Literaturhilfsmittel verwendet zu haben.

I hereby declare that this thesis is a work of my own, and that only cited sources have been used.

Karlsruhe, den 4. October 2004

Ovidiu Dobre

#### Abstract

Requirements for high-performance computing have led hardware designers to construct multiprocessor systems using different processor architectures and thus providing best computing performance for a specific computing problem. The integration of different processor architectures is also employed in processor designs to offer compatibility for today's mainstream processor architectures. Examples are the Itanium and the AMD-64 processors which offer compatibility for the IA-32 architecture. This trend in hardware technology needs to be supported by advances in software technology.

This thesis will attempt to provide design solutions for operating systems in tightly-coupled heterogeneous systems. The case study of an Itanium-based system will provide an answer concerning the suitability of the theoretical solution.

### Acknowledgments

I would like to thank my supervisor Espen Skoglund for his expertise and patient support which made this work possible. In addition, I am thankful to all members of the System Architecture Group which constantly supported me all this time: Uwe Dannowski, Jens Doll, Sebastian Biemüller, Volkmar Uhlig, Joshua LeVasseur, Gerd Liefländer, Daniel Kirchner, Stefan Götz, Ulf Vatter, Christian Ceelen and Jan Stöß.

### Contents

| 1 | Introduction                                                                              | 9              |

|---|-------------------------------------------------------------------------------------------|----------------|

|   | 1.1 Background1.1.1 The case for heterogeneous computing1.1.2 Architectural compatibility | 9              |

|   | 1.2 Motivation and problem definition                                                     |                |

|   | 1.3 Approach                                                                              | 11             |

|   | 1.4 Construction of the thesis                                                            | 12             |

| 2 | Related Work                                                                              | 13             |

|   | 2.1 RACE: Heterogeneous Multicomputer System                                              | 13             |

|   | 2.2 InterWeave: Shared State for Heterogeneous Distributed Systems                        | 14             |

|   | 2.3 IA-32 support in IA-64 Linux                                                          | 16             |

| 3 | Design of Multi-Architecture Operating Systems (MA/OS)                                    | 18             |

|   | 3.1 Computing systems                                                                     | 18             |

|   | 3.2 SPMA computing systems                                                                | 20             |

|   | 3.3 MPMA computing systems                                                                | 21             |

|   | 3.4 Design models                                                                         | 23             |

|   | 3.5 User-level support for heterogeneity                                                  | 24             |

|   | <ul> <li>3.6 Native and Secondary Architectures</li></ul>                                 | 27<br>30       |

|   | <ul> <li>3.7 Equal opportunity</li> <li>3.7.1 Global data structures</li></ul>            | 33<br>34<br>37 |

|   | 3.8 Design framework of a MA/OS                                                           | 41             |

| 4 | Case study of a MA/OS: L4 and Itanium                                                                                                                                                                                                                                                                      | 42                                                 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   | 4.1 Motivation                                                                                                                                                                                                                                                                                             | 42                                                 |

|   | 4.2 Description of the experimental approach                                                                                                                                                                                                                                                               | 42                                                 |

|   | 4.3 Support for IA-32 in Itanium processor<br>4.3.1 Support at IA-64 ISA Level<br>4.3.2 Support at Processor Level                                                                                                                                                                                         | 44                                                 |

|   | 4.4 Horizontal design: IA-32 emulation layer on an IA-64 kernel<br>4.4.1 IA-32 Emulation Layer<br>4.4.2 IA-32 Exception Handling<br>4.4.3 IA-32 Memory Segmentation<br>4.4.4 Transition between IA-32 and IA-64                                                                                            | 50<br>51<br>53<br>54                               |

|   | 4.5 Vertical design: L4Ka::Pistachio                                                                                                                                                                                                                                                                       | 57                                                 |

|   | <ul> <li>4.6 Co-design process of the MA/OS</li> <li>4.6.1 IA-32 emulation layer in Pistachio IA-64</li> <li>4.6.2 IA-32 Exception Handling in Pistachio IA-64</li> <li>4.6.3 IA-32 Memory Segmentation in Pistachio IA-64</li> <li>4.6.4 Transition between IA-32 and IA-64 in Pistachio IA-64</li> </ul> | 59<br>68<br>69                                     |

|   |                                                                                                                                                                                                                                                                                                            |                                                    |

| 5 | Evaluation of the implementation                                                                                                                                                                                                                                                                           | 70                                                 |

| 5 | <b>Evaluation of the implementation</b><br>5.1 Evaluation of design requirements                                                                                                                                                                                                                           |                                                    |

| 5 | _                                                                                                                                                                                                                                                                                                          | 70                                                 |

|   | 5.1 Evaluation of design requirements                                                                                                                                                                                                                                                                      | 70<br>71                                           |

|   | 5.1 Evaluation of design requirements<br>5.2 Performance of IA-32 threads                                                                                                                                                                                                                                  | 70<br>71<br><b> 77</b>                             |

|   | <ul><li>5.1 Evaluation of design requirements</li><li>5.2 Performance of IA-32 threads</li><li>Analysis</li></ul>                                                                                                                                                                                          | 70<br>71<br><b> 77</b><br>77                       |

|   | <ul> <li>5.1 Evaluation of design requirements</li></ul>                                                                                                                                                                                                                                                   | 70<br>71<br><b>77</b><br>77<br>78                  |

| 6 | <ul> <li>5.1 Evaluation of design requirements</li></ul>                                                                                                                                                                                                                                                   | 70<br>71<br>77<br>77<br>78<br>79                   |

| 6 | <ul> <li>5.1 Evaluation of design requirements</li></ul>                                                                                                                                                                                                                                                   | 70<br>71<br>77<br>77<br>78<br>79<br><b>80</b>      |

| 6 | <ul> <li>5.1 Evaluation of design requirements</li> <li>5.2 Performance of IA-32 threads</li> <li>Analysis</li> <li>6.1 Functionality vs. Performance</li> <li>6.2 The microkernel approach</li> <li>6.3 Linux based MA/OS</li> <li>Conclusions and Future Work</li> </ul>                                 | 70<br>71<br>77<br>77<br>78<br>79<br>80<br>80       |

| 6 | <ul> <li>5.1 Evaluation of design requirements</li></ul>                                                                                                                                                                                                                                                   | 70<br>71<br>77<br>77<br>78<br>79<br>80<br>80<br>81 |

# Chapter 1 Introduction

This chapter presents the topic of this thesis. A background of the research area together with the considered approach is given.

### 1.1 Background

#### 1.1.1 The case for heterogeneous computing

The computer industry today shows an increasing technological trend towards the construction of heterogeneous computing systems. These computing systems are composed of multiple, independent but cooperating processor cores.

The main reason for constructing heterogeneous computing system is the fact that no microprocessor architecture has yet been proven efficient for the large diversity of computing problems. Applications may have different processing requirements which may imply support of different computing models ranging from simple additions to vector operations, floating point multiplications and signal-processing. Current trends in hardware technology provide either general-purpose processors which perform *acceptably* for a large scale of computing models or specialized processor architectures which are tuned to solve a specific computing problem. For a given computing problem, the processing throughput of general-purpose processors may fail drastically in face of specialized processors, designed to provide a maximum computing performance for a specific processing requirement. Therefore, to achieve a maximum throughput for an application requiring support of different computing models, computing systems often integrate different specialized processors. Each specialized processor in the system receives workload according to its computing model, while the results are gathered to provide a global solution.

These computing systems are built today from a collection of workstations connected over a high-speed network. This simplicity of interconnection of different processor architectures is practically the driving force in constructing this type of computing systems. However, this simplicity of construction doesn't always meet system requirements like reduced size, power consumption and cost. Such system requirements are found in embedded system applications, which extensively use the computing performance of heterogeneous computing [1]. In this case, the simple interconnection of a collection of workstations doesn't provide a viable solution and a better integration of different processor architectures is required. This integration eventually leads to tightly-coupled computing systems having different processor architectures sharing a main memory.

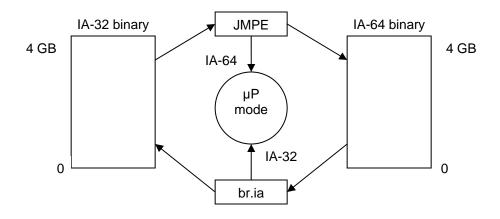

### 1.1.2 Architectural compatibility

A second reason for designing heterogeneous computing systems is simply to offer system compatibility with certain processor architectures. The integration of different processor architectures is not intended to provide better processing throughput, but it is intended to offer either backward compatibly for a certain processor architecture or an integration bridge with existing computing systems. A direct applicability of this approach is illustrated today by the passage from 32 to 64 bit computing systems. Processor architectures like IA-64 and AMD-64 integrate backward support for the IA-32 architecture in order to smooth out the passage to the new processor architecture. Applications developed for IA-32 will be able to run unmodified on both IA-64 and AMD-64 architectures. If we see the first reason for designing heterogeneous operating systems as being related to performance, this second reason is strictly related to functionality. In both cases, multiple processor architectures are required to access a shared main memory.

### 1.2 Motivation and problem definition

Current approaches for heterogeneous systems employ middleware architectures and virtual machines, which are user-level layers attempting to provide a uniform view of heterogeneous computing resources distributed over all computing nodes. These solutions for heterogeneous computing are extensively used in loosely-coupled systems, but their applicability for tightlycoupled heterogeneous systems is questionable. First, the user-level middleware introduces performance penalties for high-performance computing. In tightlycoupled systems, the presence of shared memory enables kernel-level mechanisms for communication over architectural heterogeneity, which could provide better performance results than the user-level approach. Secondly, there is a functional requirement concerning processors integrating multiple architectures: user-level binaries should be able to exploit any of the underlying processor architectures. In the latter case, the operating system must offer userlevel support for any processor architecture. As such, the solution strictly depends on kernel-level mechanisms. Designing such an operating system is the goal of this thesis:

Provide design solutions for operating systems in tightly-coupled computing systems exhibiting heterogeneous processor architectures.

This problem definition reveals some issues which will directly influence the design of such an operating system:

1. The nature of the computing system: could either be represented by a single processor with multiple architectural states or by multiprocessor systems with heterogeneous processor architectures.

2. Heterogeneity of processor architectures: is represented by the incompatibility of binary code and data type representation.

### 1.3 Approach

The design of an operating system is highly influenced by the nature of the computing system. A complete study of the targeted computing context will therefore be undertaken. Each system configuration may require different design approaches.

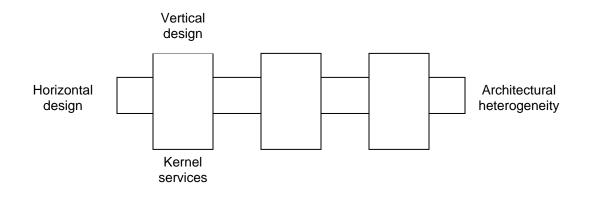

Another important element in the design is providing solutions to incompatibles introduced by the architectural heterogeneity of the system. The binary incompatibility radically influences the way in which the kernel can be constructed. That is, one kernel image can usually not execute on different processor architectures, so the kernel must be tailored for each processor architecture. In addition to binary incompatibility, the presence of different data representations constitutes an obstacle for communication across different processor architectures. Therefore, the design should also provide a solution for communication in a heterogeneous environment.

The design approach requires a case study for performance and functional analysis. We will use as such the Itanium processor to provide experimental results. Itanium natively supports the IA-64 architecture together with the IA-32 architecture, and therefore constitutes a viable example of a heterogeneous computing system. This experimental approach will provide answers concerning the suitability of the theoretical solution.

### 1.4 Construction of the thesis

The rest of the thesis is organized as follows:

- **Chapter 2** Discusses some of the main research trends in the field of the heterogeneous computing and their possible implications on the topic of this thesis.

- **Chapter 3** Presents the proposed solution. This solution will focus on providing multiple design models, each with different applicability levels depending on the nature of the computing system. This proposed solution is only a theoretical approach without an experimental evaluation.

- **Chapter 4** Discusses a case study of the proposed solution: Itanium processor (IA-64 and IA-32) and L4 microkernel. The design of the operating system will be based on a design model which shows better applicability for this specific case study.

- **Chapter 5** Presents the experimental evaluation of the operating system design discussed in the previous chapter.

- **Chapter 6** Analyzes the suitability of the theoretical solution with respect to the experimental results.

- **Chapter 7** Gives a recapitulation of the main issues discussed in this thesis: motivation, proposed solution and experimental results. A final conclusion is drawn concerning the research topic of this thesis and directions for future work are proposed.

### **Chapter 2**

### **Related Work**

This chapter gives an overview of the main approaches in heterogeneous computing systems. The focus is set on two architectures which define the current trends in heterogeneous computing: the RACE architecture which provides a solution (hardware and software) for scalable heterogeneous computing systems and InterWeave, a middleware for shared state in distributed heterogeneous systems. Both architectures are based on multicomputer systems. An addition, this chapter presents an example of an operating system (IA-64 Linux) supporting binaries of two processor architectures, IA-32 and IA-64.

### 2.1 RACE: Heterogeneous Multicomputer System

The RACE architecture [2] delivers a complete hardware-software solution for heterogeneous multicomputer systems.

The hardware approach of RACE is not as relevant as the software approach for the research topic of this thesis, but it deserves at least an overview, mainly for its remarkable architecture in terms of modularity and scalability. The hardware architecture of RACE is composed of computing nodes. I/O nodes and connection fabric (connecting the nodes of the system either through bus architecture or switching network). Each computing node is composed of one or more processors of the same architecture, local DRAM memory and an ASIC<sup>1</sup> providing a DMA controller (offering access at local memory to any other computing nodes) and address mapping logic (enabling the local processors to access any DRAM location in any remote computing node). Different computing nodes can have different architectures. In short, the hardware architecture is represented by heterogeneous computing nodes with local physical memory and a mechanism for memory access at any physical memory from any computing node in the system. Every memory location in the system can be accessed by any processor in the system, so a cache coherency problem could be raised. The problem of cache coherency has an efficient solution in this case due to physical distribution of memory: a computing node is concerned by cache coherency only in relationship with its own local memory. Whenever a processor either reads or writes data from/into a remote memory, each local processor sharing that memory invalidates the cache entry corresponding to the accessed data. This mechanism reduces drastically the amount of traffic for "snooping" memory

<sup>&</sup>lt;sup>1</sup> Application-Specific Integrated Circuit

addresses, as a processor has to watch only the local memory bus which is composed from a reduced number for processors (till three processors) comparing with the entire computing system. This solution for cache coherency provides data coherency for *hardware-shared* memory (accesses on same physical memory location), but it doesn't solve *software-shared* memory coherency (information replicated on multiple computing nodes on different physical memories). The software-shared memory problem requires a software approach due to complexity of "bookkeeping" at hardware level of all the memory transactions on different computer nodes. Moreover, a software approach is better suited in this case as it can exploit the specific requirements of an application in terms of software-shared memory. The software approach for data coherency is usually implemented by a middleware layer.

The question now concerns how the software architecture of RACE couples with the hardware architecture. The solution proposed by RACE is largely influenced by the modularity of the hardware architecture: each processor has its own single-processor operating system, completely independently from any other operating system running on remote computing nodes. This approach allows removal or insertion of computing nodes with no effect at kernel level for already existing operating system instances. As such, the kernel is not required to provide support for heterogeneous computing. Threads running on different computing nodes are independent, each having its own address space. There is however a mechanism implemented on top of this operating system which transparently handles the communication among computing nodes and the access on physical memory located on remote computing nodes. This mechanism enables software shared memory among remote threads.

This software approach is the result of modularity of the hardware architecture which enforces modularity at operating software level. The physical distribution of the memory makes practically impossible to achieve a tightlycoupled operating system. The only suitable solution for this hardware design is a single-processor operating system per computing node with a user-level mechanism for inter-processor communication.

In conclusion, the RACE architecture provides a good design model of user-level support for heterogeneous computing.

# 2.2 InterWeave: Shared State for Heterogeneous Distributed Systems

InterWeave is a middleware architecture for distributed shared state [3]. This architecture is designed to provide a distributed shared state in systems ranging from tightly coupled multiprocessor system to distributed heterogeneous systems spread around different geographical locations.

As an alternative to message passing, InterWeave allows processes to share memory regions of their own address space across heterogeneous distributed computing nodes. This facility enables processes to share information

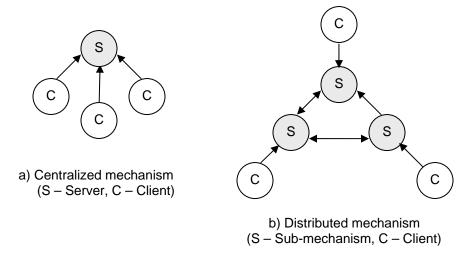

replicated around multiple locations with different data type representations. The shared information has a static structure (the structure of a replica doesn't change upon creation), but its content can change over time. All mechanisms for providing data coherency among replicas are provided by the middleware. The coherency mechanism is based on the server-client model. Servers manage a persistent copy of the replicated data and provide this data whenever a client requests it. Each time a client is started and connects to the server, a copy of the data is sent by the server to the client. Whenever a client updates its local copy of shared data, these updates are forwarded to the server which takes care of updating its persistent copy of the replicated data. Any request following an update will receive data which reflects the current distributed state. The applicability of the centralized model is based on communication scalability between server and clients (to avoid a bottleneck by increasing number of clients), communication reliability (to avoid transmission of erroneous data) and server reliability (to avoid crashes which will bring the entire system down). This coherency model has different variations ranging from full coherency (always obtain the most recent version of data) to relaxed coherency (which accepts a difference between the delivered version and the persistent copy managed by the server, either considering a time difference of the local copy or a percentage of information out-of-date). An important aspect for this centralized coherency model is the connection scalability: when having many accesses on global shared data, low connection scalability may transform the server in a bottleneck. This risk increases its chances when the targeted coherency model is full coherency and each access on global shared data needs to be confirmed by the server.

One important issue for a coherency mechanism is the protocol for delivering updates between clients and the server. InterWeave offers two concepts: polling and notifications. With pooling, the client regularly requests updates from the server. With notifications, the server has an active role of informing the client whenever an update on the client's data is required. Another aspect of the update protocol is the granularity of the data to be updated and transferred: transfer only the modified regions of shared data or transfer the entire shared data. The choice for a certain approach depends on the size of the update compared to the size of the shared data and the frequency at which updates are performed.

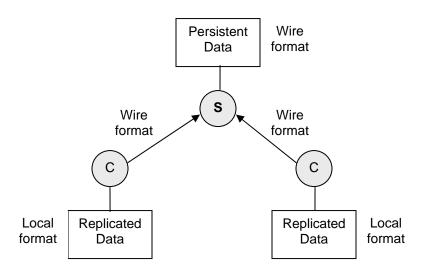

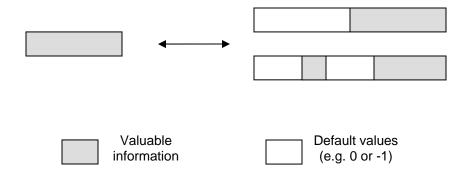

In addition to coherency mechanisms among distributed replicas, the InterWeave middleware provide mechanisms for exchanging data between computing nodes with heterogeneous data formats. The model proposed by InterWeave for exchanging data with heterogeneous representations is the model offered by all classical middleware systems like CORBA or .Net: conversion of data types from machine-specific format to a generic InterWeave format ("the wire format"). This generic format serves as exchange format between clients and the server (Figure 2.1). Another issue introduced by heterogeneity of data types is the usage of pointers on non-atomically shared data. Pointers to data types typically vary according to the size of data type representation (e.g. pointing to the next machine word value from a vector increases the pointer location with 4 bytes on 32 bit architectures and with 8 bytes on 64 bit architectures). Again this issue is solved by InterWeave by providing the concept of machine-independent pointers (MIP). To achieve independency from data type representations (especially data type sizes), the pointers are always handed out with direct reference to the addressed data type (e.g. a pointer to the third element of a word vector is handed out *literally* as the address of the vector + 2 words, instead of expressing the pointer in the equivalent number of bytes). Thus, pointers are no longer dependent on the size in bytes of each data type representation, but the measurement unit is the data type itself. Data updates exchanged between clients and server are therefore using Machine Independent Pointers.

Figure 2.1: InterWeave model for distributed shared state

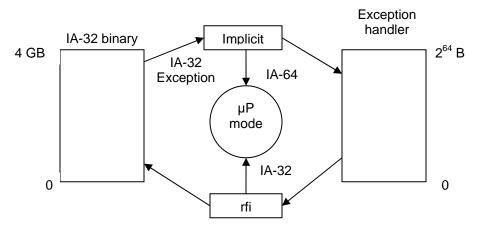

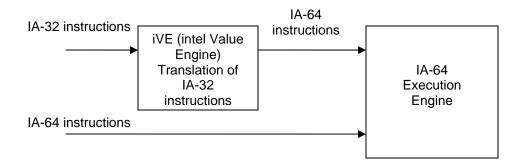

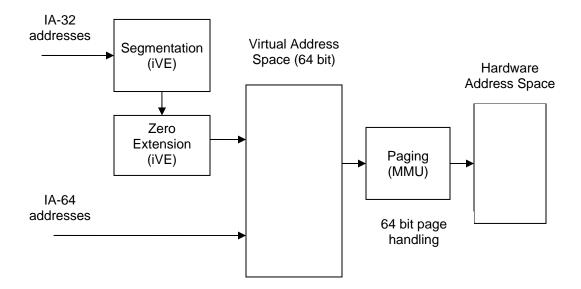

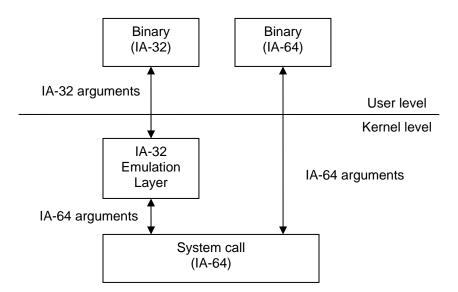

### 2.3 IA-32 support in IA-64 Linux

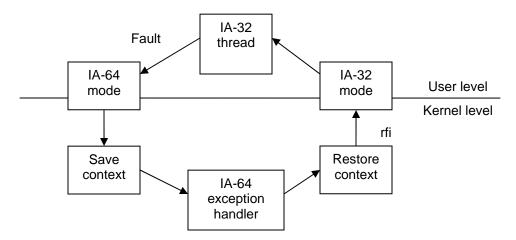

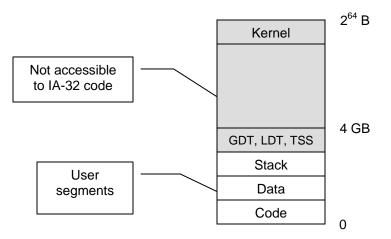

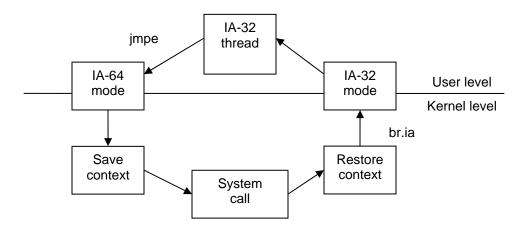

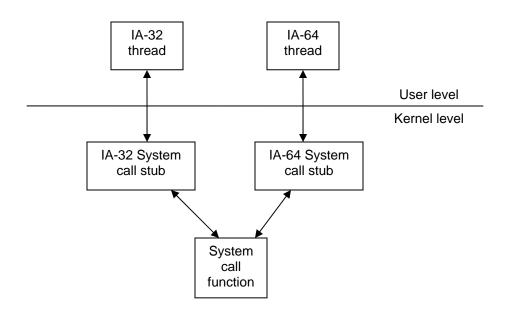

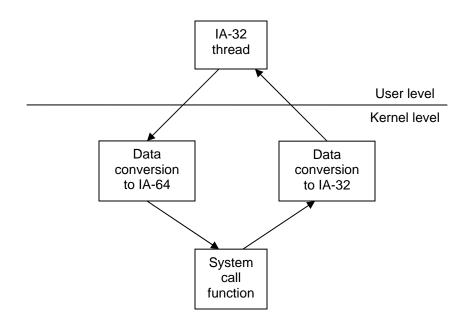

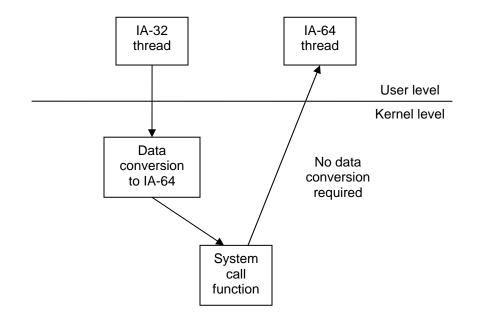

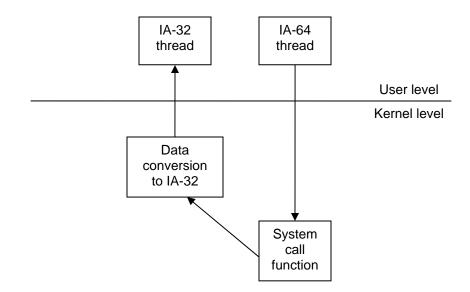

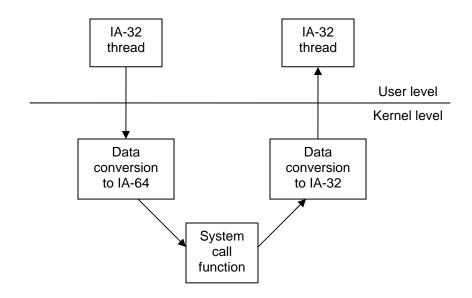

Linux IA-64 [4] is an example of an operating system offering support for two processor architectures: IA-32 and IA-64. This support is based on the Itanium's capability to execute both the IA-32 and the IA-64 instruction set. While the support for IA-64 user-level binaries is natively offered by the kernel, the Linux system interface for IA-32 user-level binaries is emulated based on the native implementation in IA-64. The Linux system interface is represented by a collection of systems calls. The main issue is the incompatibility in data representation between IA-32 and IA-64 arguments. For system calls which show no data incompatibility between IA-32 and IA-64, the IA-32 emulated interface is represented by a thin system layer which simply passes the arguments between the IA-32 thread and the IA-64 system call handler. In this case, the IA-32 system calls employ the IA-64 implementation. However, for system calls raising data incompatibility issues, IA-64 Linux provides different system call handlers for IA-32 and IA-64. This approach leverages an important amount of work for the IA- 32 emulated interface. In addition to system call interface, the IA-32 support includes additional mechanisms: IA-32 memory model, IA-32 absolute file system paths, IA-32 signal delivering, management of the I/O port space, preservation of IA-32 architectural registers.

In conclusion, IA-64 Linux provides an IA-32 execution environment which enables execution of heterogeneous applications composed of IA-32 and IA-64 binaries.

### **Chapter 3**

### **Design of Multi-Architecture Operating Systems (MA/OS)**

This chapter discusses the guidelines for designing a Multi-Architecture Operating System. We first study the nature of the computing systems requiring a MA/OS. Each of these computing systems will represent a base of discussion for the main design models of a MA/OS. In addition, a general approach for constructing this type of operating systems will be presented.

### **3.1 Computing systems**

The first issue in designing an operating system is finding the targeted computing system. According to Flynn's classification [5], computer systems can be divided in four classes based on the number of instruction and data streams. The classification doesn't take the processor architecture into consideration. However, heterogeneous systems can generally fit in the case of MIMD (Multiple Instruction/Multiple Data Streams), as they exhibit multiple instruction streams with associated data streams due to architectural heterogeneity.

A classification of computer systems which does take the processor architecture into consideration was proposed in [6] and it constitutes a result from the field of *heterogeneous computing*. The classification of heterogeneous systems is based on two orthogonal concepts: the number of *execution modes* and the number of *execution models*. The execution mode is related to the type of parallelism supported by the machine (e.g. vector, SIMD, MIMD). This concept is independent of the execution model, which refers either to different architectural states of the machine or to different performance levels (e.g. different clock rates). We will concentrate on the number of architectural states exhibited by the computing system, as the incompatibilities between different architectural states influence directly the design of the kernel. As such, the classification provides two categories which fit to our targeted computing system: Single Execution Mode/Multiple Machine Model (SEMM) and Multiple Execution Mode/Multiple *Machine Model* (MEMM) with the remark that the interest on machine model is strictly related to heterogeneity of architectural states and not to the performance within the same architectural family.

However, from the point of view of an MA/OS, there exists an additional criterion which is not taken in consideration in any of these classifications: the number of architectural states per processor. This criterion has an important

impact on designing an MA/OS. We therefore propose a classification that takes into account the number of *computing nodes* (labeled as processors) and the number of *architectural states*. These two criteria are orthogonal: a processor can have multiple architectural states, while an architectural state can be supported on multiple processors. Based on these two criteria, computing systems can be classified in four classes:

- 1. **SPSA** (Single Processor/Single Architecture): a mono-processor system

- 2. **SPMA** (Single Processor/Multi-Architecture): a mono-processor with multiple architectural states (e.g. Itanium, AMD-64)

- 3. **MPSA** (Multi-Processor/Single Architecture): a system composed of multiple processors with the same architecture (e.g. current SMP or homogeneous distributed systems)

- 4. **MPMA** (Multi-Processor/Multi-Architecture): a system composed of multiple processors exhibiting multiple architectural states

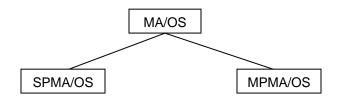

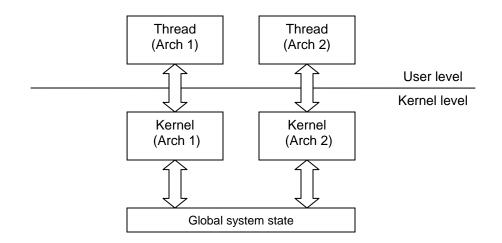

A MA/OS is exclusively related to multiple architectural states, so only two classes of the above classification are concerned: SPMA and MPMA. As such, there exist two types of MA/OS: SPMA/OS and MPMA/OS (Figure 3.1). In the case of MPMA systems, the focus of MA/OS is related to tightly-coupled systems as described in section 1.2.

Figure 3.1: Classification of MA/OS

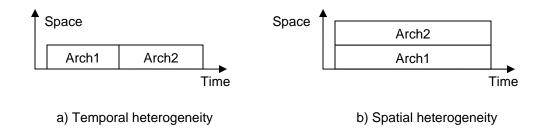

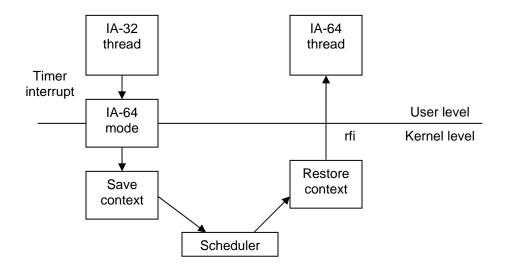

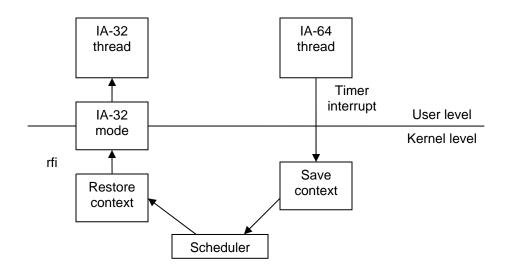

The reason for choosing the number of architectural states per processor as a criterion is related to the parallelism in execution of the different architectural states. A processor with multiple architectural states can execute in only one architectural state at the time. This type of systems exhibit temporal heterogeneity: at one single point in time, only one type of architectural state is present in the system. In contrast with SPMA systems, the MPMA systems exhibit spatial heterogeneity, as multiple processors with different architectures execute in parallel (Figure 3.2). As a consequence, each of these classes of MA/OS introduce different design issues to tackle: temporal heterogeneity may imply that the architectural state of the kernel changes with time, while the spatial heterogeneity may assume that multiple kernel instances with different architectures execute in parallel and share global structures.

Figure 3.2: Types of architectural heterogeneity in MA/OS

### 3.2 SPMA computing systems

The first computing system in the area of an MA/OS is the "Single Processor/Multi-Architecture" (SPMA) system. The SPMA system refers to a family of processors designed to offer more than one type of architectural support. This type of processors may be considered as a composition of logical processor cores, each logical core having its own architectural state, but sharing some of the processor's resources like the instruction and data bus or the cache memory. Yet, from all the logical cores, only one logical core is capable to access the shared processor resources at any single point in time. Examples of these processors are the Itanium and the AMD-64 which support two architectural states: IA-32 and IA-64.

The set of solutions to answer the requirement of architectural heterogeneity for user-level applicability can be divided into two classes, one class employing a single architectural state at kernel level, while the other class integrating the architectural heterogeneity at kernel level. Each of these approaches has its advantages and disadvantages, so the choice for a specific design model is influenced by other design requirements.

The first solution for designing a SPMA/OS employs a single architectural state at kernel level and it is based on current designs in single-processor systems. The kernel is developed for a single architectural state which generates a single kernel binary image. The user-level applications built for the kernel's architectural state will be able to directly invoke the operating system services. The missing piece from the puzzle is how to couple architectural heterogeneity at user-level with single architectural state at kernel level. Even if a user-level application was built for a different architectural state than the kernel's architecture, this application still needs to perform kernel requests. Therefore, the missing piece is a mechanism for communication across architectural heterogeneity between the kernel at one side and the user-level application at the other side. This mechanism is the only issue of this design. As an overview of this solution, one may notice that one architectural state has a higher degree of importance than all others as it defines the kernel's architectural state. All other architectural states are only supported at user-level. As any request for a kernel service is accomplished in one single architectural state of the system, this solution could also be modeled as a *master-client* approach: the kernel's architectural state is the master architecture while all other architectures are client architectures. The master architecture provides services in behalf of client architectures. From the point of view of the operating system, the master architecture performs all critical operations (e.g. kernel's system calls, exception handling) while client architectures serve only to execute non-critical operations (e.g. user-level binaries). From the user's perspective, this design approach could be regarded as *native and secondary architectures*.

The second design approach for a SPMA/OS employs architectural heterogeneity at kernel level. This design approach raises an important issue as any single machine binary cannot execute on multiple architectural states due to binary incompatibility. Therefore the binary code of the kernel has to be split up between architectural states. One acceptable solution is to provide a homogeneous kernel structure in term of architectural state and to implement this kernel structure for multiple architectural states. In this way, the binary incompatibility is solved by providing a kernel instance per each architectural state exhibited by the processor. Each kernel instance can provide kernel services to user-level applications built for the same architectural state. This design approach apparently solves the initial issue: provide architectural heterogeneity at user-level. Each user-level application can request kernel services as the operating system provides a kernel instance built for each architectural state exhibited by the system. The question now is how to construct such a single operating system image based on a set of architectural-dependent kernel instances. Looking at the first design approach of a SPMA/OS, the design issue was the interface point between the user's requirement for architectural heterogeneity and the kernel approach for single architectural state. The main issue of the second design approach is the interface at kernel level among multiple kernel instances. The second design approach can be labeled as an *equal* opportunity model: critical operations for the operating system can be performed in any architectural state by the appropriate kernel instance.

In conclusion, there are two main design approaches for SMPA operating systems. Both approaches still have an internal issue which will be discussed further in this chapter.

### **3.3 MPMA computing systems**

The second computing system in the area of MA/OS is the "Multi-Processor/Multi-Architecture" (MPMA) system. The term "MPMA" refers to multi-processor systems composed of processors with heterogeneous architectures connected through a system bus and sharing the main memory. Processors in such a hardware configuration are able to perform concurrent accesses on main memory which generate data coherency issues at cache level and require in addition exclusion mechanisms on shared data structures. These issues are the main research topic of SMP (Symmetric MultiProcessor) systems and solutions are either provided at hardware level (cache coherency protocols)

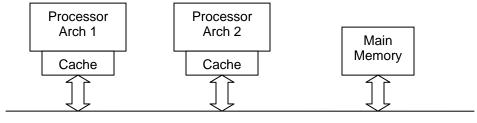

or at kernel level (exclusion mechanisms on shared data structures). The defining property of SMP systems is the homogeneous architecture of internal processors. This approach allows a smooth hardware coupling of processors on the shared memory bus and provides the ability of running the same kernel image on all processors based on same architectural state. The MPMA systems introduce an important difference with SMP systems in tightly-coupled multiprocessor systems, namely the architectural heterogeneity of processors sharing the main memory. These computing systems are labeled as exhibiting spatial heterogeneity (Figure 3.3).

System Bus

Figure 3.3: Architecture of a MPMA system

As for SPMA/OS, the essential design requirement for such an operating system is to provide architectural heterogeneity for user-level applications. In other words, the operating system must provide the capability to develop applications which exploit the architectural heterogeneity of the underlying system (e.g. run threads of a given task on different processor architectures depending on their computational requirements).

The first design approach found for SMPA operating systems we labeled as *native and secondary architectures*: a single architecture serves for kernel implementation, while all other architectures are only supported at user-level. This approach doesn't fit well with the execution parallelism of MPMA systems. Translated to MPMA systems, this design approach defines a certain processor (*master processor*) which runs the kernel of the operating system, while all other processors (*client processors*) are supposed to run only user-level binaries. Of course, the interaction between the user-level binaries and the kernel cannot longer be treated through an architectural switch, since it basically requires passing a request from one processor (running the user-level binary) to another processor (running the kernel).

The second design approach suitable for SPMA systems was labeled as *equal opportunities*: there is a different kernel instance per each architectural state. At first sight, this design approach is more suitable for MPMA systems than the previous one as the spatial heterogeneity of the kernel fits with the spatial heterogeneity of the computing system. Therefore, each processor runs its own kernel image and user-level binaries running on top of these kernel instances can simply access the kernel services without the problem of architectural

heterogeneity or the need for an inter-processor communication. The design issues don't stop here as the user-level applications should be able to take advantage of the architectural heterogeneity of the systems. If there is no mechanism for interaction between the kernel instances, the user-level applications will only be mono-architectural, without possibility of solving problems requiring heterogeneous computing. Two solutions providing support for inter-kernel cooperation can be envisaged: a user-level approach and a kernel-level approach. The former approach employs middleware architectures: a user-level layer providing cooperation between heterogeneous applications. A kernel instance can have no or limited knowledge of the existence of other kernel instances. As a consequence, the kernel instances are practically independent one from another and thus they are not required to obey the same design structure. The latter approach requires implementing the inter-kernel cooperation at kernel level. This solution is suitable when the operating system should provide transparency for any architectural state. In addition, this approach is probably more challenging than the former one in terms of kernel design as it requires synchronization and coherency mechanism to achieve cooperation at kernel level.

### 3.4 Design models

The SPMA and MPMA systems show the same design models for the kernel structure. These design approaches could be divided in three classes:

### 1. User-level support for heterogeneity:

Each architectural state has its own kernel instance independent from each other; support for architectural heterogeneity is implemented at userlevel

### 2. Native and secondary architectures:

A single architectural state is considered for the kernel design; support for architectural heterogeneity is implemented at kernel-level

### 3. Equal opportunity

Each architectural state has its own kernel instance, while sharing a global state; support for architectural heterogeneity is implemented at kernel-level

These classes show different approaches in designing a MA/OS. The essential requirement is support for architectural heterogeneity for user-level applications. This requirement could be fulfilled either by taking into account the architectural heterogeneity of the system at kernel level (design 2 and 3) or by implementing this support at user level (design 1). The latter case has a limited influence on the kernel's design. The next sections will elaborate on these design approaches.

### 3.5 User-level support for heterogeneity

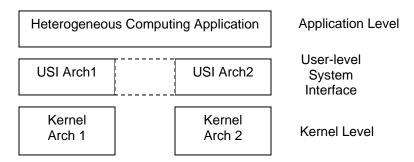

In this design approach, the kernel has no responsibility in offering support for architectural heterogeneity, so any of the classical concepts in singleprocessor operating systems may apply. The support for architectural heterogeneity is left for implementation at user level. This approach applies only to multiprocessor systems (MPMA) where each processor is running its own kernel image. In SPMA systems, due to temporal heterogeneity, the kernel's support is always required for switching the architectural state of the processor and activating another kernel instance. For these systems, support for architectural heterogeneity *exclusively* at user level cannot be achieved.

The user-level support offers the mechanisms to access the services of another kernel instance running on another processor. Each kernel instance has a User-level System Interface (USI) which publishes the interface of the local kernel. The USIs communicate with one another to provide a global system image (Figure 3.4).

Figure 3.4: User-level support for heterogeneity

There is no requirement on having identical design structures for the kernel instances. The only requirement is having each USI exposing a generic system interface accepted by all USIs in the system.

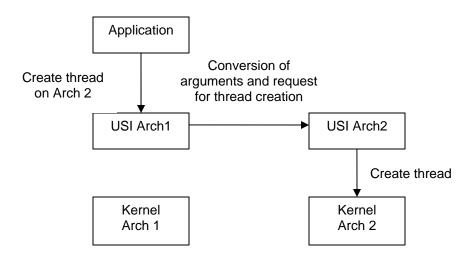

An example of collaboration between USIs is presented in Figure 3.5.

Figure 3.5: Creating a thread on a different architecture

This design approach has the advantage of simplicity: the kernel design is not affected by architectural heterogeneity. There are although limitations introduced by this design concerning the nature of a task itself. Threads of a task should be able to share kernel objects like file descriptors or IPC objects and most important of all, the same virtual address space. As there is no cooperation at kernel level between the kernel instances, threads running on different processors have no possibility to share kernel objects. The only object they are able to share is the physical memory, with mechanisms for synchronization implemented at user level. However, an application may still require coherent (or semi coherent) virtual address spaces across all processors.

### 3.6 Native and Secondary Architectures

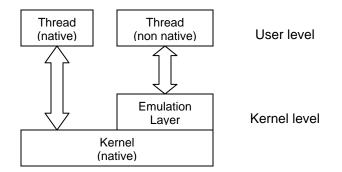

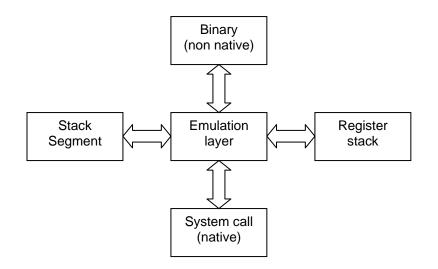

This design approach requires the kernel's support in order to offer architectural heterogeneity for user-level applications. As described earlier, the native architecture is the kernel's architectural state, while all other architectures are labeled as secondary architectures. This design approach has a direct applicability for current processor architectures exhibiting multiple architectural states (e.g. Itanium family). These processors have a native architecture which provides a maximum computing performance and usage of processor resources, while other architectures are supported only for backward compatibility and do not perform as well as the native architecture. For performance reasons, it is therefore preferable to have the kernel built for the native architecture. Moreover, the secondary architectures are used only on temporary basis, so developing a kernel instance for each secondary architecture is not justifiable. This design approach provides a mechanism to couple the user-level need for heterogeneity with the native architecture of the kernel while avoiding the requirement for a kernel instance per each architectural state. This mechanism for supporting a secondary architecture can be labeled as *an emulation layer (*Figure 3.6). The term "emulation" doesn't refer here to instruction set emulation as the processor is capable of executing the instruction set of secondary architectures. Instead, the term "emulation" refers here to *system interface emulation*: each secondary architecture receives a system interface according to own architectural specifications. These system interfaces are not natively supported by the kernel, so they have to be *emulated* based on the kernel's native interface. Basically, this emulation mechanism implements a conversion process between each secondary architectural interface and the kernel's native interface. Due to the intermediary mechanism for accessing the kernel's services, the binaries implemented for the secondary architectures will often suffer a performance overhead compared to binaries for the native architecture.

Figure 3.6: Native and secondary architectures

There are different design criteria which must be taken in consideration when constructing an emulation layer:

- 1. communication protocol between the kernel and user-level binaries: *functional interface* vs. *shared data*

- 1. location at operating system level: *user-level* vs. *kernel-level emulation*

- 2. location in the execution stack of a system call: *top* vs. *bottom design*

These criteria influence both the kernel design and the operating system performance. The kernel design is directly influenced by the location of the emulation layer. On SPMA systems, the emulation layers could be integrated at kernel level. However, this approach doesn't apply to MPMA systems where the parallelism in execution of each architectural state requires parallelism in execution of the emulation layers and the kernel. Basically, each user-level binary running on a different processor should either rely on the kernel (when running on the native architecture) or on an emulation layer (when running on a secondary architecture). Therefore, the MPMA systems accept only user-level emulation layers with a "spatial" decoupling from the kernel. When integrated at kernel level in SPMA systems, an emulation layer may take into consideration another design criterion: whether the native kernel should be aware of the presence of the emulation layer or not. In the former approach, the emulation layer sits on top of the kernel proper and filters communication between userlevel binary and the kernel without the kernel noticing its presence. In the latter approach, the kernel has to acknowledge the presence of the emulation layer and to invoke its mechanisms when communicating with user-level binaries of secondary architectures. Another criterion which may influence the design approach for an emulation layer is whether the communication between userlevel binaries and the emulation layer is synchronous (functional interface) or asynchronous (shared memory). The advantages and disadvantages of these strategies are discussed further in the following section. However, there is no ideal design model for such an emulation layer and the choices for specific strategies are depending on specific design requirements for the operating system.

### 3.6.1 Functional interface vs. Shared data

This criterion refers to the nature of the communication protocol between the user-level binaries and the kernel. The communication protocol depends strictly on the specific system interface according to each architectural state. Even if the kernel provides its own native interface, system interfaces for other architectural states may have different specifications concerning the communication protocol. Commonly speaking, each architectural state should have structurally the same system interface as the native kernel if they rely on the same kernel architecture. However, this might not be always the case and the emulation layer should consider the appropriate communication protocol in relationship with user-level binaries.

Generally speaking, the system interface may either be composed of a *functional interface* (system call interface) or *shared kernel-user data structures*. Each of these communication strategies has its own advantages and disadvantages.

1. **The functional interface** is the most commonly-used strategy for user-kernel communication in kernel design. The functional interface is composed by a collection of system calls. The interface of each system call is defined through a list of parameters to be provided by the user-level binary and a list of result parameters to be returned by the system call function. Both types of parameters could be provided either through the memory stack or the register file. In addition to passing on the system call parameters, the emulation layer must also provide a conversion mechanism between the user's data type representation and the kernel's data type representation. This mechanism must be integrated in the emulation layer since both partners (the user-level binary and the kernel) interact with the system interface according to their own data type representation (Figure 3.7).

The access to arguments passed via memory stack doesn't constitute an issue as the kernel has access to any user-defined virtual address space. The emulation layer simply reads the arguments from their stack location, converts them to the kernel's format and invokes the native system call. For arguments passed via register file, however, the working registers of a secondary architecture may not be the same as the working registers of the native architecture. The solution therefore requires reading the arguments from the original register location, performing the data type conversion of their contents and then writing the arguments to the register locations defined in the native system call interface. This approach allows transparency between the user-level binaries and the kernel, both at data type representation and argument location.

Figure 3.7: Communication over functional interface

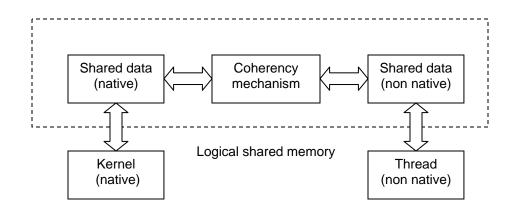

2. The second approach to user-kernel communication is represented by **shared kernel-user data structures**. Even not as common as the functional interface, this communication strategy finds its place in kernels where a faster way to access kernel data structures from the user level is required without blocking its execution (as imposed by a synchronous invocation of a system call). The architectural heterogeneity raises the question concerning the usage of the shared memory. Direct access on shared data requires every binary having the same data representation. Writing shared data according to different data representations destroys the internal coherency. This shared data will eventually make no sense for anyone trying to read it. Two main approaches for implementing shared data is stored according to a generic data representation and both the user-level binary and the kernel access the shared data through an interface which provides data conversion mechanisms. The second approach for

shared data in heterogeneous environments is the usage of replicated data managed by a coherency mechanism. In this approach, the user-level binary accesses its copy of the shared data according to its own data type representation, while the kernel accesses its own copy. The coherency mechanism should assure that the two copies remain identical in terms of information content. *Physical shared data* (access on the *same* memory location) is replaced therefore by *logical shared data* (the *same* data is replicated at different memory locations) (Figure 3.8).

Figure 3.8: Communication over logical shared memory

The question now concerns the location of the coherency mechanism. When located in the emulation layer, data coherency among replicas of shared data can be provided only when the user invokes a system call. This is not always the case: the user may change the shared data without invoking the kernel, while the latter may want to use the shared data. There is no access to coherency mechanism between these two accesses on shared data. so the kernel will access out-of-date information. In addition, the kernel may itself modify the shared data, which makes the user's copy of shared data out-of-date. One solution to this problem is to perform the coherency mechanism whenever the user thread is activated by the scheduler (update the user's replica from the kernel's replica) or whenever the thread is deactivated (update the kernel's replica from the user's replica). While the user thread is deactivated, there is no attempt to modify the user's replica, so the kernel's replica will always have up-to-date information. Moreover, as the user thread is not active, there is no concern if its replica is upto-date. The thread is concerned on having a coherent replica only when it starts to run. Therefore, the coherency mechanism should also be integrated at scheduler level. This approach is probably the only reliable to provide logical shared memory, but it reduces the transparency of the emulation layer in relationship with the kernel: the kernel's scheduler has to be aware of the presence of logical shared memory.

Another issue for implementing logical shared memory concerns the update protocol of replicated copies: *full* or *partial* coherency. The general case is to offer access to the entire content of shared data and thus replicas have to contain the same information. There are alternatives when there is no need for full coherency (e.g. the shared memory is composed of multiple buffers and only of subset of these buffers are required at a certain access on shared data). In such cases, providing full coherency only induces a performance overhead. Therefore, a partial coherency mechanism may be implemented, in which coherency is provided only for those portions of the replicated data required at the moment of the access.

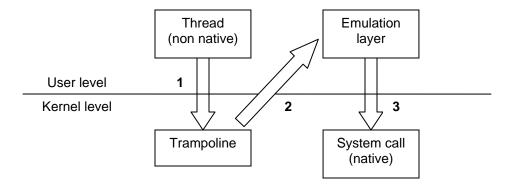

#### 3.6.2 User-level vs. Kernel-level emulation

The emulation layer may be implemented either as a user-level or as a kernel- level layer. In the first approach, the emulation layer is a user-level task. Whenever a user-level binary issues a system call according to a non-native architecture, the kernel reflects the arguments of the system call out from the kernel to the user-level emulation task. The emulation task handles argument conversion according to native interface of the system call and then issues the native system call. This user-level approach for system interface emulation is also known as the *trampoline mechanism* (Figure 3.9) and it has been used extensively by kernels like Windows 2000 (to emulate MS-DOS system calls), the Mach microkernel (to emulate UNIX system calls) [7] and the L4 microkernel (to emulate Linux system calls for L4Linux) [12].

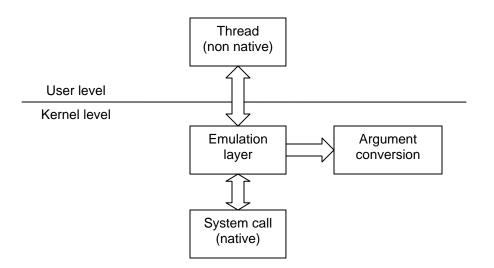

Figure 3.9: The trampoline mechanism

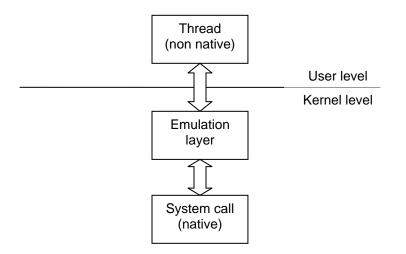

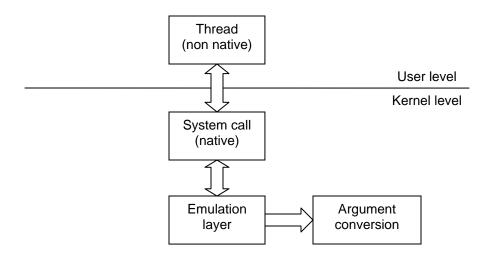

However, the separation of the emulation layer from the kernel is not possible without the kernel's support for implementing a trampoline mechanism. The trampoline mechanism should be able to recognize the architectural state of the system call and to forward the system call arguments to the appropriate userlevel emulation task. A second approach is to integrate the emulation layer in the kernel design (Figure 3.10). The advantage of this approach is the reduced performance overhead in invoking a system call according to a non-native architecture as this approach prevents the overhead of a second kernel entry (in the trampoline mechanism there is a first kernel entry when issuing the non-native system call and a second kernel entry when performing the native system call). However, the user-level emulation has some advantages over the kernel-level emulation in terms of flexibility (user-level emulation provides a more convenient mechanism to add or modify a system call interface of a non-native architecture than the kernel-level emulation) and security (adding more code to the kernel increases the size of the Trusted Computing Base and introduces the likelihood of system fatal bugs) [7].

Figure 3.10: Kernel-level emulation

#### 3.6.3 Top vs. Bottom Design

If deciding to implement the emulation layer at kernel level, the next question which arise is related to the actual location in the execution stack of the native system calls: the emulation layer could either be implemented on top of a system call function (on top of the kernel) or it could be placed at the base of a system call function (on the bottom of the kernel).

In the first approach, the emulation layer is practically transparent to the native system call functions and therefore the system call functions don't require any modifications. The emulation layer handles all argument conversion on top of each native system call function, so that no knowledge about architectural heterogeneity is required at system call level (Figure 3.11).

Figure 3.11: Emulation layer placed on top of the kernel

The second design approach places the emulation layer on the bottom of the system call functions. Arguments are no longer translated to the appropriate data type representation on top of each system call function. Instead, each system call function invokes the appropriate data conversion mechanism provided by the emulation layer (Figure 3.12). Therefore, this approach requires a total integration of the emulation layer in the kernel and practically requires modifying each system call function. This requirement influences not only the invocation of non-native system calls, but also the invocation of native system calls. The performance of native system calls may be affected.

As a guideline, it is preferable to have as much transparency for the emulation layer as possible in order not to alter the performance of the native kernel. On the other hand, providing total transparency of the emulation layer in relationship with the kernel may generate a considerable overhead for the nonnative threads (e.g. may require logical shared data to separate the user's data type representation from the kernel's data type representation). However, the focus of the kernel design should in general be on the performance of the native architecture since most of the binaries are probably intended to use the processor's native architecture. As a rule of thumb, it is desirable that the emulation layer doesn't interact with the normal functioning of the kernel.

Figure 3.12: Emulation layer placed on bottom of the kernel

### 3.7 Equal opportunity

The *equal opportunity* takes a totally different approach from the first two design models of a MA/OS. This approach takes into consideration the architectural heterogeneity within the kernel design itself. In other words, this design approach provides a kernel instance for each architectural state of the system. Advantages of this approach could be expressed in terms of user-level performance: the user-level thread is able to directly access the services of a native kernel without the overhead of either the emulation layer (see section 3.6) or the user-level system interface (see section 3.5). Comparing with the previous design approaches, the task of achieving a global system state is performed at kernel level (Figure 3.13). The question now is how to achieve a global system state. Each kernel instance has its own kernel structures which should be made coherent across all kernel instances. Issues to provide a global system state are related to the inherent distribution of global data structures and the incompatibility between data type representations across different architectural states.

Figure 3.13: Equal opportunity

When user threads are utilizing the kernel services, there is considerable effort to keep a coherent global state, making it likely for the global performance to decrease. Other factors influencing the global performance are the size of the global data structures, the number of kernel accesses modifying these global data structures and the number of kernel instances sharing a global system state.

When designing a kernel which follows the "equal opportunity" model, one should therefore focus on:

- the global data structures

- the coherency mechanism for logical shared data

### 3.7.1 Global data structures

The first criterion influencing the global performance in the *Equal* opportunity design is related to amount of global data structures. Global data structures reflect the global state of the kernel and these data structures directly influence the coherency mechanism. This mechanism enforces data coherency whenever an access on global data structures is required. Different strategies could be provided to assure data coherency, but in all cases the performance of all these mechanisms is highly influenced by the amount of data to keep coherent. Therefore, in order to improve the system's performance one should attempt to minimize the number and size of global data structures. These data structures are often related to kernel's abstractions like threads, address spaces, etc. Minimal kernels like microkernels should have a smaller amount of work in synchronizing global data structures due to the minimalism in choosing the kernel's abstractions.

Generally speaking, a kernel design for a multiprocessor system employs local and shared data structures. The global data structures provide multiple accesses from different locations within the kernel. The concept of shared data has a problem fitting in heterogeneous multiprocessor systems due to incompatibility between data type representations. Two different strategies may be envisaged for implementing shared data in a MA/OS:

- Global data representation (together with data conversion mechanisms for accesses according to other data type representations)

- Multiple data representations (together with a coherency mechanism for implementing logical shared data)

- 1. **Global data representation**: A single data representation is selected. Any data structure with global semantics will be encoded using the global data representation. Whenever there is an access to global data using another data representation, a mechanism is invoked to provide the right data format. This strategy implies direct data access for architectural states having the global data representation, while accesses having other data type representations can access the global data only indirectly, through an interface which provides data conversion. Of course, the interface access induces a performance overhead for any architectural state not having the global data representation. The important question is therefore which data type representation to use as the global one. This choice could be based on different performance criteria: frequency of operations on global data structures with a certain data type representation (e.g. a certain data type representation is dominant), facility of data conversion between a particular data representation and all other available data representations (e.g. a certain data type representation is the extension of all others), etc. After selecting the global data type representation, data conversion mechanisms from the global to all other data representations are required. These mechanisms are embedded in each access interface according to the specific data type representation handled by the interface.

- 2. **Multiple data representations:** This strategy allows direct access to global data using different data type representations. The key element of this solution is replication of data. This replication process requires a suitable coherency mechanism. The data conversion mechanisms between different data type representations will be integrated in the coherency mechanism.

Each data representation strategy has its own advantages and disadvantages, so the choice is strictly based on specific performance criteria. Based on these two strategies for implementing shared data in a MA/OS, each kernel data structure could be associated with one of the following classes:

1. **Exclusive resources**: This class is represented by resources with no global semantics. Exclusive resources are represented by local data structures with no global semantics and by the architectural state (e.g. registers, trap and fault exceptions, software interrupts). These resources

are employed either with local or with architectural scope and thus they have no effect on the global state of the MA/OS.

- 2. **Shared resources**: Resources from this class have shared access from multiple locations within the kernel, either with sequential or parallel access. For sequential access, one must assure that after each access, the shared structures are left in a consistent state. Concerning the parallel access, synchronization mechanisms must prevent concurrent access on the same resource, either by locking resources during access or by serializing accesses on shared resources.

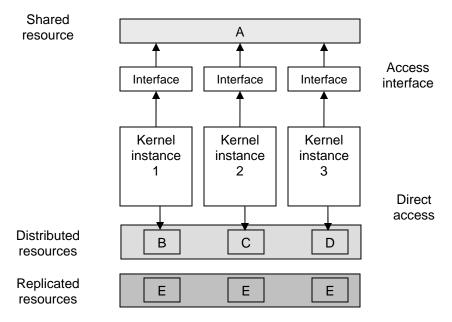

- 3. **Distributed resources:** A distributed resource is a collection of nonidentical resources which may be placed on different locations within the kernel. A coherency mechanism must guarantee that one particular resource is only accessible at one location within the kernel. Examples of distributed resources are global thread identifiers and external interrupts (interrupts provided by a shared APIC<sup>2</sup>). The coherency mechanism must enforce non-replication of these resources.

- 4. **Replicated resources:** A replicated resource is a global resource from which copies are placed in different locations within the kernel. An example of a replicated resource is the replication of a virtual address space among parallel kernel instances. In that case, the page tables of each kernel instance should contain the same information. A coherency mechanism is required to guarantee the integrity of information across all copies of a replicated resource.

The classification above shows which resources are concerned by coherency mechanisms. The exclusive resources don't influence the global system state. Resources with global semantics are represented by the shared, distributed and replicated resources. While the shared resources require only synchronization mechanisms for concurrent access, the distributed and replicated resources require a coherency mechanism (Figure 3.14).

A kernel design may require any of these types of global resources. The amount of the global resources directly influences the performance of the coherency mechanism. Besides the amount of global structures, the amount of updates also influences the performance of the coherency mechanism: achieving data coherency requires keeping track of updates on global data. Different coherency strategies can be envisaged depending on the use case and on the nature of the computing system.

<sup>&</sup>lt;sup>2</sup> Advanced Programmable Interrupt Controller

Figure 3.14: Global data structures

#### 3.7.2 Coherency mechanism

Replicated and distributed data structures along with coherency mechanisms are key issues of a MA/OS. Whether the MA/OS exhibits temporal (SPMA) or spatial (MPMA) heterogeneity, it is often the case that the kernel and/or user-kernel shared structures have to be replicated according to different data type representations. Replication inevitably requires a coherency mechanism as a key requirement of a replication process is to guarantee that replicas reflect the global state of the replicated resource.

A coherency mechanism provides two services:

- 1. Reading a global data structure delivers data which reflects the global state

- 2. Updating a global data structure must leave the data in a coherent state

The design of such a mechanism is mainly base on the following criteria:

- type of global resource: distributed vs. replicated

- location inside the kernel:

- centralized in one location vs. distributed in multiple locations

- update strategy on global resources: *push* vs. *pull protocols*

Resources concerned by coherency mechanisms are either distributed or replicated and they require a different coherency mechanism:

- 1. **Distribution coherency:** This coherency mechanism is related to distributed resources. As a distributed resource is a collection of non-identical atomic resources (e.g. global thread identifiers), the coherency mechanism should ensure that each atomic resource can be used in only one location of the kernel. Using the same atomic resource in multiple locations within the kernel will destroy the integrity of the distributed resource.

- 2. **Replication coherency**: This coherency mechanism has to guarantee that each access on a copy of the replicated resource will issue data which reflects the global state of the replicated resource.

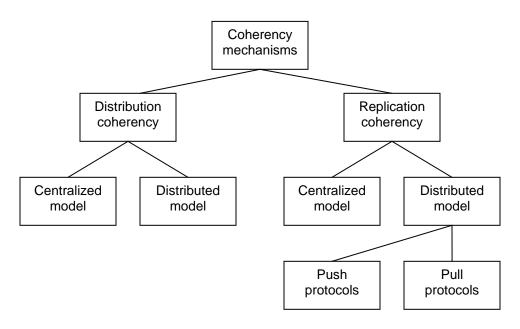

Even if these types of coherency mechanisms have different purposes (distribution and replication coherency), the global architecture of such a mechanism is generally based on two computing models: centralization and distribution. Therefore, architecturally, coherency mechanisms could classify in two main classes:

- 1. **Centralized mechanisms:** A mechanism from this class is centralized in one location of the kernel. Considering the case of multiple kernel instances, the coherency mechanism is handled by a single kernel instance in behalf of all kernel instances. Whenever a global resource needs to be accessed and/or updated, the centralized coherency mechanism is invoked. These mechanisms basically follow the server-client model.

- 2. **Distributed mechanisms:** A mechanism of this class is composed of a collection of sub-mechanisms which are spread in different locations of the kernel and which cooperate to provide a coherent state for the global resource. In the case of multiple kernel instances, each kernel instance may be provided a sub-mechanism as a part of a global coherency mechanism.

Figure 3.15 shows an overview of these two approaches. Each of these approaches has its own advantages and disadvantages. The first approach implements the coherency mechanism in one single location of the kernel and thus avoids replication of code at multiple locations. The disadvantage of this approach is due to centralization itself: the centralized location could become a bottleneck if the number of accesses on global data managed by this coherency mechanism is relatively high. The second approach solves this problem as multiple locations of the kernel can accept requests for performing global coherency. On the other hand, this approach shows also a disadvantage due to distribution itself: the sub-mechanisms have to cooperate to provide global coherency. This communication induces a performance overhead in providing global coherency. In conclusion, the choice between these two architectures depends on many performance criteria like the amount of accesses on global data or the overhead of communication intra-kernel.

Figure 3.15: Architecture of coherency mechanisms

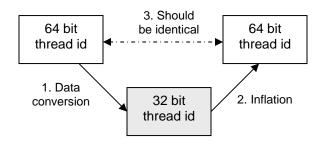

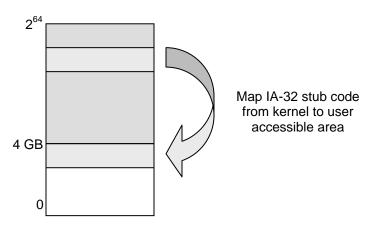

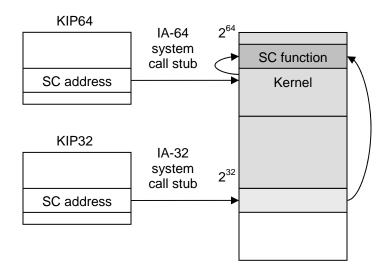

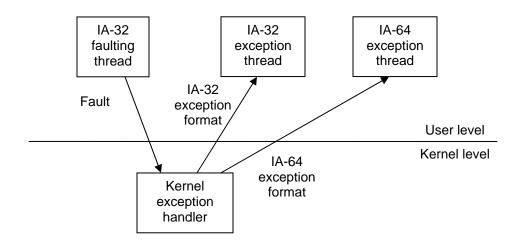

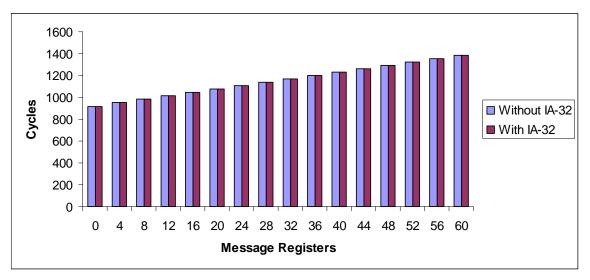

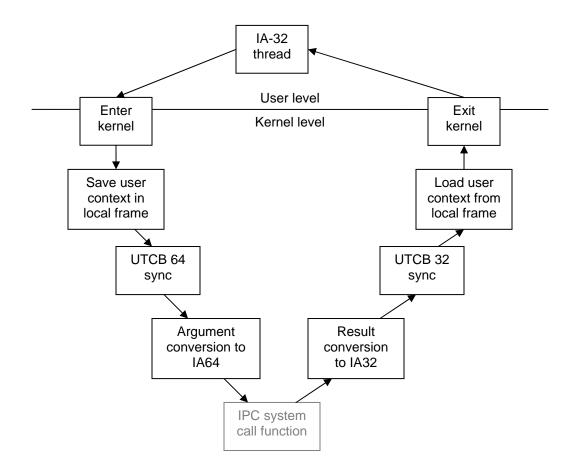

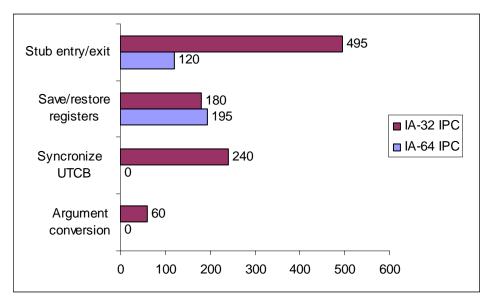

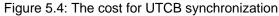

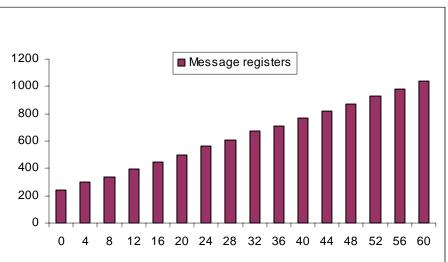

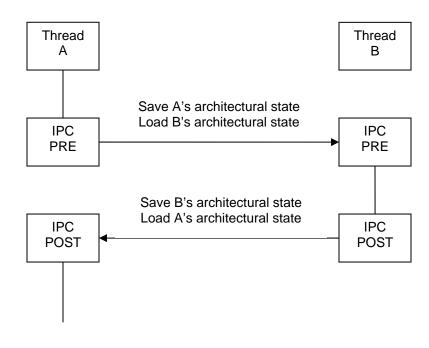

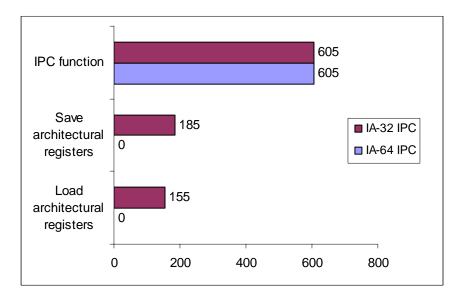

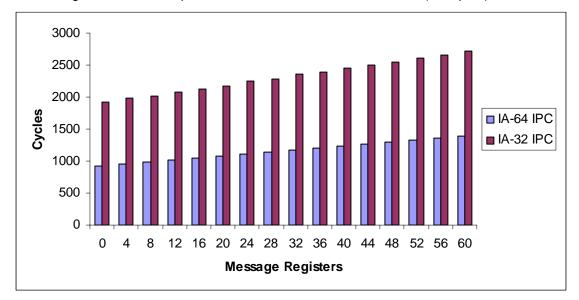

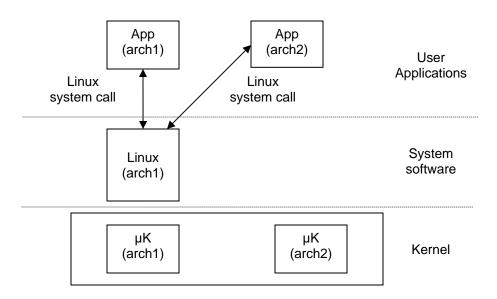

The distributed mechanism to achieve data coherency introduces another design element: the level of coherency, either full or lazy. When full coherency is required, a sub-mechanism propagates an update on the global resource to all sub-mechanisms, in order to keep coherent data at each instant of time. In the second approach, lazy coherency, updates are propagated "only when" they are required. A distributed resource accepts only full coherency as it imposes the non-replication of its atomic resources at each instant of time. On the other hand, the requirement for a replicated resource is being able at the moment of the access to obtain coherent information, although without any requirement whether all replicas contain identical information at the any instant of time. Based on these data coherency models, two families of update strategies could be envisaged: