# **Pre-Virtualization Compiler Enhancements**

Raphael Neider

Diplomarbeit

Verantwortlicher Betreuer: Prof. Dr. Frank Bellosa Betreuender Mitarbeiter: Dipl.-Inf. Jan Stöss

31.01.2006

Hiermit erkläre ich, die vorliegende Arbeit selbstständig verfasst und keine anderen als die angegebenen Literaturhilfsmittel verwendet zu haben.

I hereby declare that this thesis is a work of my own, and that only cited sources have been used.

Karlsruhe, den 31.01.2006

Raphael Neider

#### Abstract

One problem common to all virtualization techniques is the efficient injection of emulation code into the guest operating systems (guest OSs). Emulation is needed to limit the effects of *virtualization sensitive instructions* to the appropriate virtual machine. For instance, privilege mode changes, processor halting or resetting, and device accesses must be redirected to the executing *virtual* machine rather than affect the underlying *physical* machine, as the latter is probably shared among multiple virtual machines. The emulation code will—in many cases—overwrite the contents of general purpose registers that would remain unmodified by the emulated sensitive instruction. These additional sideeffects must carefully be hidden from the guest OS to guarantee its correct execution.

The pre-virtualization approach uses a load-time rewriter to replace sensitive instructions with a sequence of code that saves all caller-saved registers, calls appropriate emulation code, and restores the saved registers afterwards. In many cases, this approach unnecessarily saves many registers whose content is afterwards discarded, thus increasing the virtualization overhead.

In this thesis we propose to use additional context-information for each sensitive instruction to facilitate generating more efficient replacement code: *Live registers* enable us to identify and discard irrelevant registers instead of preserving them across the emulation. Furthermore, literally known register content can help in statically selecting more specific emulation code, especially for device I/O. We also propose to use static rewriting techniques, such as register reallocation and rescheduling, to reduce the number of live caller-saved registers at the sensitive instructions.

All presented techniques will be integrated into an advanced rewriting system, which automatically extracts the required information from the pre-virtualized guest OS binary, performs the supporting static rewriting, and implements efficient load-time rewriting routines.

Our implementation for IA-32 shows that the use of context-information reduces the number of preserved registers during the emulation of sensitive instructions by more than 40 % for current Linux kernels.

<u>ii</u>\_\_\_\_\_

# Contents

| 1 | Intr | duction                                               | 1 |

|---|------|-------------------------------------------------------|---|

|   | 1.1  | The Problem: Missing Context-Information              | 2 |

|   | 1.2  | Approach                                              | 3 |

|   | 1.3  | Structure of This Thesis                              | 4 |

| 2 | Bac  | ground And Related Work                               | 5 |

|   | 2.1  | Virtualization                                        | 5 |

|   |      | 2.1.1 Terminology                                     | 6 |

|   |      | 2.1.2 Simulation and Interpretation                   | 6 |

|   |      | 2.1.3 Pure Virtualization                             | 7 |

|   |      | 2.1.4 Para-Virtualization                             | 7 |

|   |      | 2.1.5 Pre-Virtualization                              | 8 |

|   | 2.2  | Binary Rewriting 10                                   | 0 |

| 3 | Proj | osed Solution 13                                      | 3 |

|   | 3.1  | Terminology                                           | 3 |

|   | 3.2  | Optimizations for Individual Patches                  | 4 |

|   |      | 3.2.1 Discarding Irrelevant Registers                 | 4 |

|   |      | 3.2.2 Reducing the Overhead of Callee-Saved Registers | 6 |

|   |      | 3.2.3 Statically Evaluating Dispatch Tables           | 9 |

|   | 3.3  | Optimizations for Successive Patches                  | 0 |

|   |      | 3.3.1 Deferring Register Restoration                  | 0 |

|   |      | 3.3.2 Rescheduling the Instruction Stream             | 2 |

|   |      | 3.3.3 Compacting Basic Blocks                         | 2 |

|   | 3.4  | Context-Aware Rewriting System                        | 3 |

|   |      | 3.4.1 Goals of Our Design $\ldots 2^4$                | 4 |

|   |      | 3.4.2 System Structure                                | 5 |

|   |      | 3.4.3 Sources of Context-Information                  | 6 |

|   |      | 3.4.4 Analysis Component                              | 7 |

|   |      | 3.4.5 Rewriter Component                              | 8 |

|   |      |                                                       | _ |

| 4 Implementation |            | lementation 29                                     |

|------------------|------------|----------------------------------------------------|

|                  | 4.1        | Rewriter Component                                 |

|                  |            | 4.1.1 General Approach                             |

|                  |            | 4.1.2 Efficient Handling of Caller-Saved Registers |

|                  |            | 4.1.3 Static Dispatch                              |

|                  |            | 4.1.4 Deferred Register Restoration                |

|                  |            | 4.1.5 Compaction of Basic Blocks                   |

|                  | 4.2        | Glue Code Generators                               |

|                  |            | 4.2.1 Specification Language for Glue Code         |

|                  |            | 4.2.2 Generated Glue Code                          |

|                  |            | 4.2.3 Locally Modified Calling-Conventions         |

|                  | 4.3        | Analysis Component                                 |

|                  |            | 4.3.1 Overview                                     |

|                  |            | 4.3.2 Code Discovery                               |

|                  |            | 4.3.3 Disassembly                                  |

|                  |            | 4.3.4 CFG Reconstruction                           |

|                  |            | 4.3.5 Data-Flow Analysis                           |

|                  |            | 4.3.6 Static Rewriter                              |

| 5                | Eval       | uation 53                                          |

|                  | 5.1        | Test Environment   53                              |

|                  | 5.2        | Microbenchmarks                                    |

|                  |            | 5.2.1 General Virtualization Code                  |

|                  |            | 5.2.2 Unused Scratch Space                         |

|                  | 5.3        | Applicability                                      |

|                  | 5.4        | Minibenchmarks                                     |

|                  |            | 5.4.1 Latency Tests                                |

|                  |            | 5.4.2 Bandwidth Tests                              |

|                  | 5.5        | Execution Profiles                                 |

| 6                | Con        | clusion 67                                         |

|                  |            | Summary                                            |

|                  | 6.2        | Open Issues                                        |

|                  | 6.3        | Outlook         68                                 |

| A                | Eve        | mples of IA-32 Glue Code 69                        |

|                  | A.1        | Original Calling Conventions                       |

|                  | A.1<br>A.2 | Efficient Calling Conventions Using Stubs          |

|                  | A.2        | Inlined Stubs                                      |

|                  | 1 1.0      |                                                    |

# Chapter 1

# Introduction

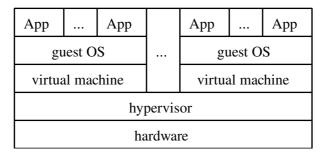

Virtualization technology enables the concurrent execution of multiple operating systems (OSs) on a single physical machine. To safely isolate the operating systems from each other, virtualization environments confine their guest OSs in virtual machines and control their execution with virtual machine monitors (VMMs). Virtual machines can be hosted on general purpose operating systems or on specialized *hypervisors*, which provide services such as physical memory management and scheduling for their clients. The basic structure of a hypervisor-based system is outlined in Figure 1.1.

Most of the instructions of the virtual machines are passed through to the physical machine for direct execution. Some instructions, however, access the hardware in a way that might affect other concurrently running virtual machines or even break the control of the VMM over the guest OS. The effects of these *sensitive instructions* must therefore be redirected to software-emulated or virtualized hardware [27], which is usually provided by the VMM or the hypervisor. The approaches to discovering sensitive instructions and redirecting their effects vary between virtualization techniques.

One approach is to use *pre-virtualization*: In a preparation phase the sensitive instructions in the guest OS binary are first padded to provide scratch space for emulation code and then annotated to ease the process of finding them during later rewriting. While loading the guest OS into a virtual machine, a rewriter replaces all sensitive instructions with appropriate emulation code or a call to an emulation routine in the VMM or the hypervisor.

Care must be taken not to expose side-effects of the emulation to the guest OS. This is important, because the emulation code is executed on the same processor and in the same context as the guest OS, which implies shared registers between guest OS and emulation code. If the content of a register is still required after the sensitive instruction (respectively its emulation) has been executed, the rewriter must guarantee that the emulation does not overwrite this particular register. If the rewriter cannot guarantee this, it must save and restore the content of the register as part of the emulation.

Figure 1.1: Structure of a virtualization environment. The operating systems and their applications are executed and confined in virtual machines. The virtual machines can access critical system hardware only via the hypervisor, which also provides physical memory management and basic scheduling for its client virtual machines. (system structure adopted from [1])

## **1.1 The Problem: Missing Context-Information**

For convenience, the emulation routines provided by the VMM are usually compiled from a high-level programming language, such as C or C++. Thus we have only limited influence on the registers that are used and modified, but can rely on the calling-conventions of the compiler. These include a logical split of the register set into caller-saved and callee-saved registers: The *callee-saved* registers are guaranteed to retain their value during execution of the called subroutine; if the callee wants to access them anyway, it has to restore their original value before returning to the caller. For *caller-saved* registers, no such guarantee is made: the callee is free to modify them at will.

During replacement of the sensitive instructions, previous rewriters do not possess any information about which of the caller-saved registers are actually modified by the called emulation routine. Additionally, they do not "know", which of these registers actually need to retain their contents because they are read later on by the guest OS. Currently, the rewriter conservatively approximates the missing information according to worst-case assumptions:

- all registers are modified by the called emulation routine

- all registers contain values that are accessed again afterwards

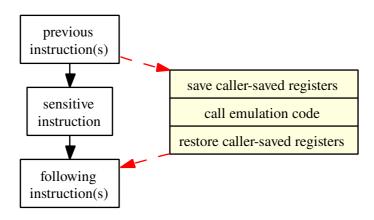

As a consequence, the rewriter replaces each sensitive instruction with a code sequence that first stores *all* caller-saved registers (in memory), then calls the desired emulation routine, and finally restores the previously saved registers. We depict this approach in Figure 1.2.

Our analysis (Section 5.3) shows that, in about 75 % of all cases, not all callee-saved registers need to be saved, because only a subset of them is actually used later on. For each

Figure 1.2: Virtualized sensitive instruction. The rewriter substitutes sensitive instructions with virtualization code; the latter often includes a call to an appropriate emulation routine. Calling conventions allow the called function to modify caller-saved registers. The virtualization code must hide these modifications from the guest OS unless the registers are not read afterwards. Solid edges represent the original control-flow, dashed edges represent the control-flow after the sensitive instruction has been replaced with the virtualization code (right box).

unused register the current approach wastes two instructions<sup>1</sup> and two memory accesses. Estimating a mean number of 50 executed instructions per emulation, each unnecessarily preserved register adds 4 % to the overall virtualization overhead, which we want to avoid.

# **1.2** Approach

To improve the rewritten code, we deliver information about the contexts of each individual sensitive instruction to the rewriter. Based on this information, an enhanced rewriter then generates custom-tailored code that only saves the relevant registers. Additional context-information can be used to statically select more specific emulation code instead of having a dynamic dispatcher select it at runtime, and thus reduce the number of costly control-flow operations.

We develop a system that automatically computes all required information solely based on the pre-virtualized guest OS binary. Together with an enhanced rewriter, this system facilitates efficient rewriting at load time. We verify the effectiveness of our proposals with an implementation for the common IA-32 systems. Measurements on a Pentium 4 reveal that the overall system performance is hardly affected by our optimizations,

<sup>&</sup>lt;sup>1</sup>Two instructions are needed to either push and pop the register on and off a stack or to store it to a dedicated memory location and load it from there afterwards. For architectures without push and pop instructions, even more code might be needed to update the stack pointer if no dedicated memory can be used—for example in multi-processor systems.

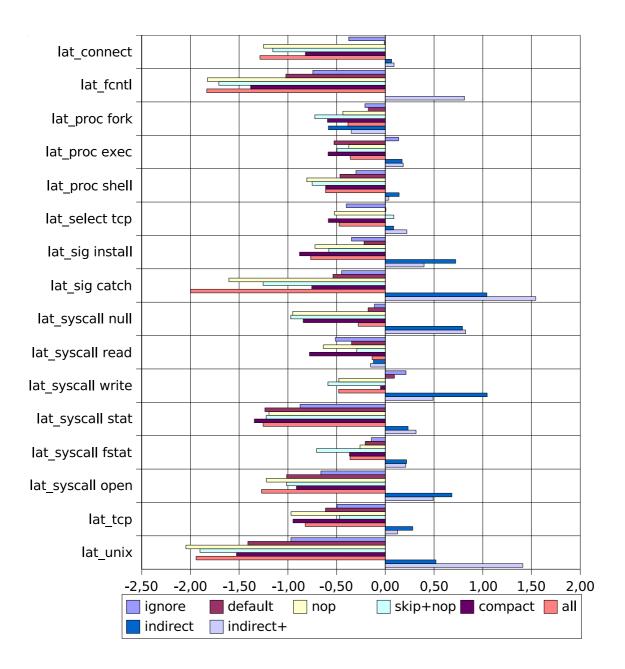

although more than 40 % of the previously preserved caller-saved registers are discarded. Most of the benchmarks we conducted on a pre-virtualized Linux show insignificant improvements of round about 0.5 % due to our optimizations.

### **1.3** Structure of This Thesis

The remainder of this thesis is structured as follows:

Chapter 2 relates this work to previous research in the fields of virtualization techniques and binary rewriting. We point out differences between previous work and our system and show how this work is influenced by formerly published results. In Chapter 3 we present our ideas on improving the load-time rewriting process with contextinformation. All developed techniques will finally be integrated into an enhanced rewriting system, which automatically extracts the required context-information from the guest OS and makes use of it in a context-aware rewriter. Chapter 4 provides details on our implementation of both the enhanced rewriter and the analysis of IA-32 guest OS binaries, which obtains the context-information to support the rewriter. In Chapter 5 we prove the effectiveness of the proposed techniques with microbenchmarks and their applicability in a pre-virtualized Linux kernel with figures we obtained during rewriting. In this chapter we also present benchmark results that compare the original and our optimized approach to rewriting. Chapter 6 summarizes and concludes this thesis and hints at possible future work based on our results.

# Chapter 2

# **Background And Related Work**

In this chapter we provide background information on three current approaches to virtualize IA-32 systems. We will then present related work from the research field of binary rewriting.

## 2.1 Virtualization

The basic idea of virtualization is to enable the concurrent execution of multiple operating systems on a single physical hardware platform while providing strong isolation of these guest operating systems. This is similar in spirit to multi-tasking operating systems, which allow for the concurrent execution of multiple user-level applications on a single instance of an operating system. Virtualization is, however, conceptually located one layer below such systems. Where multi-tasking operating systems can define and expose a software API that can be tailored to address the problems of multi-programming, virtualization is bound by the underlying hardware architecture, which is externally defined and rather fixed.

Further problems arise from the nature of the guest operating systems: For one, these expect to execute in the most privileged processor mode. Secondly, they are designed to exert direct control over the hardware but not to share it with concurrently executing operating systems. In a virtual machine, the guests are deprivileged and restricted to accessing the provided virtual hardware in order to reliably control them and to guarantee strong isolation of the concurrently running guests. As a consequence, instructions that rely on the above assumptions must be intercepted and emulated; however, the major part of the instructions of the guests will be executed natively on the underlying physical machine.

#### 2.1.1 Terminology

In this thesis we will use the following terms with respect to virtualization: The virtualization environment provides a set of *virtual machines* (VMs), which are software controlled abstractions of the underlying physical machine. We call the software that implements the virtual machines a *virtual machine monitor* (VMM). A *hypervisor*<sup>1</sup> multiplexes the hardware among the virtual machines—that is, the hypervisor provides management of resources such as memory or processor time for the virtual machines. The general structure of such a virtualization environment is shown in Figure 1.1, page 2.

In order to successfully contain the *guest operating system* in its virtual machine, we must prevent (*virtualization*) sensitive instructions from affecting the shared hardware. Instead of executing these instructions natively, we must therefore replace them with VMM-specific emulation code that applies the effects to the proper virtual machine. Sensitive instructions comprise instructions that change the processor's mode of execution—for example change the current privilege level, enter system management mode, halt or reset the processor—or access the now possibly shared devices via port I/O. In addition to sensitive instructions, we also need to intercept sensitive memory operations [14], which read or modify hardware-accessed data structures, such as page-tables or interrupt descriptor tables, or trigger memory mapped I/O.

During execution of a guest OS in a virtual machine, the effects of all the sensitive instructions and sensitive memory operations must be redirected to the executing virtual machine rather than be applied to the physical machine. For this purpose, the VMM provides *emulation code*, which is executed instead of the original sensitive instruction. Because the emulation code is usually executed on the same processor that also runs the guest OS, all side-effects of the emulation on the machine state, especially its registers, must be hidden from the guest OS. We shall refer to *any* code that is substituted for a sensitive instruction as *virtualization code*; typically, virtualization code prepares the execution of emulation code and cleans up afterwards in order to hide the emulation from the guest OS.

The remainder of this section gives an overview of different approaches to virtualization together with a summary of their particular strengths and weaknesses.

#### 2.1.2 Simulation and Interpretation

Whole-system simulators, such as QEMU [2], bochs [12], or Virtual PC [17], emulate not only virtualization sensitive instructions but the complete instruction set. This enables the execution of guest operating systems that are designed and implemented for hardware architectures different from the one that executes the simulator. Such a flexibility is paid

<sup>&</sup>lt;sup>1</sup> For the purpose of this thesis, it does not matter whether the virtual machines are hosted on a complete operating system or on a hypervisor. We therefore restrict our discussion to the second approach.

for with an enormous emulation overhead at runtime; we consider the latter to be too high for efficient virtualization.

A similar albeit much more efficient and less general approach to abstracting from the physical hardware has gained popularity with Sun's Java [15] and Microsoft's more recent .NET technology [5]. Both systems provide a runtime environment for the execution of just-in-time compiled byte-code. The runtime is commonly referred to as a virtual machine, which is conceptually an interpreter for the respective byte-code.

Neither technique is suitable for virtualization of IA-32 systems, because these virtual machines do not reflect the IA-32 hardware interface but implement a new "architecture". We know of no efforts to port a current operating system from IA-32 to either Java or .NET. However, the byte-code approach could be adopted to convey detailed information about the contexts of sensitive instructions to the load-time rewriter in our system.

#### 2.1.3 Pure Virtualization

Virtual machines as provided by VMware [25] execute on top of a common desktop operating system such as GNU/Linux or Windows. Non-sensitive instructions are passed through to and executed unmodified by the underlying hardware, whereas sensitive instructions are detected and emulated using *binary translation* [21]: In this process the guest OS is automatically ported to a new architecture, which mostly resembles the original IA-32, but lacks the sensitive instructions. All sensitive instructions in the guest OS are implicitly translated to emulation code for the provided virtual machine. As the emulation code is automatically injected into the guest OS, nearly all operating systems can run unmodified in the provided virtual machines. Only the virtual machine monitor (VMM) must occasionally be improved to correctly handle new instructions and hardware features.

On the downside, this approach implies considerable overhead: For one, the larger part of the emulation is performed not within the guest's protection domain, but in a kernel module in the host OS. This necessitates frequent and costly privilege level changes for the emulation of sensitive instructions. Secondly, memory sensitive operations must not only be emulated, but also be detected at runtime. For this purpose, the translator inserts *guard instructions* before every memory access in order to discover references to sensitive data structures such as page-tables or interrupt descriptor tables. As an alternative, the hardware memory management mechanisms segmentation and paging can be utilized to intercept such accesses via segmentation violation or page fault exceptions. Both approaches introduce significant overhead.

#### 2.1.4 Para-Virtualization

The para-virtualization technique [26], which is implemented for example in the Xen hypervisor [1] or L4Linux [7], abandons the need to detect and insert emulation code for

sensitive instructions at runtime. Instead, this approach provides a high-level, functioncall based interface to its emulation routines, which enables virtualization with a very low overhead for two reasons: First, the virtual machine monitor (VMM) is *collocated* with the guest OS—that is, VMM and the guest OS reside in the same address space. Therefore, execution of emulation code often does not require privilege level or even address space changes but only a simple function call. The high-level interface allows to reduce the number of privilege level changes even further by batching several calls to the hypervisor and having all of them handled upon the next unavoidable entry into the hypervisor. Second, the virtualization code is generated by the optimizing compiler that is used to build the guest OS; thus its integration into the guest is automatically optimized as well (as opposed to pre-virtualization, for which this thesis strives to provide optimized virtualization code).

To make use of the new interface, a potential guest operating system must first be ported to this new "architecture" before it can be loaded into the virtual machine. During porting, all sensitive instructions must be removed from the source code of the guest operating system and be replaced with calls to their respective emulation routines in the VMM. Besides source code access, porting an operating system requires intimate knowledge of the ported OS and leads to high engineering cost both for the initial porting and the later maintenance of the guest OS.

Despite its good performance, we believe that the long-term engineering effort, which is caused by porting and maintaining specialized guest OS versions, is too high to make para-virtualization practical on the long run. Our approach will enable the use of optimizing compiler techniques for the generation of virtualization code and thus help to close the performance gap between para- and pre-virtualization—the latter of which we will introduce now.

#### 2.1.5 Pre-Virtualization

Pre-virtualization was developed both to overcome the high engineering cost of paravirtualization while keeping up its efficiency and to enable the binary to execute on a variety of hypervisors—or even on raw hardware.

In [14], LeVasseur and colleagues state that, although still minor changes to the guest OS are necessary, the engineering effort is an order of magnitude lower than for plain para-virtualization. The authors report that they can automatically prepare the guest OS for virtualization by using assembler macros to detect, annotate, and pad sensitive instructions for later rewriting. This preparation is integrated into the build process of the guest OS and therefore requires source code access. The resulting binary still obeys the hardware interface; consequently it can be executed on bare hardware and on pure virtualization systems. Additionally, pre-virtualization–aware hypervisors can efficiently instantiate a virtualized version that is targeted for themselves using load-time rewriting: While the guest OS is loaded into the virtual machine, the rewriter uses the provided an-

#### 2.1. Virtualization

notations to easily find and replace the sensitive instructions with inlined emulation code or calls to emulation routines in the collocated VMM. The rewriting process solely relies on information from the binary and does no longer require access to the source code of the guest OS. Consequently, OS vendors need to maintain only a single pre-virtualized binary distribution of their operating systems, which can than efficiently be executed on the targeted hardware as well as in a variety of virtualization environments. The source code of the OS need not be published.

Compared with pure virtualization, the injection of virtualization or emulation code is considerably simplified, because the preparation step provides enough scratch space to hold the injected code. Consequently, no instructions need to be relocated as no code is added to and inserted into the guest OS, so that global rewriting or translation to adjust the references is not required.

In the current design, the mapping from sensitive instruction to virtualization code is fairly static: All occurrences of a sensitive instruction are replaced with identical copies of virtualization code—except for adjustments to the operands to match the original sensitive instruction. This results in inefficient code being emitted for sensitive instructions that are virtualized by calling emulation routines in the VMM, because the rewriter must make sure to preserve all caller-saved registers: Each register *might* need to be preserved at some call-site, although at most call-sites only a subset of the caller-saved registers actually needs to be preserved.

An approach similar to pre-virtualization was presented by Eiraku and colleagues in [6] to run BSD systems as Linux applications. They propose to use an assembler preprocessor to automatically replace the sensitive instructions with their respective virtualization code. As the binary is statically rewritten, this approach tightly couples guest operating system and the targeted "hypervisor", quite similar to para-virtualization. No details about the assembler preprocessor are published, so we assume that it is a mere macro expander. As a consequence, this approach could as well benefit from the results of this thesis by using are more powerful, context-aware preprocessor.

#### Analysis

The presented virtualization techniques all exhibit the classic cost vs. efficiency tradeoff: While simulation and pure virtualization are cheap in terms of guest OS preparation cost, they imply a considerable runtime overhead. Para-virtualization reduces the runtime overhead of virtualization at the cost of a tremendous engineering effort for preparing the guest OS. The pre-virtualization approach sacrifices some of the performance of paravirtualization its simple rewriter, but greatly reduces engineering cost again. We believe that we can close the performance gap between pre- and para-virtualization with an improved rewriter without reintroducing any additional engineering effort. For this purpose, we will provide context-information for the sensitive instructions to the rewriter and generate more efficient virtualization code, which respects the specific context of the currently rewritten instruction.

## 2.2 Binary Rewriting

The use of context-information, such as live registers, for efficient code generation is common practice in modern compilers [18]. Furthermore, computing this information via data-flow analysis on binaries has also been proposed before and is implemented in a variety of tools. However, we are not aware of any system that implements the analysis and the rewriter in separate tools, as we will do. Most available approaches also rely on additional meta-data, such as debugging symbols or relocation records, to help them in locating code and data in the binaries. Our system will use such information if available, but also work just fine without it.

Binary instrumentation, implemented in tools like ATOM [22] or FIT [4], is similar in spirit to the pre-virtualization load-time rewriting: Both approaches inject foreign code into a readily compiled program without disturbing its execution besides timing behaviour. ATOM and FIT already use live register information to efficiently hide the side-effects of the injected code from the instrumented program. The current load-time rewriter lacks this information and consequently emits inefficient code.

More general binary rewriting tools, such as the Executable Editing Library EEL [11], grant even more access to the code of completely linked binaries. For this purpose, these tools extract a control-flow graph (CFG) representation of the binary and allow to insert or remove instructions on this graph. The modified program can afterwards be emitted as a runnable executable. EEL even provides static program analysis, including live registers, and would therefore be a good starting point for the task of this thesis. Unfortunately, EEL is only available for SPARC-like RISC architectures. As virtualization is primarily interesting for the common CISC IA-32, which introduces many problems like variable instruction lengths that are not addressed by EEL, neither the library itself nor the implemented algorithms can easily be adopted for our purposes.

However, similar tools exist for IA-32: DIABLO [24] is a link-time rewriter, which is available for IA-32 and several other architectures. Being a link-time rewriter, DIABLO does not operate on the completely linked binary but takes the relocatable object files as input. This precludes its use on pre-virtualized guest OS binaries without source-code access. Furthermore, the applicability of this system to operating system kernels is unknown, as it was developed to rewrite user-level applications.

#### Analysis

Several tools for efficient rewriting of IA-32 binaries exist, but all of these are intended to *statically* rewrite the binaries. To facilitate the insertion of foreign code, the tools must precisely identify code and data, so that they can correctly adjust references to the

following, relocated code. As code and data are inherently indistinguishable in IA-32 binaries, all present tools require additional information about the structure of the binary and therefore operate on relocatable object files. These provide the required information in terms of relocation records.

In this thesis, however, we want to rewrite pre-virtualized guest OS binaries without relying on additional information. This is possible, because we do not rewrite the code globally, but apply only local modifications to replace sensitive instructions. Consequently, we do not need to globally update address references, which relieves us from the burden of having to precisely identify code and data. We only need to find all code fragments, so that the contexts of the sensitive instructions can correctly be determined. For the actual computation of the context-information, we can use a number of standard data-flow analysis [19], which are also implemented in the previously presented tools.

# Chapter 3

# **Proposed Solution**

In this chapter we will present an enhanced rewriting system for pre-virtualized operating systems on IA-32. First we propose techniques that overcome the inefficiencies of previous rewriters by considering additional information about the contexts of sensitive instructions during their rewriting. Afterwards, we present approaches to amortize some of the virtualization overhead across successive rewritten instructions. The proposed optimizations reduce the number of instructions that are substituted for the sensitive instructions. Our final contribution shall therefore enable us to efficiently skip the unused space.

As the presented optimizations require detailed information about the contexts of the rewritten instructions, we shall conclude this chapter with a presentation of our analysis tool. This tool extracts the required information from the guest OS binary to support the enhanced rewriter, which implements the above techniques. The rewriter and the analysis tool together make up our enhanced rewriting system.

## 3.1 Terminology

Throughout the remainder of this work we will use the following terms to refer to welldefined objects: To keep the virtual machines isolated from each other, we must redirect the effects of sensitive instructions in a guest operating system (guest OS) to its assigned virtual machine. The *emulation code*, which implements this functionality, comes in two guises: For most instructions, the virtual machine monitor (VMM) provides appropriate emulation code in terms of compiler-generated subroutines (external emulation). For simple but frequently executed instructions, the rewriter inlines the emulation code into the guest OS (inlined emulation).

Especially for external emulation, we often require additional code to (a) compute arguments for the emulation, (b) hide side-effects of the emulation from the guest OS, (c) implement the call of the emulation routine, and (d) clean up the argument stack afterwards. We use the term *virtualization code* to refer to these code fragments. Again,

virtualization code can either be completely inlined or (partially) be deferred to helper routines. We call the latter *stubs*, as they abstract from the details of the actual call similar to stubs in remote procedure calls [3].

To simplify the injection of inlined emulation or virtualization code into the guest OS, we prepare the latter during assembly: A set of assembler macros pads each sensitive instruction with an instruction-dependent number of semantically neutral nops to provide *scratch space*. The rewriter can use this space in addition to the space previously occupied by the original sensitive instruction to store the generated code. We subsume the sensitive instruction and its dedicated scratch space in a *patch*. More global optimizations not only consider the current patch, but also the surrounding *basic block*, which is a straight-line sequence of instructions without jumps or jump targets in between. Only the last instruction in a basic block may be a branching instruction.

## **3.2** Optimizations for Individual Patches

Previous rewriters with static virtualization code must save and restore all registers that might be modified by the emulation code at every rewritten instruction, because their contents might still be needed after some of these instructions. Our observation is, however, that in most cases only a subset of the registers is in fact relevant for the subsequent execution of the guest OS. We therefore propose to dynamically generate the virtualization code according to the context of the currently rewritten instruction. During rewriting, the irrelevant registers can then safely be discarded, if the rewriter can distinguish relevant from irrelevant registers.

### 3.2.1 Discarding Irrelevant Registers

We shall now present a formal approach to computing the minimal set of registers, whose contents must be preserved across the emulation of a sensitive instruction i. To avoid confusion, we will subsequently use *instruction* to refer to a particular instance of an instruction—that is, a single occurrence of its encoding in the examined binary—and not to all instructions with the same opcode or type.

#### **Relevant Registers**

We call a register *relevant* at the instruction i if its content from before the execution of i is possibly read afterwards. Intuitively, the set of all relevant registers is the minimal set of registers that must retain their original value after the execution of the virtualization code for i.

To formalize this definition, let Assigns(i) denote the set of registers that are potentially modified during the non-virtualized execution of *i*. Let us further refer to the set of live registers<sup>1</sup> immediately *after* the execution of *i* as LiveAfter(i). We then define

$$Relevant(i) := LiveAfter(i) \setminus Assigns(i).$$

(3.1)

The set Relevant(i) is in fact the earlier mentioned set of *relevant registers at i*:

- " $\subseteq$ ": Let  $r \in Relevant(i)$  be a register. From Equation 3.1 follows that  $r \in LiveAfter(i)$ and  $r \notin Assigns(i)$ . From the definition of live registers we can conclude that r is accessed after i has been executed; furthermore, the content of r is not changed by the execution of i, as  $r \notin Assigns(i)$ . Consequently, r's content from before the execution of i is accessed afterwards—r is a *relevant register* at i.

- " $\supseteq$ ": To make r a relevant register, its value prior to the execution of i must be accessed after i's execution. In other words: r is live after i has been executed and r is not modified during the execution of i. This implies  $r \in LiveAfter(i)$  and  $r \notin Assigns(i)$ , thus  $r \in LiveAfter(i) \setminus Assigns(i)$  and finally  $r \in Relevant(i)$ .  $\Box$

#### **Saved Registers**

Not all relevant registers need to be preserved across the emulation (let us refer to the code that is used to emulate i as Emulate(i)): We can safely ignore registers that are known to remain untouched by the emulation code. As we provide this code, we can also provide the set of registers that are potentially modified during its execution; let Assigns(Emulate(i)) denote this set.<sup>2</sup> As a consequence, we need to save and restore all registers r with

$$r \in Relevant(i) \cap Assigns(Emulate(i)).$$

All other registers can safely be discarded.

If the emulation code is provided as a compiler-generated subroutine in the VMM which is the common case—, the task of preserving register contents is partially deferred to the emulation code due to compiler-enforced calling conventions: For subroutine calls the register set of the processor is logically split into caller-saved and callee-saved registers. *Caller-saved* registers may be left modified by the called subroutine; the caller has to save and restore them if their contents is still needed. The usually larger part of the register set is *callee-saved*; the called subroutine must guarantee that the contents of callee-saved registers appears to be unchanged by its execution.

<sup>&</sup>lt;sup>1</sup> A register is commonly considered to be *live* if its current value is *potentially* read by one of the following instructions.

<sup>&</sup>lt;sup>2</sup> For the sake of readability, we implicitly extend our functions from the domain of single instructions to the domain of sets of instructions in the natural way: For arbitrary code *c*—represented as a set of instructions—we define  $Assigns(c) := \bigcup Assigns(i)$ .

Consequently, the minimal set Saved(i) of registers that need to be saved and restored by the generated virtualization code is given as

$Saved(i) := Relevant(i) \cap Assigns(Emulate(i)) \cap Callersaved.$

### 3.2.2 Reducing the Overhead of Callee-Saved Registers

In the previous section we have defined the set Saved(i) to help in generating efficient code for caller-saved registers. However, the callee-saved registers are still saved unnecessarily if they are not relevant at the call-site: The subroutine must work correctly in all contexts, so that the compiler approximates the combined *Relevant* set of all call-sites with the set of all registers. With s denoting the set of instructions that make up the subroutine, this results in the generation of code to save and restore

$\{all registers\} \cap Assigns(s) \cap Calleesaved = Assigns(s) \cap Calleesaved,$

although for each call, only the subset that is relevant at the current call-site c effectively needs to be preserved:

$$Relevant(c) \cap Assigns(s) \cap Callees aved$$

We will now present three approaches to counter the negative effects of unnecessarily preserved callee-saved registers on overall virtualization performance.

#### Storing Caller-Saved Registers in Callee-Saved Registers

Our first approach is to preserve relevant caller-saved registers not in memory but in irrelevant callee-saved registers. This effectively makes some irrelevant callee-saved registers relevant, because their values are used after returning from the emulation routine to restore the originally relevant caller-saved registers. Furthermore, less registers are saved in memory, which reduces the number of memory accesses in favour of register-to-register copies. Additionally, the presented approach reduces the stack footprint of the emulation, which might improve cache effectiveness and therefore indirectly increase overall performance. We depict this technique in Figure 3.1.

The main advantage of this approach is its general applicability: Whenever calleesaved registers are considered irrelevant while at least one relevant caller-saved register exists, we can save two memory accesses—storing and restoring the caller-saved register—by preserving the relevant caller-saved in the irrelevant callee-saved register.

On the downside, this approach does not reduce the number of instructions that are necessary for saving the register state. Its direct effect on the virtualization runtime is therefore rather negligible.

| (a) original virtualization code | (b) improved virtualization code |

|----------------------------------|----------------------------------|

| pushl %eax                       | movl %eax,%esi                   |

| pushl %ecx                       | movl %ecx,%edi                   |

| pushl %edx                       | pushl %edx                       |

| call emulation                   | call emulation                   |

| popl %edx                        | popl %edx                        |

| popl %ecx                        | movl %edi,%ecx                   |

| popl %eax                        | movl %esi,%eax                   |

Figure 3.1: Caller-saved registers preserved in callee-saved registers. Relevant caller-saved registers can be protected from modification by the callee by moving them into irrelevant callee-saved registers before the call and restoring them from there afterwards. In this example we assume %EAX, %ECX and %EDX to be relevant caller-saved registers, whereas %ESI and %EDI are assumed to be irrelevant callee-saved registers.

#### Locally Adjusting the Calling Conventions

Our second approach to reducing adverse effects of callee-saved registers is to completely banish them from emulation code and make all registers caller-saved instead. As discussed earlier in this section, we can handle caller-saved registers efficiently, so that this approach effectively reduces the overhead that was previously incurred by unnecessarily preserving irrelevant callee-saved registers.

We propose to modify the calling conventions that apply to our emulation routines, so that *for these functions*, all registers are considered caller-saved and none callee-saved. We are free in the choice of calling conventions for our emulation routines, because they are never directly called from within compiler-generated code that relies on the original conventions. Emulation routines are exclusively called from a rewritten guest OS, so we only need to adapt the injected virtualization code to pure caller-saved calling conventions. No modifications to the guest OS are necessary.

We must, however, not ignore the implications on the size of the virtualization code: Previously, the code that is needed to save and restore the originally callee-saved registers was present only once in the prologue and the epilogue of the emulation function. In the worst case, we now have to replicate this code at each call-site, thus increasing the total code size. An increased code size generally reduces the effectiveness of the (trace-)caches and consequently degrades the overall system performance.

The pre-virtualization approach limits this effect by providing only a small scratch space for the rewriter, thus tightly bounding the size of the virtualization code. But this raises a new problem: What shall we do if the provided scratch space is not sufficient to save all relevant registers? Enlarging the scratch space is not possible if we have no access to the source code of the guest OS. Moreover, a larger scratch space would negatively

affect the performance of the guest even if it is executed natively due to increased cache pollution.

The only obvious solution to this problem is to call the emulation routines indirectly via stubs and to delegate the task of preserving the relevant registers there. With N registers to consider, we either need to statically provide  $2^N$  stubs per emulation routine to efficiently handle all combinations of relevant and irrelevant registers, or we need to generate the required stubs dynamically during rewriting. In the worst case, even the dynamic approach requires the complete set of stubs.

In addition to the implied cost of indirectly calling the emulation routine, this approach—when applied for many emulation routines—dramatically enlarges the code size of the VMM and therefore considerably increases the risk for TLB misses during emulation. For IA-32, we need to handle N = 7 general purpose registers (%ESP must always be restored by the callee), which results in 128 stubs per emulation routine. Assuming a realistic mean stub size of 16 bytes and 4 kByte pages, only 2 sets of stubs fit into one page, so that we require round about 13 pages only for the stubs of the 25 emulation routines present in the current VMM. Furthermore, most of the 128 stubs will reside in a different cache line than the emulation routine, whereas in the single stub case, stub and emulation can easily be partially collocated in one line. Consequently, the new approach often requires one additional cache line for each called emulation routine as compared with the original approach, which also increases the risk for memory stalls due to cache misses.

Concluding, we state that modified calling conventions can in fact be used to our benefit, but only if the according emulation routines have few call-sites and only if these provide enough rewriting space, so that we do not need the stubs. We apply these conventions only to instructions that explicitly require preserving all registers as part of their emulation; for IA-32, these instructions are cpuid and iret. Here the pure caller-saved conventions imply no additional cost, as all registers are preserved by the caller anyway, but prevent the callee from preserving these registers again.

#### **Reallocating Registers**

Our third approach to making callee-saved registers relevant at sensitive instructions uses *register reallocation*.

Instead of copying relevant caller-saved registers to irrelevant callee-saved registers at runtime as proposed in the first approach, we now try to reallocate a relevant caller-saved register r to a callee-saved register s throughout the whole lifetime of r (see Figure 3.2). If such an s is available, we can replace all references to r with s, beginning at the previous assignment to r up to and including the last use of the assigned value.

The result of this technique is that the reallocated caller-saved register r is no longer relevant at the sensitive instruction, so that the virtualization code needs to save less registers. On the other hand, the now relevant callee-saved register s implies no additional

| original code                    | reallocated registers            |

|----------------------------------|----------------------------------|

| movl (%ecx),%edx                 | movl (%ecx),%edi                 |

| pushl %edx                       |                                  |

| call emulation                   | call emulation                   |

| popl %edx                        |                                  |

| <pre>movl (%eax,%edx),%edx</pre> | <pre>movl (%eax,%edi),%edx</pre> |

Figure 3.2: Effects of register reallocation. By reallocating live values from caller-saved to calleesaved registers, we can reduce the number of preserved registers. In this example we assume that %EDX is caller-saved and not used in the emulation. Furthermore, we assume that %EDI is an irrelevant callee-saved register.

cost, because the callee preserves its content anyway.

Register reallocation is superior to the first approach with respect to efficiency, because it reduces not only the number of memory accesses, but also the number of executed instructions: Reallocation completely removes both the save and the restore instructions for now irrelevant caller-saved registers.

This advantage is paid for with a reduced applicability: Caller-saved registers often cannot be reallocated, because they are used as *implicit* or *fixed* operands: On IA-32, mul %eax implicitly assigns to %EDX, whereas the in and out instructions for port I/O require their operands in parts of %EAX and %EDX. In both cases, the registers cannot be replaced with different ones. Another problem arises from registers, whose lifetimes extend into multiple basic blocks with disjoint sets of available callee-saved registers. For these cases, register reallocation is hard if not impossible without introducing additional register-to-register copy instructions. The latter would reduce or even negate the intended reduction of runtime and must therefore be avoided. The first technique, however, can easily be applied even in these cases.

#### **3.2.3** Statically Evaluating Dispatch Tables

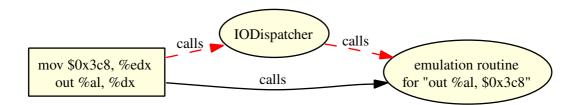

Some sensitive instructions, especially those related to device I/O, require different emulation code depending on the current value of one of their operands. For example, the emulation of IA-32's out instruction first retrieves the addressed port from %EDX to determine the accessed device. Then it selects and calls the appropriate emulation routine of the according virtual device. We term the first called emulation routine a *dispatcher*, as it only dispatches emulation requests to more specific handlers.

Occasionally, the value of the deciding operand is a previously assigned literal or can otherwise be determined statically. In these cases, we can replace the call of the dispatcher with a direct call of the more specific emulation routine. This allows us to remove one unnecessary control-flow indirection (a call/return pair) at runtime, which is depicted

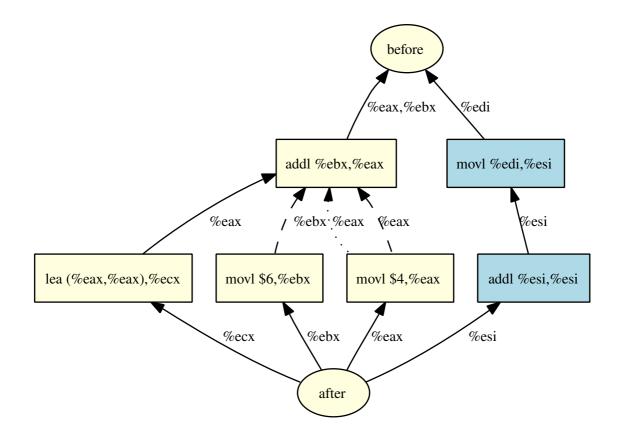

Figure 3.3: Static dispatch. Some sensitive instructions require different emulation code based on operand values. If their values are statically known, we can rewrite the sensitive instruction to directly call the specific emulation routine and bypass the otherwise needed dispatcher.

in Figure 3.3.

A similar approach is also applicable to memory mapped I/O, although the device addresses are not fixed, but rather assigned dynamically at system boot-up with page-size granularity (*plug'n'play*). The device registers are always located at constant offsets in the assigned memory region, and these offsets can be inferred from static program analysis. Together with the accessed device, which is available from the annotation for the sensitive memory operation, we have all the information that is required to statically select the appropriate emulation routine.

## **3.3** Optimizations for Successive Patches

The previously discussed techniques are limited to locally affect code generation for a single sensitive instruction, only register reallocation also modifies the surrounding code. These approaches deny possible synergistic effects that can result from generating code for more than one sensitive instruction. In the following sections we shall provide approaches that improve code quality at a more global scope.

#### 3.3.1 Deferring Register Restoration

If two sensitive instructions are separated only by instructions that do not access relevant caller-saved registers, it is likely that the relevant registers at the first instruction are also relevant at the second one<sup>3</sup>. In this case we need not restore the saved registers after the first sensitive instruction, but can defer their restoration until after the second one. Furthermore, we need not save the registers again before the second sensitive instruction,

<sup>&</sup>lt;sup>3</sup>The only exception occurs when the second sensitive instruction itself accesses the previously relevant registers. In all other cases, we know that the contents of the relevant registers prior to the first sensitive instruction are used after its execution; otherwise the registers would not be considered relevant. As neither the code in between the two sensitive instructions nor the second sensitive instruction accesses these registers, we conclude that they are still relevant at (and unchanged after) the second sensitive instruction.

| original virtualization | deferred register restoration |

|-------------------------|-------------------------------|

| pushl %eax              | pushl %eax                    |

| pushl %edx              | pushl %edx                    |

| call emulation1         | call emulation1               |

| popl %edx               | popl %edx                     |

| popl %eax               |                               |

|                         |                               |

| pushl %eax              |                               |

| pushl %edx              | pushl %edx                    |

| call emulation2         | call emulation2               |

| popl %edx               | popl %edx                     |

| popl %eax               | popl %eax                     |

Figure 3.4: Deferred register restoration. By considering the virtualization code of two consecutive sensitive instructions, we can remove unnecessary restore/save pairs in between. For this example, %EDX is assumed to be accessed between the two patches, whereas %EAX is not used until after the second patch.

because they are still saved. Thus we amortize the preservation overhead across two successive emulations; by applying the same technique iteratively, we can occasionally defer the restoration even further. The effects of a single application are shown in Figure 3.4; %EAX is effectively preserved across two sensitive instructions at the cost of preserving it across only one.

We must take special care if the stack pointer is used by one of or in between the two sensitive instructions: As we usually preserve registers by pushing them onto the stack, the stack pointer has a different value than expected by the guest OS code. If the stack pointer is used as part of an address expression, we are in some cases able to adjust a specified offset to skip the additional values on the stack. In cases where such an adjustment is not possible, we cannot use this technique.

Despite the complex preconditions, this technique is often applicable especially in conjunction with device I/O: A first sensitive instruction issues a command, such as *read disk block*, whereas a second sensitive instruction provides additional data, reads the result or checks the status of the device. Another common scenario involves devices that only expose an address register and a data register. For such devices, each access first selects the desired internal device register by writing its index to the address register. The desired data is afterwards read from or written to the data register using a second sensitive instructions are present in between the two device accesses.

| original code     | rescheduled code  |

|-------------------|-------------------|

| movl \$0x3c4,%edx | pushf             |

| movl \$0x80,%al   | movl \$0x3c4,%edx |

| pushf             | movl \$0x80,%al   |

| • • •             | • • •             |

| out %al,%dx       | out %al,%dx       |

Figure 3.5: Rescheduling. By reordering the instructions, we can reduce the number of live registers at sensitive instructions. In the original code, both %EAX and %EDX are live across the execution of the sensitive instruction pushf, whereas in the rescheduled code, both are irrelevant.

#### **3.3.2** Rescheduling the Instruction Stream

During scheduling of the instructions, the compiler that is used to build the guest OS is not aware of sensitive instructions; especially, it does not perceive that the respective emulation code requires additional registers. Consequently, the compiler does not try to reduce the number of caller-saved registers that are live *across* such a sensitive instruction.

As we do know about sensitive instructions and the possible need for further available registers, we can reallocate registers in order to free up caller-saved registers as discussed in Section 3.2.2, and we can reorder the instructions, so that less caller-saved registers are live across sensitive instructions. We give an example for the latter approach in Figure 3.5: In the original code, %EDX and %AL are live during execution of the sensitive pushf instruction. The rescheduled code frees up both registers for use by the appropriate emulation code.

A second goal of rescheduling is to cluster sensitive instructions, so that the previously discussed deferred register restoration technique (Section 3.3.1) can be applied to reduce the virtualization overhead. For this purpose we need to either move two sensitive instructions as close to each other as possible or, equivalently, move non-sensitive instructions that are embraced by two sensitive instructions before the first or after the second sensitive instruction.

### 3.3.3 Compacting Basic Blocks

Most of the previously discussed optimizations, both for single and successive patches, reduce the number of instructions that make up the virtualization code. As the rewriter cannot change the size of the scratch space that is provided for the current sensitive instruction, the space that was previously occupied by unnecessary instructions must now be filled with innocuous instructions. Executing the latter costs additional cycles at runtime and thus reduces the effects of the presented optimizations.

We therefore propose to compact the basic blocks that contain sensitive instructions,

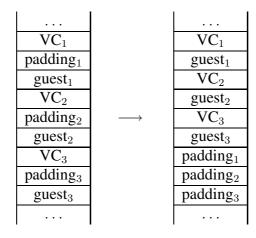

Figure 3.6: Basic block compaction. By moving unused scratch space to the end of the containing basic block we can more efficiently skip over it.  $VC_i$  denotes the virtualization code, padding<sub>i</sub> represents the unused space in the same patch and guest<sub>i</sub> symbolizes the interleaving code from the guest OS. The basic block ends after guest<sub>3</sub>.

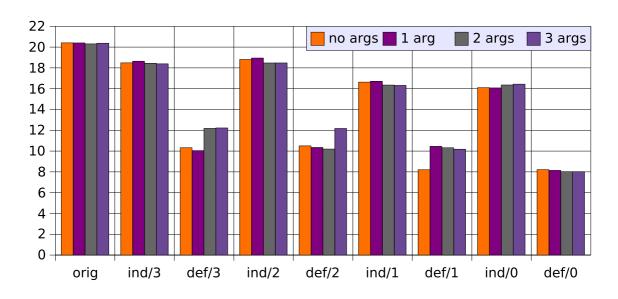

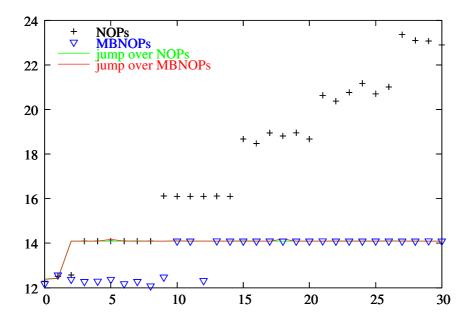

after the virtualization code has been generated. In this process we propagate all unused space to the end of the basic block, where we can then implement efficient ways to skip it either by emitting a jump over the unused space, or by filling it with multi-byte nops as proposed in [8]. By collecting all unused scratch space, we only need to skip one large block instead of multiple small ones, which significantly increases the effectiveness of the multi-byte nop approach.

The end of the basic block is an ideal place for the unused scratch space: By keeping the space in its original block we avoid to move labels, which would require a global adjustment of all references. In the presence of indirect jumps, such an adjustment is not even possible. Furthermore, many basic blocks end in branching instructions. For unconditional branches, the presented approach completely removes the overhead of skipping over the unused space, as it has been moved to after the branch and out of the critical path. Similarly, taken conditional branches skip the unused code for free. Additional instructions to skip the unused space are therefore only required on the fall-through path of conditional branches and for basic blocks that do not end with a branching instruction. Figure 3.6 provides a visualization of basic block compaction.

## 3.4 Context-Aware Rewriting System

In the previous two sections, we proposed techniques that help to generate efficient virtualization code for sensitive instructions. Most of the discussed techniques require information such as live registers about the contexts of the sensitive instructions. In this section we shall present the design of a system that incorporates both an analysis component, which computes the necessary context-information, and a context-aware rewriter to implement the presented techniques.

## 3.4.1 Goals of Our Design

Our system is intended to enhance the pre-virtualization approach, so we do not want to trade in the primary goals and achievements of the latter for the improvements that are offered by our system. We therefore state the following goals for the context-aware rewriting system:

### **Reduced Runtime Overhead**

The basic goal of our system is to effectively reduce the runtime overhead that is caused by replacing sensitive instructions in a guest operating system with *inefficient* calls to emulation routines.

#### **Fully Automated Improvement**

As stated in [14], pre-virtualization reduces the engineering effort of para-virtualization by "orders of magnitude" while maintaining nearly the same performance. Our system shall close the performance gap between pre- and para-virtualization without reintroducing significant engineering effort.

#### **Hypervisor-Independent Enhancements**

Pre-virtualized guest OS binaries adhere to the targeted platform API; they can be executed on bare hardware as well as in pure virtualization environments and even on all hypervisors with support for pre-virtualization. Our system shall not hinder this flexibility, but offer its improvements to all pre-virtualization–aware hypervisors and avoid to degrade the performance of the natively executed guest OS.

#### **Efficient Rewriter**

The rewriter must replace sensitive instructions with appropriate, efficient virtualization code. As this task has to be carried out whenever a guest OS is loaded into a virtual machine, we want to keep the rewriter fast.

#### **General Applicability**

We want to be independent of access to the source code of the guest OS to the largest possible extent. We can then efficiently virtualize even commercial guest operating systems

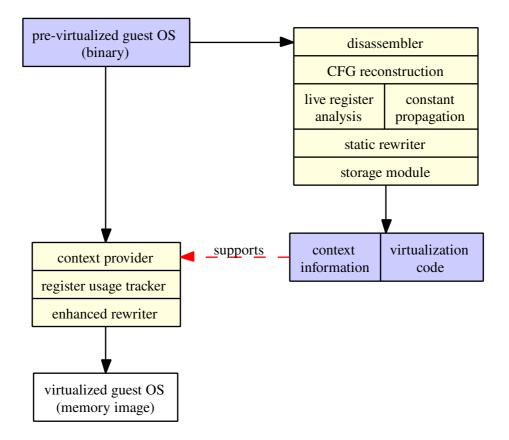

Figure 3.7: Structure of the proposed system. In an analysis phase (top-right box), we augment the pre-virtualized guest OS binary with context-information on all sensitive instructions. At load-time, the optimizing rewriter replaces the sensitive instructions in the memory image of the guest OS with dynamically generated, efficient virtualization code based on the results of the analysis.

that are delivered as pre-virtualized binaries but without source code.

### 3.4.2 System Structure

In order to keep the rewriter fast and simple, we propose to split the rewriting system into two components (Figure 3.7): An *analysis component* extracts the desired context-information from the guest OS binary and appends the analysis results. This is useful, because the information is solely dependent on the binary and does not change over time. Computing it once suffices and saves time during rewriting, as the information will instantly be accessible.

A *rewriter component* implements the previously discussed techniques to replace sensitive instructions with efficient virtualization code while a guest OS is loaded into a

virtual machine. The rewriter dynamically generates the virtualization code based on the type of the rewritten instruction and on the context-information that is provided by the analysis component.

### 3.4.3 Sources of Context-Information

We have evaluated several sources for the required context-information, but found most of them to be insufficient or impractical.

**Compiler-Internal Data** While building the guest OS binary, the compiler already computes some of the information we need for our enhanced rewriting techniques: Both live registers and propagated constants, which we require to determine the relevant registers and to support the static dispatcher respectively, are also used during code generation. Unfortunately, the information is only available for compiler-generated code. As the machine-specific sensitive instructions have no counterpart in modern high-level languages such as C or C++, they are inserted using inline assembly or even plain assembler source files. In both cases, the compiler does not analyze the code and therefore does not directly deliver the desired information.

**Assembly Code** Our second option is to analyze the generated and hand-written assembly code, where all instructions are clearly identified as such and are easily parseable. Furthermore, symbolic labels and references explicitly convey the control-flow relations between instructions; we can even identify jump tables in the code. Still we opted against analyzing the assembly code for two reasons: First, access to the assembly code is equivalent to access to the guest OS source code, which we want to avoid in order to also support closed-source guest OSs. Second, the individual assembly source files only allow file-local analysis. In order to acquire precise information about live registers at return instructions, we need to perform whole-program analysis, which considers register usage information from all call-sites. As an alternative to whole-program analysis, we could augment the compiler to emit information about the registers that are used to return values to the callers for each function, but that would still require access to the source code.

**Object Files** The assembled object files no longer provide easily parseable instructions or explicit, symbolic control-flow relations within the files. As they require source code access similar to the assembly code but only provide less information, we also opted against using the object files as our source of context-information.

**Binary** The pre-virtualized guest OS binary is the only source of information, that is always available. To our benefit it contains all of the guest OS code, except for loadable kernel modules, so that we can use whole-program analysis to obtain precise information.

On the downside, the binary contains the instructions in their machine encoding; we first need to disassemble them to extract useful information. Furthermore, the labels that mark control-flow targets are no longer accessible but must be inferred from other sources, such as disassembled instructions or debugging symbols. Lastly, instructions and data cannot be distinguished in the binary, which complicates the analysis.

**Decision** Despite the indicated problems, we opted to obtain the desired contextinformation solely from analysis of the guest OS binary, as this is the only source of information that is always available and does not require access to the source code of the guest OS.

#### 3.4.4 Analysis Component

The analysis component provides context-information on all sensitive instructions to prevent the rewriter from having to recompute this information over and over whenever the guest OS is loaded. We have identified several types of information that can be used during rewriting and can be precomputed in the analysis component: The rewriter requires information on live registers to identify and discard irrelevant registers and uses literally known register contents (alias propagated constants) in static dispatching. Furthermore, we inform the rewriter about the registers, whose restoration can be deferred until after the next patch because they are not used in between. In order to support an efficient implementation of basic block compaction, we deliver the addresses and sizes of basic blocks to the rewriter. We also provide the locations of addresses, that are evaluated at runtime relative to the current instruction pointer: As block compaction includes code motion, we need to adjust these addresses whenever the associated instruction has been moved.

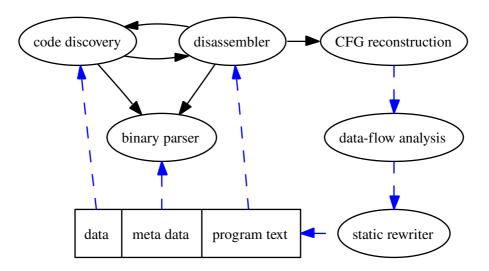

We use standard data-flow analysis to compute live registers and statically known register contents (via constant propagation). The remaining information can easily be obtained once the necessary data structures are present: Data-flow analysis require a control-flow graph (CFG) representation of the analyzed code, along with additional data-flow annotations. We construct such a CFG from the results of a disassembler. During disassembly we extract the control- and data-flow relations for the instructions and store this information in abstract instructions. We then combine the latter according to their control-flow relations to make up the CFG, on which we perform all further analysis.

We also move the more complex rewriting techniques, namely register reallocation and rescheduling, into the analysis component. The results of this static rewriter are appended to the binary together with updated context-information for the rewritten blocks. To use the virtualization-friendly code, the load-time rewriter must patch both the guest OS and the context-information; alternatively it may completely ignore the information from the static rewriter. This approach is compatible with all hypervisors and does not influence native execution of the binary, so that we do not lose generality by implementing static rewriting early. We only reduce the complexity of the rewriter and speed up the rewriting process.

### 3.4.5 Rewriter Component

We split the load-time rewriter into three modules: The first one, the *context provider*, encapsulates the acquisition and retrieval of context-information. Although we propose to precompute this information and store it in the binary, this module can as well be implemented to compute the information on demand. The *register usage tracker* provides an abstract interface to the code generation routines that are affected by our optimizations. Most importantly, this module provides abstract register save/restore operations that use the context-information to implement the desired operation efficiently: irrelevant registers are silently discarded, whereas relevant registers are preserved in callee-saved registers if possible or on the stack. The third module provides the basic code generation and rewriting mechanisms. This module also integrates the rewriter component into the surrounding virtualization environment.

# Chapter 4

# Implementation

To demonstrate our approach, we implemented a context-aware rewriter and an analysis tool for IA-32 systems. The implementation of the rewriter is based on the Afterburner project [13], which is developed at the University of Karlsruhe. We reused the provided infrastructure and rewriting mechanisms to implement our enhancements. For the analysis tool, no such foundation was available, so that we implemented it from scratch.

In the following sections, we will first present how we implemented the proposed optimizations in the load-time rewriter. Afterwards, we will sketch the implementation of our analysis tool.

# 4.1 Rewriter Component

The Afterburner project provides a complete pre-virtualization framework: It includes assembler macros to automatically annotate and pad the sensitive instructions while the guest OS is built, the required emulation routines, and a rudimentary load-time rewriter. We reused the complete system, including the rewriting mechanisms, and integrated our optimizations.

We implemented the relevant techniques for efficient handling of caller-saved registers in abstract save\_registers and restore\_registers routines. Together with data-structures for the necessary bookkeeping, these routines make up a separate module, the register usage tracker. We integrated static dispatching into the code generation for both port I/O and memory mapped I/O. Furthermore, we also implemented deferred register restoration and compaction of basic blocks. As the latter optimizations require information about the structure of the generated code, we apply both of them in an additional pass over the patches after all code has been generated.

We begin the detailed discussion of the rewriter with a description of our approach to generating virtualization code and present the implementation of the optimizations afterwards.

## 4.1.1 General Approach

When a guest OS is loaded into the virtual machine, we use the pre-virtualization annotations to iterate over all sensitive instructions and replace them with appropriate emulation or virtualization code. The annotations provide neither the type nor the operands of the instructions, so we first disassemble the instructions to obtain this information. For inline emulated instructions such as cli, we then emit the hand-crafted emulation code (usually a single instruction) and continue with the next sensitive instruction.

For externally emulated instructions, more work needs to be done: If the current instruction references an operand in memory, we must first compute its effective address, so that we can pass it on to the emulation routine. We store this address temporarily in %EAX, but only after we have preserved its original value on the stack. We encapsulated the code generation for calls to emulation routines in a dedicated function, which generates the required code to preserve caller-saved registers, to pass arguments to the emulation routine, and to call it.

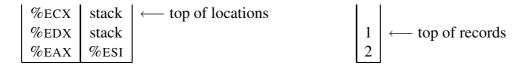

This function takes a descriptor for the requested emulation routine and an array of (type, value) pairs for each argument that is to be passed to the emulation routine. type can be either register or immediate, and value represents the according register number or literal value of the operand. Based on this information, we generate virtualization code as shown in Figure 4.1: First, we save the caller-saved registers %EAX, %ECX and %EDX, unless the descriptor for the emulation routine indicates that they are expected as *implicit* arguments. In the latter case, the registers are not saved, but pushed onto the stack as additional arguments to the emulation routine. We distinguish between *save* and *push* operations, because the former may be discarded for irrelevant registers or implemented as a register-to-register copy, see Section 4.1.2. A push operation always pushes its argument onto the stack.

Having handled the caller-saved registers, we then push the explicit arguments in reverse order onto the stack according to the usual C calling conventions and call the emulation routine. The remaining code cleans up the stack and restores all previously saved or pushed registers.

We will now show, how we implemented our optimizations for efficiently handling caller-saved registers in the save and restore operations.

### 4.1.2 Efficient Handling of Caller-Saved Registers

While generating virtualization code, we need to emit code to save and restore registers. The original rewriter directly generated appropriate push and pop instructions. We instead delegate the code generation to more abstract save and restore routines. These use the available context-information to transparently discard irrelevant registers by simply not emitting any code, to preserve relevant ones in unused callee-saved registers as proposed in Sections 3.2f, or to push them onto the stack. For convenience, the

```

default virtualization code