# Stage-aware Scheduling in a Library OS

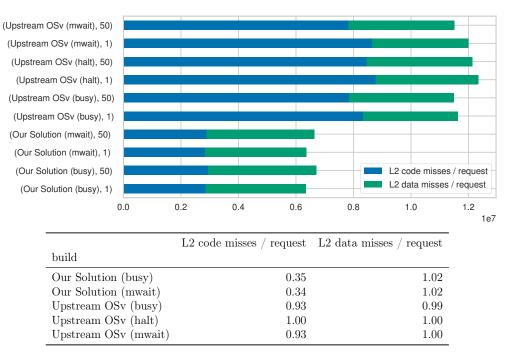

Bachelorarbeit von

# cand. inform. Christian Schwarz

an der Fakultät für Informatik

Erstgutachter: Zweitgutachter: Betreuender Mitarbeiter: Prof. Dr. Frank Bellosa Prof. Dr. Wolfgang Karl M. Sc. Mathias Gottschlag

Bearbeitungszeit: 01. Dezember 2017 – 27. März 2018

Karlsruhe, den 27. März 2018

Ich versichere wahrheitsgemäß, die Arbeit selbstständig verfasst, alle benutzten Hilfsmittel vollständig und genau angegeben und alles kenntlich gemacht zu haben, was aus Arbeiten anderer unverändert oder mit Abänderungen entnommen wurde sowie die Satzung des KIT zur Sicherung guter wissenschaftlicher Praxis in der jeweils gültigen Fassung beachtet zu haben.

iv

## Abstract

Scalable high-performance network servers are a requirement in today's distributed infrastructure. Event-driven concurrency models often provide better scalability properties than multi-threaded servers but many legacy applications still follow the multi-threaded model where each request is handled by a dedicated operating system thread. Recent profiling at Google suggests that the instruction working set of many server applications does not fit into the private i-caches of contemporary processors, causing underutilization of their super-scalar out-of-order pipeline. In a multi-threaded server with an oversized instruction working set, context switches between two request-handler threads are thus likely to cause i-cache misses and subsequent pipeline stalls.

We start by analyzing existing approaches to optimize the cache behavior of network servers. One technique applicable to multi-core systems is executing different parts of an application's code on different cores. By migrating threads to those cores whose caches contain the threads' current instruction working set, the application's code is effectively spread over the system's private i-caches and code misses are greatly reduced. Proof-of-concept work at the KIT OS group shows the potential of this technique, but the implementation does not scale to multiple clients and cores. In this thesis, we therefore propose that the spreading technique described above must be tightly integrated with the OS thread scheduler. We present an unintrusive user-space API that allows partitioning a multi-threaded server's request handler code path into *stages*. Our scheduler then dynamically assigns cores to stages and dispatches threads on their current stages' cores.

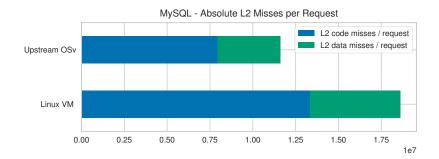

We evaluate our design and its implementation in the OSv library operating system by adapting the MySQL database management system to our solution. We achieve up to 22% higher throughput caused by a 65% reduction of L2 i-cache misses without having to sacrifice request latency for this improvement.

ABSTRACT

vi

# Contents

| Abstract |      |                                        |           |  |

|----------|------|----------------------------------------|-----------|--|

| Contents |      |                                        |           |  |

| 1        | Intr | roduction                              | 3         |  |

| <b>2</b> | Rela | ated Work                              | 7         |  |

|          | 2.1  | Network Servers & Concurrency          | 8         |  |

|          | 2.2  | Cohort Scheduling & Staged Computation | 9         |  |

|          | 2.3  | Staged Event-Driven Architecture       | 10        |  |

|          | 2.4  | STEPS                                  | 11        |  |

|          | 2.5  | Top-Down Performance Analysis          | 13        |  |

|          | 2.6  | Profiling Datacenter Applications      | 15        |  |

|          | 2.7  | Interim: Applicability to SMP Systems  | 16        |  |

|          |      | 2.7.1 Private Caches                   | 16        |  |

|          |      | 2.7.2 Real Parallelism                 | 16        |  |

|          | 2.8  | Computation Spreading                  | 17        |  |

|          | 2.9  | Prototype in Linux at the KIT OS Group | 18        |  |

| 3        | Ana  | lysis                                  | <b>21</b> |  |

| 4        | Des  | ign & Implementation                   | 25        |  |

|          | 4.1  | The OSv Library Operating System       | 28        |  |

|          |      | 4.1.1 The OSv Scheduler                | 29        |  |

|          | 4.2  | The Stage API                          | 30        |  |

|          | 4.3  | Fast Thread Migration                  | 32        |  |

|          | 4.4  | Thread Migration on Wake-Up            | 36        |  |

|          | 4.5  | Core Allocation Policy                 | 40        |  |

|          |      | 4.5.1 OSv's Page Access Scanner        | 44        |  |

| 5        | Eva  | luation                                | 47        |  |

#### CONTENTS

|                  | 5.1          | Evaluation Setup                                    | 48 |  |  |

|------------------|--------------|-----------------------------------------------------|----|--|--|

|                  |              | 5.1.1 Configurable Idle Strategy in Upstream OSv    | 51 |  |  |

|                  | 5.2          | Adopting the Stage API in MySQL                     | 51 |  |  |

|                  | 5.3          | Whole-System Benchmark with MySQL                   | 55 |  |  |

|                  | 5.4          | Validation of Design Assumptions                    | 57 |  |  |

|                  |              | 5.4.1 Instruction Working Set Spreading             | 57 |  |  |

|                  |              | 5.4.2 Changes to Thread Migration                   | 59 |  |  |

|                  |              | 5.4.3 Core Allocation: Validation of Implementation | 64 |  |  |

|                  |              | 5.4.4 Core Allocation: Performance Evaluation       | 66 |  |  |

|                  | 5.5          | Discussion                                          | 68 |  |  |

| 6                | Con          | nclusion                                            | 69 |  |  |

|                  | 6.1          | Future Work                                         | 70 |  |  |

| $\mathbf{A}_{]}$ | Appendix     |                                                     |    |  |  |

| Bi               | Bibliography |                                                     |    |  |  |

2

## Chapter 1

# Introduction

Network servers are of ever-increasing importance in today's infrastructure, handling requests from clients at high degrees of concurrency. A common implementation pattern is a *sequential* handler routine that processes each request, consisting of logical stages such as protocol handling, decoding/encoding and actual business logic. Concurrency is achieved by executing the handler code per connection in separate operating system thread – either by spawning a thread per request or by using a thread pool. The sequential handler implementation is simple to follow for programmers and abstractions for the aforementioned threading models are available in virtually any programming language and operating system. [PDZ99; Keg99]

Given the increasing CPU-memory-performance gap, it is paramount that the request handler's working set fits into the private CPU caches. The code-part of the working set is of particular importance to avoid stalling the execution pipeline of contemporary super-scalar out-of-order processors. The dominant CPUs in the server market are x86-64 based Intel processors featuring separate 32KiB L1-d and L1-i caches and a unified 256KiB L2 cache per core, as well as a shared inclusive L3 cache that is significantly larger. [NehAnand] Recent profiling at Google shows that this memory hierarchy fails to meet the demands of contemporary server applications: Request handling code exhibits little spacial locality and thrashes the private CPU caches, leading to frequent pipeline stalls and sub-optimal application performance.[Kan+15]

Previous work in this field includes techniques such as *cohort scheduling*: Threads that execute the same working set are grouped into *cohorts* and dispatched in series, thereby amortizing instruction cache misses among all threads in the cohort. *Staged Computation* expands this concept to general software architecture and *staged event-driven architectures* (SEDA) generalizes it further: Request processing state is encapsulated into an object which is passed through a pipeline of stages interconnected by queues. Each stage controls the concurrency model used to perform its work, allowing cohort scheduling to be employed. A derivative of cohort scheduling has been implemented in a research DBMS under them term *STEPS*, yielding an overall speedup of 40% in the TPC-C benchmark.[LP01; WCB01; HA04; Har05]

Despite the promising results of the research presented above, the concepts have found little practical adoption. For example, the popular database management systems MySQL still uses thread-based concurrency (one handler per request) with a pre-spawned pool of handler threads. [MySQL]. Apart from the required software-engineering effort do adapt an existing project to SEDA, we must also consider that the solutions mentioned so far were designed for uniprocessors. However, given the ubiquity of SMP systems, techniques such as *computation spreading* propose a different approach to mitigate i-cache thrashing: With computation spreading, OS code is executed on different cores than user-level code, thereby effectively splitting the application's working set at the user-kernel-boundary, resulting in better use of the private caches per core. Experimental work at the KIT OS group generalizes computation spreading to support migration points at arbitrary positions in the application code: Application developers manually partition their code into *stages* and insert one-line stage switching calls into the request handling code path. By dedicating CPU cores to stages and migrating threads between the cores on stage switch, the request handler's instruction working set is spread over the private caches of these cores. A proof-of-concept implementation in Linux and the MySQL database management system shows that for a single concurrent client, L2 cache misses can be reduced by up to 40%, correlating with up to 17% increased throughput. However, for more than one client and for increased core counts, the achieved throughput is up to 40% lower compared to running on standard Linux. The proof-of-concept is thus clearly not work-conserving, but shows the potential gains achievable by the technique.

In this thesis, we present a stage-aware thread scheduler that sustains the performance improvements achieved by instruction working set spreading at a high number of concurrent clients and multiple CPU cores. Our solution requires minimal customization effort for adoption in multi-threaded servers, making it particularly attractive for large legacy codebases that cannot be easily refactored to support more efficient concurrency models. Specifically, our contributions are as follows:

- We analyze the design aspects that make the early 2000's approaches of cohort scheduling and STEPS inapplicable to SMP systems.

- We analyze the design and implementation of the aforementioned proofof-concept implementation at the KIT OS group and point out why it is not work-conserving.

- We present a user-space C++ API for applications to manually define stages and stage switching points in the request-handling code path.

- We present the design and implementation of a work-conserving scheduler that allocates CPUs to stages and migrates threads as necessary to preserve warm instruction-caches.

- We show the practical applicability of our solution by adopting it in MySQL, resulting in 22% increased throughput and a 65% reduction in L2 i-cache misses.

The remainder of this thesis is structured accordingly. In Chapter 2, we examine preceding work in the area of high-performance network server design. Chapter 3 describes the design of the KIT OS group's proof-of-concept, pointing out why it is not work-conserving. Subsequently, Chapter 4 presents the design and implementation of our solution in the OSv library operating system. Finally, we evaluate our implementation in Chapter 5 by applying it to MySQL and showing that our design decisions have their intended effects.

## Chapter 2

# **Related Work**

High-performance network servers must handle requests at a degree of concurrency that exceeds the parallelism provided by hardware in the form of CPU cores. Much research has gone into techniques to handle this problem, further constrained by additional requirements such as predictable response times and fairness among clients. This chapter starts with an overview of the prevalent concurrency models in the early 2000s' software landscape. We proceed with an introduction to cohort scheduling, staged computation and staged event-driven architecture which stem from the same time period and present *STEPS*, which applies above concepts to a research database management system, showing that these software-only solutions lead to performance improvements due to reduced i-cache misses and better branch prediction. Despite these in research systems, large-scale profiling at Google from 2015 shows that the memory hierarchy in contemporary processors is still suboptimal for typical datacenter applications. Given that the approaches above targeted single-core machines from the early 2000s, we take a step back and analyze their applicability to today's multi-core systems and memory hierarchies, coming to the conclusion that major redesigns are required to provide work-conserving solutions. Motivated by the ongoing relevance of the topic and a changed hardware landscape, we explore *computation spreading*, a technique that explicitly targets SMP systems and uses thread migration to spread the instruction working set of a thread over multiple CPU cores. We conclude with a proof-of-concept implementation at the KIT OS group which extends computation spreading to arbitrary split points within userlevel code, forming the basis for this thesis.

#### 2.1 Network Servers & Concurrency

Network server software is generally concerned with receiving requests from clients over a network connection, acting upon them and returning a response. In addition to the network I/O, disk access is very common, for example within file servers. The request handlers are thus commonly I/O bound. [WCB01]

I/O hardware interfaces are asynchronous, allowing the CPU to perform useful work while the slow I/O operation completes. However, the traditional *software* abstractions exposed by UNIX-like operating systems are synchronous: Processes or threads that block on I/O operations are preempted from the CPU and only resume execution once the result of the operation is available. Out of this situation, the following type of software architecture emerged: *Multi-process* and *multi-threaded* servers handle requests by following a sequential description of the steps involved to fulfill the requested task. Concurrency is then achieved by having multiple threads (either spawned on demand or from a pre-spawned pool) execute the same request-handling function for different connections and to interleave these control flows by time-multiplexing the CPU. This interleaving happens each time an I/O activity blocks or at the end of the scheduler-assigned time slice. Canonical scalability problems with this approach are the context switching overhead and the minimal amount of memory each thread requires, e.g., for its TCB and stack. Furthermore, synchronizing request handlers on shared resources without busy waiting requires kernel-supported synchronization primitives, implying syscall overhead. [PDZ99; Keg99; ALL89; WCB01]

One alternative to the above are *event-driven architectures* where the server consists of a loop that allocates a state object per request and implements a finite state machine driven by those objects. Each thread of the server acts on one state object at a time, but does not perform blocking operations. Instead, the operations are merely initiated and the state machine immediately switches to the next state object. The server loop picks up the completion events of these asynchronous I/O operations and changes the corresponding state object accordingly. This change in turn eventually triggers the state machine to perform the next logical request-handling step for the request represented by the state object. [PDZ99; WCB01; Keg99]

For this thesis, the most relevant difference between multi-threaded and event-driven architecture lies in the representation of request-handling state: Multi-threaded servers encode it implicitly in the thread's execution state, consisting mostly of its stack, registers and instruction-pointer. In contrast, event-driven servers explicitly define the finite-state machine and have a dedicated representation of the processing state in the state objects.

Although the above description focuses on the role of I/O, nothing stops application developers from partitioning their CPU-bound or memory-intensive request-handling steps using the same mechanism. The next sections give an introduction to *staged computation* and *staged event-driven architectures* which build on top of the event-driven model.

## 2.2 Cohort Scheduling & Staged Computation

In the early 2000s, Larus et al. investigated the cache behavior of I/O intensive online-transaction processing workloads (OLTP) in servers implementing the multi-process or multi-threaded architecture. They observe high cache miss rates and instruction stalls, attributing it to the large amount of system calls made by the request handler threads: System calls themselves have a large working set disjoint from the application code and might bring an entirely different working set into the cache when blocking and switching to another thread. [LP01]

Cohort scheduling is then proposed as a scheduling policy to dispatch threads that are currently executing the same code segment in batches (cohorts): The first thread in a cohort may incur instruction / data cache misses but all successors of the same cohort benefit from a warm cache. Naturally, the threads must yield the CPU before leaving this shared code segment and the segment size must not exceed the i-cache size to avoid thrashing the cache. The number of threads per cohort represents the central trade-off in the scheduling policy: Large cohorts yield fewer amortized cache misses but cause higher response time due to progress only being made once enough threads have reached the synchronisation point required for batch dispatch. Furthermore, since the amortization only reduces the execution time but does not eliminate it, the minimum response time is necessarily increased. [LP01]

For immediate application, the authors suggest systems calls as pre-existing synchronisation points because they do not require modifying user-space code. However, to increase cache locality in arbitrary parts of an application, the authors propose *staged computation*: In this programming model, instead of synchronous calls to subroutines, the request-handling stage posts asynchronous operation requests to other stages, each encapsulating a particular functionality and state. A stage has *scheduling autonomy*, which means

it is free to choose the concurrency model that suits the type of provided operation best — cohort scheduling being just one of several options. [LP01].

Cohort scheduling at the syscall boundary is non-invasive with regards to application code bases and will we revisited by *computation spreading* (Section 2.8). In contrast, staged computation requires non-trivial refactorings in existing applications, in particular if they already follow the multi-threaded model: Synchronous, blocking operations must be converted to asynchronous operations and continuations, and the scheduling autonomy granted to each stage must actually be addressed in code.

## 2.3 Staged Event-Driven Architecture

Staged event-driven architecture (SEDA) is a software architecture generalizing the idea of staged computation. The primary motivation for its inception was the construction of network servers whose performance should degrade linearly under an increasing number of concurrent requests. SEDA provides a framework for application developers to implement an event-driven server by only defining event handlers. Each event handler represents a *stage* and is invoked by its stage controller, which executes the event handler on the stage's thread pool with input from the stage's *incoming event queue*. The event handler can enqueue additional work into other stages' queues, but cannot call into their code directly, enforcing an explicit boundary in the application's control flow. The stage controller works in a feedback loop to ensure a stage's performance requirements are met, for example by adjusting the thread pool / *cohort size* to meet a certain response time goal.<sup>1</sup> Stage controllers can be further customized to the application's unique requirements, providing an opportunity for developers to take full control of each stage's concurrency-model. [WCB01]

The authors evaluate SEDA by implementing an HTTP server and measuring the performance metrics total concurrent throughput and response time over a varying number of concurrent clients. Additionally, they measure the amount of requests each client completes, defining an equal distribution of service among clients as ideally *fair*. The results show 16–20% higher throughput at little-varying response times and high fairness among clients in comparison to the the multi-threaded Apache web server. The authors'

<sup>&</sup>lt;sup>1</sup>SEDA terminology for a resource controller implementing cohort scheduling is "batching controller".

#### 2.4. STEPS

explanation for these results is that the SEDA server queues all requests *inside* the application whereas the multi-threaded Apache web server will not accept new client connections when reaching the maximum size of its thread pool, causing exponentially increasing response times for non-accepted clients due to exponential back-off algorithm employed in TCP. [WCB01]

SEDA shows the software-engineering and performance benefits of staged computation but requires adapting the application to use the provided framework of event handlers and stage controllers. In contrast, our solution requires minimal effort for adoption in multi-threaded servers, for which we expect non-trivial amounts of refactoring work to be required for SEDA. Notably, the SEDA authors suggest operating system support for their model, emphasized by their need to implement asynchronous I/O abstractions for their resource controllers. Although async I/O may facilitate the implementation of SEDA itself, it does not address the hurdle of refactoring existing code bases.

## 2.4 STEPS

The Synchronized Transactions through Explicit Processor Scheduling project (STEPS) implements a derivative of cohort scheduling in the SHORE research database system. [Reg12]

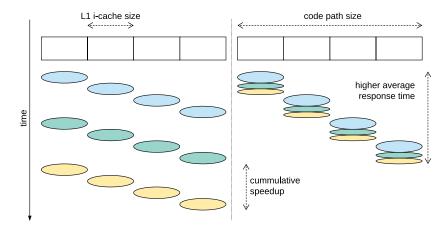

The authors reproduce the observations already made by the authors of cohort scheduling [LP01] for database systems: The execution flow in databases exhibits low spatial locality and the instruction working set does not fit into the CPU caches, leading to pipeline stalls and a high amount of mispredicted branches. In contrast to cohort scheduling, STEPS groups threads into *team lists* organized by the high-level application-specific operation they currently execute, for example INSERT or UPDATE queries. The code path of the operation then contains context-switching points (CTX calls) at which the currently executing thread yields control to the next member of its team list, which amounts to user-mode round-robin scheduling within a team. Contextswitching points are placed such that the working set between two of them fits into the CPU's L1 i-cache. The schema described above leads to a stepby-step progression of the entire team that is depicted in Figure 2.1. As an example, let us imagine three context-switching points A, B and C and a team of ten threads executing between A and B. After the last thread reaches B, the team moves forward to the next step B to C. Although the first thread

executing this step will incur capacity i-cache misses, it pre-warms i-cache and branch predictors for the remaining nine threads. [HA04]

Figure 2.1: Idealized scenario of three threads (different colors) executing the same code path that does not fit into the L1 cache. Left: Each thread passes through the code completely before yielding CPU to the next thread. **Right**: A team of threads trickles down the code path in code segments that do not exceed the L1 i-cache size.

Blocking threads or those that abort the operation would fall behind in this trickle-down schema and thus no longer share their ex-team members' code. The solution is to remove blocking or aborting threads from the team list and track them as *stray threads*. The publications on STEPS describe that the thread package in SHORE required modification to support this schema, but falls short on implementation details. For this thesis, though, blocking is a highly relevant topic because it is a major problem in the proof of concept implementation at the KIT OS group (see Section 2.9 and Chapter 3). By examining the 6.0 release of SHORE which was published after STEPS, we can identify a base class for all DBMS threads called **sthread\_t** which provides wrappers for basic blocking I/O functions such as the **read** or **write** syscalls. Under the assumption that these abstractions existed in the version of SHORE that STEPS was based on, we are confident that the STEPS authors used these wrappers to get notified about potentially blocking I/O requests by a thread to remove it from its team list. [Reg10; Reg12]

Regardless of the exact implementation details, we are not convinced that the adoption of STEPS in arbitrary applications requires as few code modifications as claimed by the authors: SHORE already comes with a custom thread abstraction around the *POSIX threads API* (pthreads) and centralized wrappers around blocking I/O. In contrast, arbitrary applications will use the pthreads and C standard libraries directly, in which case either substantial modifications to the code base are necessary to establish a situation as found in SHORE or runtime-patching via LD\_PRELOAD would be required.

Lastly, STEPS's handling of stray threads should be considered: Recall that stray threads are removed from their team when performing potentially blocking syscalls, and only re-join a team when re-starting a new high-level operation. [HA04] This means that STEPS does not account for the instruction footprint of the operating system at all. However, Agarwal et al. show that the operating system has a significant cache footprint and should thus be considered when trying to optimize the i-cache footprint. [AHH88; CWS06] Stray thread will further continue to compete for CPU time for the time until they finally block. Since the OS scheduler is unaware of the team lists, it may schedule a stray thread in the midst of a team, evicting its cache state inadvertently. STEPS tries to prevent such situations by giving a "hint" to the scheduler to prioritize the next thread that remained in the team, but does not elaborate on the additional syscall overhead. In this thesis, we propose an implementation that is implemented in the OS scheduler, thus avoid the information loss and implementation complexities associated with STEPS's user-space approach.

#### 2.5 Top-Down Performance Analysis

For the upcoming Section 2.6 and the evaluation in Chapter 5, we require some basic understanding of modern out-of-order processors and the *topdown performance analysis method*.

Modern high-performance microprocessors employ various techniques to exploit instruction-level parallelism (ILP) and to keep all functional units of the system busy. *Pipelining* is a very basic solution that splits the execution of an instruction into multiple phases. An instruction passes through an *N*-staged pipeline in  $N * C_{max}$  clock cycles where  $C_{max}$  is the number of clock cycles required for the slowest pipeline stage. More sophisticated superscalar processors replicate the functional units of individual stages, enabling multiple instructions to be completed (*retired*) per clock cycle. The state-of-the-art technique to manage this pipeline is called dynamic pipeline scheduling where it is the job of the hardware instead of the software and compiler to optimally supply functional units with work. Further techniques to exploit ILP are branch prediction and speculative execution. [PH05].

In any way, the above architecture is barely comparable to the classical model of a single-issue pipeline. Thus, Intel describe their contemporary microarchitectures as being split into 3 main parts: An *instruction fetch unit* that decodes the incoming instruction stream into micro-operations (uops), an *out-of-order execution engine* that executes those uops on functional units and an *in-order retirement* unit that ensures that the effects of the issued instructions appear in program order. [Cor16].

Yasin [Yas14] further simplify this view by only differentiating between *fron*tend and backend: The frontend is responsible for fetching instructions, decoding them to uops and supplying them to the backend, which in turn is in charge of fetching operands, scheduling uops on the functional units and retiring instructions in program-order. The authors present the **top-down** performance analysis method, which helps to identify micro-architectural bottlenecks by classifying CPU time into categories that are organized in a nested tree. When applying the method, one traverses the tree top-down, usually following those categories marked with the highest percentage of spent CPU time. The data source for the classification are performance counters which are built into to the CPU and are accessible by software.

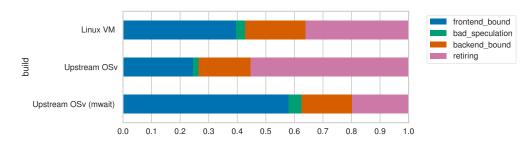

For this thesis, we will focus on the *top-down top-level breakdown*, i.e., the highest level of the category tree. The categories at this level are *retiring*, *bad speculation*, *backend-bound* and *frontend-bound*. The first two categories indicate that actually or at least potentially useful work was done whereas the latter two categories classify those pipeline slots lost due to microarchitectural bottlenecks: Backend-bound cycles do not perform useful work because operations in the backend take exceptionally long, thereby introducing *bubbles* into the execution pipeline. Examples for this category may be a sub-optimal instruction mix or d-cache misses on uop-operands. In contrast, frontend-bound cycles do not perform useful work because the backend is undersupplied with uops. For example, i-cache misses will cause no instructions to be decoded and thus no uops to be issued for execution. [Yas14; Cor17; Cor16]

In this thesis, we optimize i-cache behavior by partitioning the instruction working set. Reducing the percentage of frontend-bound cycles is thus used as a success metric in our evaluation.

#### 2.6 Profiling Datacenter Applications

Although the micro-architectural performance problems caused by large icache footprints were already observed in [LP01] and [HA04] in the early 2000s, recent profiling work at Google shows that computer architecture is still not able to satisfy the requirements of contemporary scale-out applications. However, the potential performance gains and cost savings due to improved cache behavior become relevant at scale, motivating a re-assessment of the situation.

Kanev et al. identify a significantly higher amount of pipeline stalls in realworld datacenter applications when compared to the SPEC CPU2006 benchmark. Apart from the overhead associated with distributed software architecture (*datacenter tax*), a large cache footprint (both code and data) reveals the major performance bottleneck on today's processors for typical datacenter applications: The authors observe 60% of  $\mu$ op slots to be backend-bound, and 15 – 30% to be frontend-bound. In particular, the authors find that more than 5% of cycles are wasted due to empty front-end buffers, which is attributed to instruction read misses in the private L2 cache, resulting in slow accesses to the CPU's shared last level cache. Additionally, the observations confirm that applications under active development grow in their instruction working set, worsening the situation.<sup>2</sup> The authors do not explicitly investigate why datacenter applications have such large instruction working sets but mention *lukewarm* code and static linking as possible contributors. [Kan+15]

In comparison to the work published a decade earlier (see Section 2.2 and 2.4), Kanev et al. focus on computer-architecture and only pay brief attention to the operating system: Approximately 20% of CPU time is spent in the kernel with more than 5% in the scheduler alone. Additionally, it is noteworthy that the 90-th percentile of the observed machines handles more than 4500 concurrent threads. Given that at least a portion of these threads will be part of network servers, the question of the concurrency model thus stays very relevant although not explicitly stated as a source of performance-optimizations. [Kan+15]

Looking at the related work presented so far, we conclude that for more than 15 years, typical datacenter applications have been observed to exhibit high i-cache-miss and branch-misprediction rates, resulting in sub-optimal use of the available CPU resources and motivating continued research in this field.

$<sup>^2 {\</sup>rm The}$  authors present exemplary results of up to 27% per year.

## 2.7 Interim: Applicability to SMP Systems

Cohort scheduling, SEDA and STEPS were all evaluated on single-core machines. Adaption to multi-core systems is not mentioned at all or stays theoretical. [HA04; HA03] Given today's ubiquitous multi-core systems and the ongoing relevance of high i-cache footprints, re-examining the applicability of the above approaches seems appropriate.

#### 2.7.1 Private Caches

The uniprocessor machines used to evaluate cohort scheduling, SEDA and STEPS feature a small L1 cache and a larger, higher-latency L2 cache. However, contemporary symmetric multi-core systems typically have a *private* L1 and L2 caches per core and a *shared* L3 cache. The capacities of the per-core L1 and L2 are comparable to the early 2000s' uniprocessors' caches. The access latency between L1, L2 and L3 increases by a factor of 3 - 4 between each level. Beyond the L2 level, instruction cache misses can typically not be compensated by out-of-order processing. [HP02; 7cp]

Given these hardware constraints, an adaption of cohort scheduling and STEPS to multiprocessors must target the private caches of each core to benefit from warm i-caches. More importantly, the existence of private caches per hardware thread adds the problem and opportunity to allocate this resource: In terms of STEPS, multiple steps can now be spread over different cores instead of time-multiplexing only one cache. We will come back to this observation when assessing *computation spreading* in Section 2.8.

#### 2.7.2 Real Parallelism

We recall from Section 2.2 that the scheduling trade-off in both SEDA and STEPS consists of reduced cache misses vs. increased response time due to *batching*. However, the real parallelism available on SMP systems brings with it another scheduling dimension that STEPS and cohort scheduling do not address: To utilize the available hardware threads, load must be balanced among them to maximize resource utilization, which generally surpasses response time as the primary scheduling goal. All relevant operating systems abstract CPU cores through threads, and the OS scheduler implements load balancing by migrating threads between cores, often directed by metrics such as the length of each core's the ready queue (*load*). [MN04]

#### 2.8. COMPUTATION SPREADING

Cohort scheduling and STEPS were not designed for this situation because **batching is inherently not work-conserving on SMP systems**: All threads in a cohort or team must run on the same core to benefit from the warm i-cache, implying that only one thread per team can run at any given time. Furthermore, STEPS and the OS scheduler work actively against each other because the latter will see all threads in a cohort as runnable and actively spread the cohort over all (presumably idle) cores.

An easy fix would be a mechanism for STEPS to influence the load balancing to favor threads of the same team to stay on the same core, e.g., through thread pinning. Thread-pinning is obviously not work-conserving on multicore systems and requires additional mechanisms and communication between STEPS and the OS scheduler, thus complicating the implementation. On a busy system, one could further argue that enough runnable threads are available to simply employ cohort-scheduling per core. However, in contrast to the approach of *computation spreading* presented in the next section, percore cohort scheduling replicates to each core the repeated capacity misses when a team moves to the next step.

The above assessment shows that cohort scheduling, SEDA and STEPS cannot be directly applied to today's multi-core systems. The availability of private caches per core must be accounted for and new requirements such as load balancing between cores must be addressed. However, given the ongoing relevance of the problems identified more than 15 years ago, we continue this chapter by investigating publications that explicitly target multi-core systems.

## 2.8 Computation Spreading

Computation spreading (CSP) in its most general form is a technique to spread the instruction working set of a process more effectively on SMP systems which commonly feature private caches per core. Chakraborty et al. [CWS06] show that this cache hierarchy leads to redundantly stored code. For example, in a traditional thread-based concurrency model, each requesthandling thread may interact with the file system through system calls which leads to redundantly stored file system code in each core's private cache. The authors present a solution that dedicates CPU cores to either OS code or user-level code. Threads entering or leaving the OS synchronously through syscalls, exceptions or page faults are then migrated between compatible cores. [CWS06] A central aspect of the implementation is the thread migration mechanism, which is based on hardware virtualization features: All synchronous kernel entries are intercepted and used to trigger the thread migration, allowing adoption of CSP without any modifications to *guest* OS and user-space software. [CWS06] However, since hardware-based thread migration is only available in hypervisor mode, cooperation from the software executing in this mode is required. Deployment in public clouds based on hardwarevirtualization is thus only possible with explicit support by the cloud provider and would require further work in the hypervisor scheduler. Our solution does require hardware virtualization only due to limited driver support but implements thread migration in software and can thus be deployed to existing infrastructure.

The authors evaluate their solution using full-system simulation of an eightcore machine with private L1 and L2 cache and a shared L3 cache. Server applications, which are of primary interest for this thesis, exhibit 25 - 58%fewer L2 instruction misses and 9 - 25% improved branch misprediction rates. Data read misses are less affected, with only 13 - 19% decrease for Apache web server and an *online transaction processing* (OLTP) application. The approach leads to a speedup of up to 20% in Apache and 9.4% for OLTP, measured by comparing total runtime of a full-system simulation. [CWS06]

Despite the very specific implementation, it should be noted that the concept presented by the authors is more general and not limited to the syscall interface: They suggest migration points at arbitrary positions in the application code and corresponding core allocation policies. [CWS06] However, we cannot find a concrete proposal ready for implementation.

## 2.9 Prototype in Linux at the KIT OS Group

At the KIT OS group, a Linux-based proof-of-concept implementation combines the idea of staged execution, cohort scheduling and computation spreading into a C API that allows for intuitive conversion of existing code bases to staged execution: The application developer manually identifies stages and inserts library calls into application code for switching the current stage. Each CPU core is assigned one or more stages and each time a thread switches to a new stage, it is migrated to a core assigned to that stage, benefiting from a warm i-cache. This approach targets applications that employ thread-based concurrency, i.e., the multi-threaded server architecture outline in Section 2.1, since the stage-switching is embedded into the control flow of the request handler and thus not explicitly modeled like in SEDA (see Section 2.3).

Fast thread migration mechanism is required for this technique to succeed. Otherwise, the performance benefits of always-warm caches per stage are destroyed by the migration time. The Linux built-in facility for this purpose, sched\_setaffinity, is impractical because it uses expensive inter-processor-interrupts to implement this syscall, resulting in  $9\mu s - 14\mu s$  of migration time. As a consequence, thread migration was implemented in user-space: For each user-level thread (ULT), there still exists exists a kernel-level thread (KLT), but KLTs are pinned once to a specific core and stage. ULTs run on a KLT of the stage they are currently in and migrate to a different KLT when switching stages. [KST10]

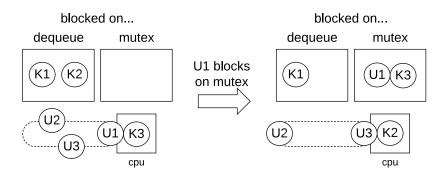

When a ULT makes a call to switch stages, its context is saved and enqueued into the next stage's incoming migrations queue. The source KLT now waits for new ULTs on its own stage's incoming migrations queue. If it is empty, the KLT makes a blocking syscall  $sys_dequeue$  to a kernel component to wait for incoming migrations. The kernel component must ensure that there is always one KLT per core either doing work or actively dequeuing ULTs to utilize the CPU. To accomplish the availability of a dequeuing KLT per core, a callback from the Linux scheduler informs the kernel component of task state changes. For example, if the currently dequeuing KLT  $K_1$  executes a ULT, and that ULT blocks on a mutex,  $K_1$  transitions from running to blocked. The kernel component must then wake up another KLT  $K_2$  that is currently waiting for incoming migrations of that stage on that core. Otherwise, the core does not perform any work (for the application) until  $K_1$  acquires the mutex and becomes runnable. Figure 2.2 visualizes this situation.

Figure 2.2: When a ULT issues a blocking syscall, the current KLT blocks. Another KLT must take over executing ULTs from the core's queue. Note that although there is a KLT for each ULT, the relationship is not fixed.

The authors evaluate their system using the TPC-C benchmark, comparing throughput and cache behavior of a modified version of MySQL 5.6.38 against an unmodified version as a baseline. For a single client and low core counts, they observe the expected 40% reduction in L2 cache misses, correlating with a 17% speedup in throughput. However, for both an increased number of concurrent clients and a higher number of CPU cores, throughput is 10 - 40% below baseline. Additionally, L2 miss rates and achieved throughput do not correlate with more than one concurrent client. In the next chapter, we present our analysis of the reason behind this behavior.

20

## Chapter 3

# Analysis

Related work has shown that the instruction working set of datacenter-class server applications often exceeds the size of modern processors' private icaches. Computation spreading is proposed as a technique to spread the instruction working set of such servers over the available private caches through thread migration. The authors provide an implementation based on hardware virtualization instructions to separate OS kernel code from the application (see Section 2.8).

In contrast to computation spreading, the proof-of-concept implementation at the KIT OS group proposes a software-only solution that allows splitting the instruction working set of an application at arbitrary positions in its code. Multi-threaded servers can be adapted to use the technique without significant refactoring. The MySQL DBMS shows a speedup of up to 17% in throughput in the TPC-C benchmark with a single client. However, with multiple clients and cores, the solution performs worse than unmodified MySQL. This chapter provides an explanation of the inherent design problems in the proof-of-concept which lead to the behavior described above and motive the work presented in this thesis.

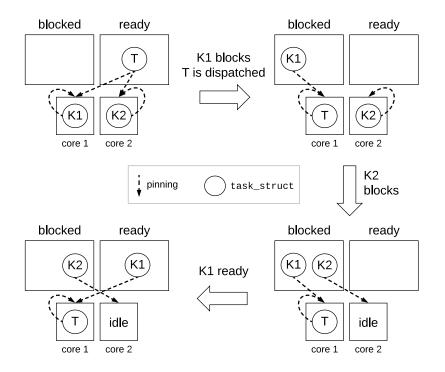

Let us imagine a system as depicted in Figure 3.1, starting with a ULT  $U_1$  in stage S executing on a KLT  $K_1$ . As described in Section 2.9,  $K_1$  is pinned to core  $C_1$ . When  $U_1$  performs a blocking syscall, for example when trying to acquire a lock,  $K_1$  blocks. The Linux scheduler now dispatches another task T on  $C_1$  to maximize CPU utilization, where T is not a  $K_i$  of our application. In fact, all  $K_i$  are blocked in sys\_dequeue. When  $K_1$  finally acquires the mutex and is ready again, it is still pinned to  $C_1$  because the solution needs pinning to perform thread migration in user-space. However,  $C_1$  is still executing T, not  $K_1$ , and thus  $K_1$  must be put into  $C_1$ 's ready queue.

On a single-core system, the situation described above would be acceptable because T is also performing useful work. However, we have another CPU  $C_2$  where a KLT  $K_2$  is dequeuing ULTs for the same stage S: If  $K_2$  does not have any ULTs to execute,  $K_1$  should be migrated to  $C_2$  immediately when it is woken up and continue execution there, benefiting from the warm on-core caches. But the implementation only performs thread migration when a ULT calls the stage switching API. There is no mechanism in place to save  $K_1$ 's state and enqueue it to  $K_2$ 's incoming migration queue on wake-up. One might assume it is possible to enqueue  $U_1$  to  $K_2$  since we saved its register state on kernel entry via pthread\_mutex\_lock: This is not possible because there might still be kernel code that needs to run after the mutex is acquired, before returning to  $U_1$ .

Figure 3.1: The proof-of-concept implementation is not work-conserving. When K1 becomes ready it should be dispatched to C2 immediately. But K1 is pinned to C1 due to the implementation of thread migration.

We identify several fundamental problems in the approach taken by the proofof-concept implementation: The requirement for fast thread migration drove the design toward a user-space solution which decouples the threads known by the application (ULTs) from the threads known by the kernel (KLTs). However, the kernel scheduler still only handles KLTs and assumes a 1:1 threading model, which leads to an **ambiguous role of KLTs** in the proof-of-concept: When switching between stages, the user space thread migration code views KLTs as the CPUs they are pinned to. But when a ULT running on a KLT interacts with the Linux kernel, the kernel sees a normal task\_struct and continues to assume the 1:1 threading model where tasks can just block. The proof-of-concept works around this schizophreny by introducing a callback from the scheduler to react to blocking KLTs, but fails to handle asynchronous events like wake-ups, which we expect to require further integration into the scheduler.

We conclude that the proof-of-concept does not model the situation correctly: The association of stages and CPU cores is piggybacked onto the KLTs using sched\_setaffinity, leading to an ambiguous role of KLTs. We thus propose the following guidelines for a proper design:

- Stages must be modeled as kernel objects, separate from CPUs and threads.

- The association of stages and CPU cores must be represented explicitly.

- Threads must carry the information in which stage they are executing.

- The scheduler must honor this information by scheduling threads onto cores that are associated with their respective stage.

- The scheduler must trade off the potential gains of always-warm caches against existing scheduling goals such as resource utilization, fairness and response time.

These guidelines revert the complex situation of ULTs and KLTs to a simple 1:1 threading model and remove the special-case of blocking kernel activity. The remainder of this thesis presents our design which follows the proposal above.

## Chapter 4

## **Design & Implementation**

Certain classes of datacenter applications exhibit large instruction working sets that do not fit into the private cache of commodity processors. On a micro-architectural level, the large instruction working set leads to i-cache thrashing and thus underutilization of the cores' functional units, which in turn degrades application performance. This chapter presents our operating-system-based solution to mitigate these micro-architectural problems in multi-threaded servers using a software-only solution.

Multi-threaded servers handle client connections in threads, each following the same, sequential, potentially blocking, code path. For example, in a database management system that is accessed over TCP, a request-handling thread will

- (a) read the request data from a socket, using the network stack,

- (b) deserialize & parse it,

- (c) perform the requested operation,

- (d) serialize the response and

- (e) send it back to the client.

Database systems exhibit a significant i-cache footprint in step (c) per highlevel SQL operation (see Section 2.4). The code footprint of the network stack is also significant, as is the filesystem and potentially the serialization library.

All these steps combined will execute more code than fits in the private i-cache, leading to capacity i-cache misses when executed on a single core. Additionally, some code will be executed twice, but with another i-cache sized working set being used inbetween: For example, steps (a) and (e) share parts of the network stack but steps (b), (c) and (d) will execute before (e). Step (e) will thus likely incur i-cache misses for code that step (a) had brought into the cache at the beginning of the procedure. Furthermore, we must consider the situation where a request-handler thread A blocks, for example on I/O in steps (a), (c) or (e): The scheduler will dispatch another request-handler B on the same core, which may be in a different step than A. At worst, B will evict all of A's cache state. Looking at multi-core systems, the above behavior can be observed on each core because contemporary OS schedulers balance threads based on load of the cores, not on cache state. [MN04]

We solve above problems on modern multi-core systems by implementing a suitable scheduling policy in the OS scheduler. We define a *stage* as a span in the request-handling code path that has an instruction working set smaller than the private i-cache size. Ideally, different stages' instruction and data working sets are fully disjoint. Given the example database system, one would define the following stages:  $S_n$  for network stack,  $S_{ser}$  for serialization and one per SQL operation ( $S_{INS}$  for INSERT,  $S_{SEL}$ for SELECT, ...). It is important to emphasize that stages do not necessarily form a pipeline: Reading from and writing to the network socket form one stage because these operations share the network stack code, as do request deserialization and response serialization because they both use the serialization library.

Once the stages are defined, a request-handler thread must switch to the appropriate stage before performing the next step of request-handling. In concrete terms, this means that developers must call a system API in the request-handling code path. In the example above, a SELECT request would result in the following switch series:  $S_n$ ,  $S_{ser}$ ,  $S_{ser}$ ,  $S_{n}$ . For the rest of this thesis, we will refer to an application that uses the stage API as described above as a *stagified* application.

Our scheduler tracks a thread's association to its current stage in the thread's TCB. Additionally, it tracks per stage the number of runnable threads associated with it. We then use this information to periodically compute the *current core allocation*, which assigns CPU cores to stages proportional to the stages' load. A core is thus always allocated to exactly one stage. The scheduler then implements the following guiding principle: A thread is only dispatched on cores that are allocated to the thread's current stage. When a thread uses the system API to switch to a stage S, we choose the least-loaded core C among the cores allocated to S and enqueue

the switching thread into C's runqueue. When a thread blocks, it no longer counts toward the load of stage but does not lose the association to it. Thus, when a blocked thread is woken up again, the *waker* simply uses the current core allocation to choose a suitable core for the woken thread and enqueue the still-sleeping thread into that core's runqueue.

The promise behind the approach described above is the same as in computation spreading and the proof-of-concept implementation at the KIT OS group (Chapter 2): By dedicating CPU cores and hence their private caches to a stage and by scheduling threads exclusively on the cores of their current stages, the i-cache always contains the instruction working set of all threads in the CPU's runqueue. This reduces instruction cache misses, pipeline stalls and mispredicted branches, resulting in faster execution of the stage's code and cheaper context switches on the CPU.

Our solution is specific to certain types of server applications and thus not suitable as a general-purpose scheduling policy. Ideally, we would thus extend an existing scheduler such as the Linux *completely fair scheduler*. However, extending the Linux scheduler is out of scope of this thesis due to the expected design and implementation complexity. Instead, we implement our solution in the OSv library operating system, a small kernel that is bundled with an application into an appliance-like virtual machine image.

The remainder of this chapter presents our design and its implementation in detail: Section 4.1 gives an introduction to the OSv library operating system, providing the knowledge required to understand the implementation constraints we faced. We proceed with details on the user-space API illustrated with examples (Section 4.2), followed by the design of our thread migration mechanism (Section 4.3). In Section 4.4, we explain the details involved in implementing thread-migration on wake-up, which required significant refactoring of OSv's thread state tracking and timer implementation. Section 4.5 then presents the CPU core allocation policy. Where appropriate, we refer to the relevant commits in the Git repository of our modified version of OSv which can be obtained from the the appendix.

#### 4.1 The OSv Library Operating System

We implement our stage-aware scheduling solution in the OSv *library op*erating system, which breaks up the traditional divide between the kernel and applications: Traditionally, an operating system provides abstractions from the physical hardware and multiplexes it among *multiple* untrusting users and applications, providing protection and isolation at various levels. With the rise of hardware virtualization, it has become common practice to deploy a traditional OS running a *single* application in a virtual machine running on top of a hypervisor. In this situation, both the hypervisor and the guest kernel implement protection mechanisms, but because each VM only runs a single application, the protection efforts of the guest kernel may be considered duplicate. [Mad+13; KCE14]

OSv addresses this situation by delegating all resource abstraction and protection responsibilities to the hypervisor. It confines itself to providing a familiar execution environment for a single trust domain, providing facilities for multi-threading, scheduling, a network stack and filesystems. To run an application on OSv, it is bundled with the OSv kernel into a virtual machine image. When the VM starts, OSv establishes a single virtual address space and dynamically links the application against OSv's own C standard library, in which system calls are merely calls to OSv-internal functions. This technique allows dynamically linked applications built on Linux to execute unmodified on OSv, unless they depend on facilities intentionally not provided by OSv such as forking new processes. The single trust domain property furthermore allows omitting all privilege level switching between OSv and the application. In summary, the removed user-kernel-boundary and syscall overhead improves application performance significantly without any application code changes required. However, if application developers choose to specifically target OSv, more efficient system APIs provide further optimization, e.g., zero-copy networking as opposed to the traditional socket API. [KCE14]

Although OSv incorporates pre-existing components for ACPI, the filesystem and originally the network stack, the core system is implemented in C++11. The codebase of ca. 400000 lines of code is very small compared to the 20 million lines of Linux 4.13, which can be attributed to both the use of a more expressive programming language and the comfort of only providing device drivers for typical hypervisor-emulated devices and paravirtualization. The OSv scheduler in particular amounts to less than 3000 lines, making OSv particularly attractive for this thesis. [KCE14]

#### 4.1.1 The OSv Scheduler

The solution presented in this chapter must be implemented in the scheduler. To understand the design and implementation constraints we faced, this section gives a summary of the upstream OSv scheduler implementation.

The OSv developers state that the "thread scheduler [...] should be lock-free, preemptive, tick-less, fair, scalable and efficient." As such, it features CPU-local runqueues containing runnable threads, which are sorted in ascending order by the threads' recent average runtimes. Load-balancing is implemented by a periodically-invoked per-core load-balancer thread that migrates threads from its runqueue to other cores if these are less loaded. [KCE14]

OSv implements thread migration through a set of lock-free single-producersingle-consumer queues: Given N CPUs, each CPU has N incoming\_wakeup queues, one per source CPU, containing pointers to the TCBs of the threads being migrated. At every reschedule, a CPU then drains all incoming queues into its runqueue. Each CPU is guaranteed to have an always runnable idle thread that spins for a short time and halts the CPU if no other runnable threads are in the runqueue. Thus, a source CPU may need to send an interprocessor-interrupt (IPIs) to the target CPU after enqueuing the migrated thread. For this purpose, each CPU has a bitmask, each bit representing one source CPU / wake-up queue: The source CPU will atomically set its bit in the target CPU's bitmask and only send the IPI if the bit was not set before, avoiding unnecessary flooding the target CPU with IPIs. [Sys17; KCE14]

Migrating runnable but not currently running threads is easy in this model: The source CPU removes the runnable thread from its runqueue and puts it into the incoming queue of the target CPU. However, threads may also migrate themselves to another CPU while still running, for example through the pthread\_set\_affinity API. Let us call this case *synchronous thread migration*: In OSv, the migrating thread spawns a short-lived helper thread and immediately schedules out. The helper thread will then put the migrating thread's TCB into the correct incoming\_wakeup queue. [Sys17]

One complication of the above procedure are timers: Apart from CPU-local timers such as the preemption timer, a thread can program timers as well, for example for use with SIGALARM. Per CPU, a list of active timers is kept, sorted in ascending order by their expiration time. The OSv timer implementation then programs a single hardware-timer (clock\_event driver) such that it fires at the nearest expiration time. On x86-64, the CPU-local Advanced Programmable Interrupt Controller (LAPIC) timer is used for this

purpose. [SDM105] In the timer interrupt handler, the expired timers are removed from the sorted list and the LAPIC timer is reprogrammed. Threads whose timer fired are then woken, i.e., marked as runnable and put into the CPU's ready queue. It is crucial to observe that the upstream OSv timer abstraction does not allow a thread to have timers set on multiple CPUs: All data structures related to timer management are only protected by masking interrupts because they are only manipulated by the thread itself or from the timer interrupt context. For thread migration, this timer-locality means that timers must be removed from the source CPU's timer list before enqueuing the thread into the target CPU's incoming\_wakeup queue. On the target CPU, after adding the migrated timers to its timer list, the LAPIC may need to be reprogrammed if any of the migrated timers' expiration dates are earlier than the previous head of the list. [Sys17]

In addition to synchronous thread migration, upstream OSv also supports remote asynchronous thread migration, i.e., the situation where a thread  $T_i$  executing on CPU  $C_1$  initiates the migration of a thread  $T_m$  currently executing on a CPU  $C_2$  to CPU  $C_3$ . As outlined in the previous paragraph,  $T_m$ 's timers must be migrated, which can only be initiated from the source CPU itself. Upstream OSv only requires this feature for implementing pthread\_attr\_setaffinity\_np and uses a helper thread  $T_h$  that chases  $T_m$  until  $T_h$  can successfully mask all interrupts on the same CPU as  $T_m$  and suspend  $T_i$ 's timers. The remaining steps are the same as in synchronous thread migration. [Sys17]

#### 4.2 The Stage API

Our scheduling policy spreads an application's working set over the private caches of all available CPU cores by scheduling threads only on those cores that have its current stage's code in their private cache. We require developers to manually *stagify* their applications by defining stages and inserting switching calls into the request-handling code path. To facilitate adoption, our primary design goal for the stage API is to be non-invasive, allowing maintenance of private patches to an existing open source code base.

In OSv, we implement stages as a C++ class with public member functions for stage definition and switching. Without the syscall boundary, we can simply export the corresponding headers to the application, which receives pointers to the kernel objects representing stages and invokes methods on them. However, applications for OSv must be built on the Linux host where

```

#include <osv/stagesched.h>

stage *s_net, *s_ser, *s_db;

int main() {

s net = stage::define("net");

s ser = stage::define("serialization");

s db = stage::define("db");

// start threads ...

}

void request handler(database db, net::conn c) {

s net->enqueue();

buf b = c.recv();

s\_ser->enqueue();

req req = sql::parse(b);

s db->enqueue();

response resp = db.handle request(req);

s ser—>enqueue();

buf b = sql::respond(resp);

s net->enqueue();

c.send(b);

}

```

Figure 4.1: Example for a stagified application using the stage API in pseudo C++. Because we implement our solution in OSv, we can simply use pointers to the kernel objects representing stages.

the stage API header and implementation are not available. To avoid build and linker failures, we provide a no-op implementation of the API as a shared library, enabling us to produce application binaries that work on both Linux and OSv.<sup>1</sup> Figure 4.1 gives an impression of how the stage API could be used in an existing application.

In addition to the direct invocation of the switching API, we provide a datastructure similar to C++11 lock guards: Following the *resource acquisition is initialization* (RAII) paradigm, the structure allows switching to a stage for the lifetime of a block and to automatically switch back to the previous stage when the guard object goes out of scope. The guard objects can also be used to shift the responsibility of switching stages from the function caller to the callee, which is particularly useful when a piece of code is large enough to

<sup>&</sup>lt;sup>1</sup>The OSv linker ignores missing libraries, and the app does not crash because the OSv implementation of the stage class provides the required functions.

have its own stage but is called from more than one other stage. Figure 4.2 shows how the above example looks like with the RAII-style API.

The commits in the Git repository corresponding to the changes presented in this section are 439b5501 and 9eaf3a8b.

## 4.3 Fast Thread Migration

Once an application has been stagified by the application developer, our solution must act on the stage switching calls made during request handling. Specifically, we must find a core whose private caches contain the next stage's code and migrate the calling thread to that core. We defer discussion of the core allocation policy to Section 4.5 and focus on the migration mechanism for now.

For a net benefit from spreading the instruction working set, the performance gained through always warm i-caches must outweigh the cost of thread migration. One significant contributor to the latter is migration latency, which is the reason why we require a low-latency mechanism. Upstream OSv's uses short-lived helper-threads for synchronous thread migration and interprocessor interrupts (IPIs) to notify the target CPU about incoming migrations. The IPIs are necessary because the target CPU may be temporarily halted in the idle thread. We state that the upstream mechanism is unsuitable for our use-case of frequent stage-switching: At first, recent measurements on AMD systems have shown that IPI propagation on bare-metal systems is 1700ns. For OSv, we assume significant overhead due to virtualization, which we will further investigate in Section 5.4.2. The IPI propagation time puts a lower bound on the achievable migration latency but additionally, the impact of IPIs on the target CPU's pipeline must be considered: An arriving interrupt will flush the pipeline or at least obsolete the instructions it currently executes. [She13] At last, on the source CPU, the use of helper threads implies memory allocation for the new TCB and an invocation of the OSv scheduler, which does not run in constant time.

As a consequence of the above, we choose to implement a lowerlatency alternative for thread migration that neither uses IPIs nor helper threads: When a thread switches to another stage, the switching thread queries the core allocation policy for a target CPU that has the target stage's code in its private caches. The thread then puts its TCB into the *incoming migrations queue* of the target CPU while running and subsequently

```

#include <osv/stagesched.h>

class thread {

stage stack stagestack;

. . .

};

stage *s net, *s ser, *s db;

int main() {

s net = stage::define("net");

s ser = stage::define("serialization");

s_db = stage::define("db");

// start threads ...

}

void thread::request handler(database db, net::conn c) {

buf b = c.recv();

req rq = sql::parse(b);

response rs = db.handle request(rq);

buf b = sql::respond(rs);

c.send(b);

}

// Use stage_stack::guard in all functions

req sql::parse(buf& b) {

stage stack::guard g(thread::current()->stagestack, s ser);

. . .

}

```

Figure 4.2: stage\_stack keeps previous stages in a stack. The stage\_stack::guard constructor pushes the stage pointer onto the stage\_stack and switches to the stage. The corresponding destructor pops the current stage's pointer from the stack and switches back to the previous stage.

schedules out. The target CPU's reschedule routine and its idle thread eventually dequeue the TCB pointer from the incoming migrations queue into the runqueue, thereby completing the migration.

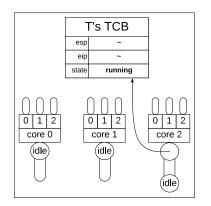

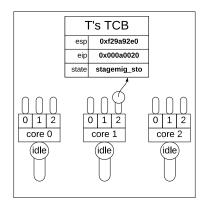

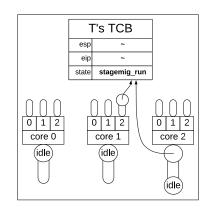

Although the above paragraph gives a good overview of our mechanism, we omitted two important details: First, there is a race condition between the point where a migrating thread T puts its TCB pointer into the incoming migrations queue and the point at which it schedules out: If the target CPU dequeues T's TCB before T has scheduled out, the TCB contains will invalid register state or the state from the last time T scheduled out. If T now starts running on the target CPU, we have the hazardous situation of T running on both CPUs simultaneously, primarily visible through a corrupted stack. We solve this problem by representing the stage-switch as a *two-step* thread state transition, visualized in Figure 4.3: Before the migrating thread puts its TCB into the target CPU's incoming migrations queue, it sets its state to stagemig run. The target CPU will not put threads in that state into its runqueue but instead enqueue it back into the incoming migrations queue because the migration is not yet finished. On the source CPU, after T has scheduled out, we then set T's state to  $stagemig_sto$ . Eventually, the target CPU will dequeue T again, observe from its state that it is not running anymore and enqueue it into its runqueue.

The other issue we face with our migration mechanism is that in upstream OSv, the idle thread halts CPUs using the HLT instruction. This works in upstream due to the use of IPIs which wake the CPU up again, but we want to avoid IPIs in our solution and therefore provide two boot-time configurable alternatives: First, the idle thread can busy-wait for changes to the incoming migrations queue. Alternatively, it can use the MONITOR and MWAIT instructions to wait for changes to the queue while keeping the core in a low power state. Both options have benefits and downsides: Busy-waiting offers 16% lower migration latency (see Section 5.4.2) but consumes more power, which is undesirable for technical (dark silicon), economical (increased cost) and ecological reasons. MWAIT in combination with *simultaneous multithread-ing* (SMT) in contrast allows the core to switch to another hardware thread, which also opens a window for increased performance. [SDM810; Har+11] Neither of the alternatives cause an exit to the hypervisor, to which the VM will appear 100% busy.

At last, we want to provide some implementation details that we omitted for easier understanding of the design: We implemented above mechanism in the early course of this thesis with a limited understanding of the upstream OSv migration mechanism. Therefore, instead of replacing the upstream

(a) T is running on core2 and wants to migrate to core1.

(c) T schedules out. The context switching routine sets its state to stagemig\_sto after T has stopped running on core2.

(b) T switches to stagemig\_run and puts a pointer to its TCB into the incoming migrations queue at core1. Core1's idle thread does not dequeue TCBs with state  $\neq$  stagemig\_sto.

(d) The idle thread on core1 observes T in state stagemig\_sto and admits it to the ready queue.

(e) T starts executing on the core1.

Figure 4.3: Fast thread migration without helper threads.

mechanism and extending the OSv scheduler's incoming\_wakeups dequeuing routine, we implemented above solution as a supplement. As such, in our implementation, the *incoming migrations queue* referred to above is different from the incoming\_wakeups queues from Section 4.1.1: We currently use a lock-free multi-producer-single-consumer queue which we originally used to poll for changes in the idle thread. The addition of MWAIT however required waiting for changes to the upstream incoming wake-ups queue and our queue simultaneously. We solved this problem by also setting upstream mechanism's bitmask from the stage-switching code path and by using MWAIT on its address. Combined with the changes we present in the next Section, we want to merge the two mechanisms in the future, thereby de-duplicating the dequeuing code in the idle thread.

The commits in the Git repository corresponding to this section are 439b5501 and f00b5872.

## 4.4 Thread Migration on Wake-Up

In Chapter 3, we analyzed that the proof-of-concept implementation in Linux at the KIT OS group is not work conserving: It only allows thread migration to be initiated from user-space and thus prohibits migrating threads to idle cores at the time the thread unblocks. In contrast, our solution models stages explicitly and tracks a thread's association with its current stage in the thread's TCB. Utilizing all cores of a multi-core system is thus trivial in theory: When a blocked thread is woken up, we find a CPU that has that thread's current stage's code in its cache and enqueue the woken-up thread's TCB into that CPU's runqueue.

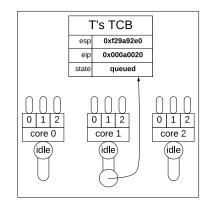

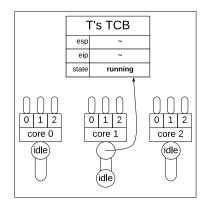

However, in practice, this simple concept is complicated by the realities of the OSv scheduler implementation. Let us first look at the wake-up-related state transitions that a thread might go through in upstream OSv, as depicted in Figure 4.4: The most common case will be that a thread goes to sleep, waiting for some predicate to become true, for example that a timer has expired or that it acquired a mutex. The *running* thread will then transition synchronously to the *waiting* state and schedule out. Let us now imagine that another thread makes the predicate become true. That *waker* knows the threads waiting for this condition and wakes them using the wake() function, which puts the woken thread's TCBs into their last core's incoming\_wakeups, which is in turn eventually drained into the core's runqueue.

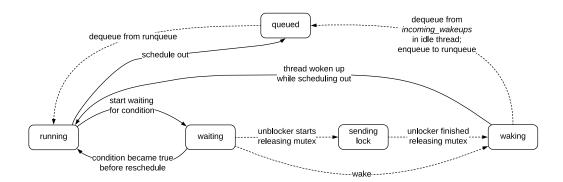

Figure 4.4: Upstream OSv wake-up-related thread state transitions: States *waiting*, *sending\_lock* and *waking* are ambiguous with regard to whether the thread is still scheduling out whether it has fully stopped executing. Dashed lines represent events asynchronous to thread execution, solid lines represent synchronous events.

The crucial observation in this section is that the corresponding **OSv thread** states do not precisely encode whether the a thread has stopped executing. In fact, only threads in state queued are guaranteed to be stopped and only threads in state running are guaranteed to be running. The remaining waiting, sending\_lock and waking states are ambiguous: In each of these states, the thread can either have completed scheduling out or it can still be on the way to do that. In the latter case, the thread may even observe that it has already been woken up again by some other thread and move itself from waking back to running.

Upstream OSv can afford the ambiguous state representation because its wake-up mechanism is limited to ensuring that the woken thread is made runnable again on its current CPU. Our solution however requires precise knowledge of whether the woken thread is still running or whether it has actually stopped executing on its current CPU. In the former case, we do not want to migrate it because its current CPU still has a hot cache. However, in the far more common case of waking up a stopped thread, we want to use the opportunity for load balancing, thereby maximizing CPU resource usage: Among the cores that have the to-be-woken thread's stage's instruction working set in their private cache, the least loaded core is chosen as a migration target. And because the woken-thread is not running at the time of wake-up, we can implement remote asynchronous thread migration that works without a chasing helper thread.

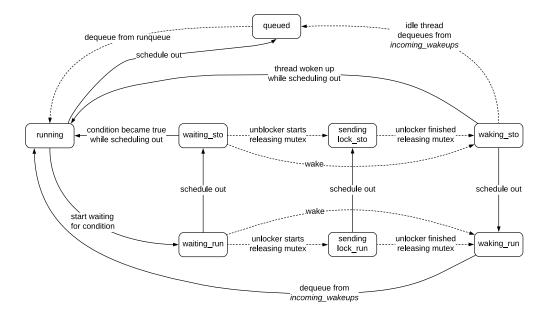

Figure 4.5: Modified OSv wake-up-related thread state transitions: All states are unambiguous about whether the thread is still running or completed scheduling out. Dashed lines represent events asynchronous to thread execution, solid lines represent synchronous events.

The first pillar of our work-conserving scheduler implementation is therefore a significant refactoring of the OSv thread states, the result being depicted in Figure 4.5. As we already did with the *stagemig\_run* and *stagemig\_sto* states in Section 4.3, we spread the three *waiting*, *sending\_lock* and *waking* states into  $\star$ \_*run* and  $\star$ \_*sto* sub-states; the the former suffix represents a still-running thread whereas the latter represents a stopped thread. The **context switching routine then implements the switch from**  $\star$ \_*run* **to**  $\star$ \_*sto* **after saving the register state of the thread to its TCB.<sup>2</sup> An asynchronous waker can thus always distinguish between running and stopped threads.**

With the refactoring of the thread states done, we can now discuss our faster alternative for remote asynchronous thread migration. Let us recall some details on upstream OSv from Section 4.1.1:

(a) The waker may run on another CPU than the woken-up thread.

$<sup>^{2}</sup>$ The implementation in the context switching routine is a generalization of the two-step migration mechanism presented in Section 4.3.

#### 4.4. THREAD MIGRATION ON WAKE-UP

- (b) The timer implementation requires all timers of a thread to be in the timer list of one CPU.

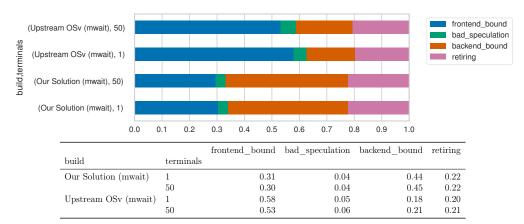

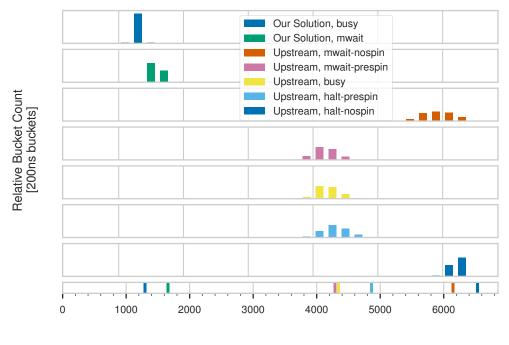

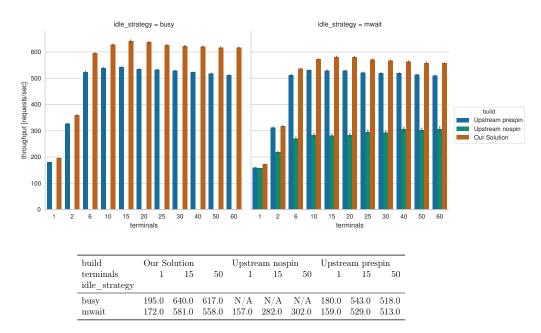

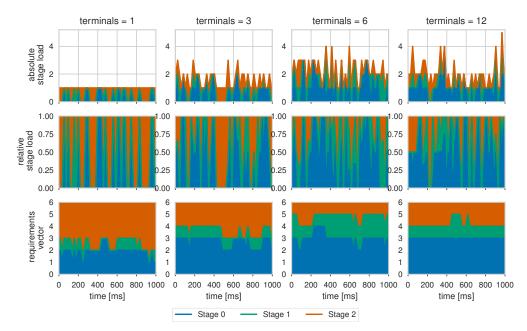

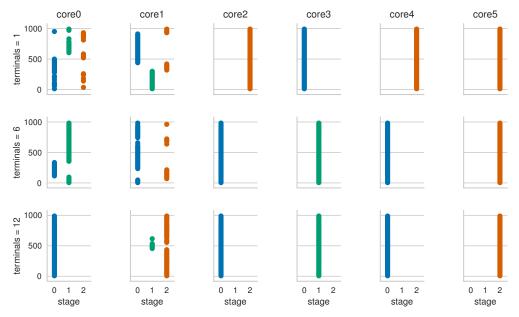

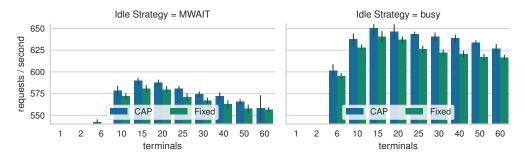

- (c) Remote asynchronous thread migration relies on a short-lived helper thread that chases the to-be-migrated thread and eventually performs the same steps required for synchronous thread migration in the name of the to-be-migrated thread.