# On Statistical Properties of Duplicate Memory Pages

Diplomarbeit von

# cand. inform. Thorsten Gröninger

an der Fakultät für Informatik

Erstgutachter: Zweitgutachter: Betreuender Mitarbeiter: Prof. Dr. Frank Bellosa Prof. Dr. Hartmut Prautzsch Dipl.-Inform. Marc Rittinghaus Dipl.-Inform. Konrad Miller

Bearbeitungszeit: 1. Mai 2013 – 31. Oktober 2013

## Abstract

In this work, we investigate the possibility to make memory deduplication scanners more efficient. Modern memory scanners equipped with hinting mechanisms merge large amounts of duplicate memory pages originating from disk, but still lack to harvest other replicas equally fast. We analyzed the properties of this remaining sharing potential and aim to decrease the amount of scanned pages by directly focusing memory scanners to stable page content. Stability is necessary to share content, or otherwise the sharing is instantly broken. With a metric to exclude unstable pages, it is possible to speed up merging.

We acquired memory modifications and semantic information with a fullsystem simulation to analyze sharing opportunities, memory access frequencies, and access patterns which lead to stable pages. We implemented a toolchain that allows to gather such information quickly and scalably. Our evaluation shows that up to 89% of all pages are stable and can be shared with other VMs executing the identical file benchmark. Furthermore, a heuristic for CPU or I/O bound workloads can only exist for a small sub-set of examined workloads, e.g., kernel builds. General page state prediction seems impossible.

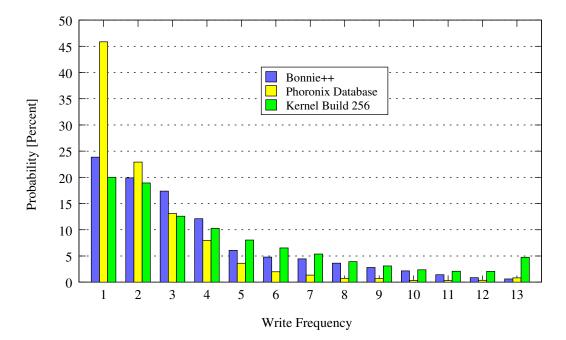

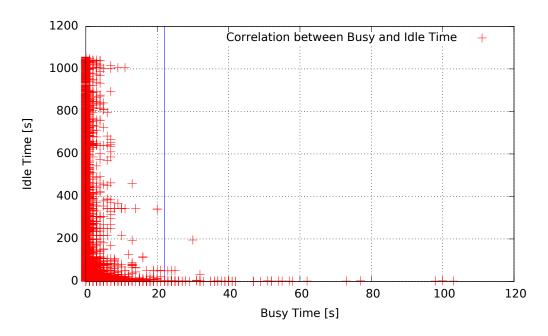

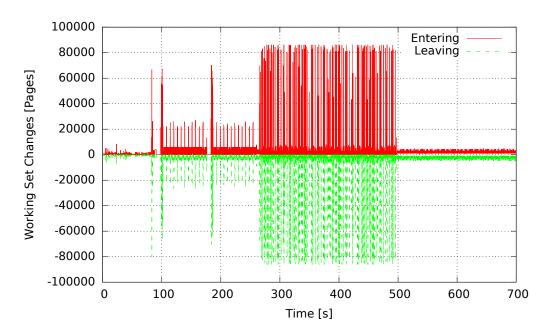

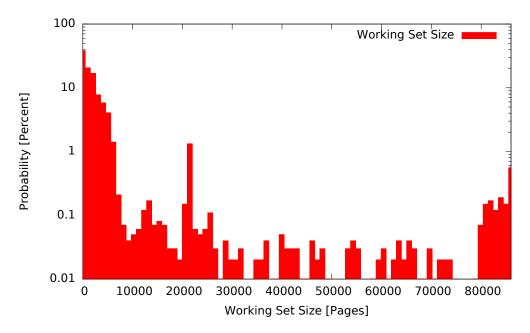

Our findings show that memory write frequencies correlate with page stability, even in otherwise unpredictable workloads. About 78% of all pages experience a low access frequency before they stabilize. A memory scanner should therefore prioritize pages that show a low write access frequency. A reasonable threshold appears to be about 4 accesses within a window of 1.5 seconds. Pages with high memory access frequencies such as device associated page frames can be excluded permanently from scans, if their overall busy time exceeds 15 seconds. We further conclude that a scanner should focus on pages leaving the write working set instead of linear scanning all pages. These pages (on average about 1,800 pages per 480 ms) are guaranteed to have been recently modified, but are not currently written and are thus candidates for further examination by a scanner.

I hereby declare that this thesis is my own original work which I created without illegitimate help by others, that I have not used any other sources or resources than the ones indicated and that due acknowledgment is given where reference is made to the work of others.

Thorsten Gröninger Karlsruhe, October 31th 2013

### **Deutsche Zusammenfassung**

Heutige Computersysteme werden mit immer mehr Arbeitsspeicher ausgestattet, allerdings wächst gleichzeitig auch der Speicherbedarf durch Virtualisierung, In-Memory Datenbanken und Cloud Computing. Obwohl Speicher erschwinglich erscheint, bleibt er (zu einem gewissen Grad) eine begrenzte Ressource. Insbesondere Virtualisierung erzeugt redundante Daten; große Teile des physischen Speichers enthalten identische Inhalte und könnten eigentlich dedupliziert werden. Allerdings sind die heute verfügbaren Deduplikationslösungen für Arbeitsspeicher nur eingeschränkt nutzbar. Zum einen benötigen sie speziell angepasste Betriebssysteme, Virtualisierungslösungen und Programme. Zum anderen verbrauchen sie sehr viel Rechenleistung um redundante Speicherseiten zu finden und zusammenzulegen, dieser Vorgang kann durch verschiedene Ansätze verbessert werden.

XLH (Cross Layer Hints) [35] benutzt den in Linux verfügbaren Deduplikationsmechanismus und kombiniert ihn mit Informationen aus dem virtuellen Dateisystem um schneller den Speicherverbrauch einer virtuellen Maschine zu reduzieren. Verschiedenste empirische Untersuchungen [9, 35, 36] haben gezeigt wie erfolgreich Speicherseiten, deren Inhalt von der Festplatte geladen wurden, dedupliziert werden können. Allerdings müssen die anderen Speicherseiten, z.B. anonymer Gastspeicher, immer noch linear durchsucht werden. Große Teile des theoretisch teilbaren Speichers bleiben unberücksichtigt oder werden nur sehr langsam zusammengelegt, dies sind, abhängig von den jeweils ausgeführten Programmen, bis zu 50% aller theoretisch teilbaren Speicherseiten.

Diese Arbeit beschäftigt sich mit diesem ungenutzten Deduplikationspotential, dessen Eigenschaften und Verbesserungsmöglichkeiten für Memory Scanner. Wir untersuchen das Potential von duplizierten Speicherseiten, ihre Stabilität und Speicherzugriffsmuster die zu (in-)stabilen Seiten führen, um jene zeitweise oder dauerhaft von einem Scan auszuschließen.

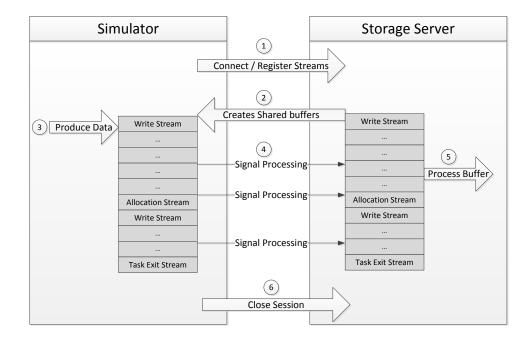

Um eine tiefergehende Untersuchung dieser Speicherseiten durchzuführen, wurden die entsprechenden Daten, z.B. alle Speicherzugriffe, aufgezeichnet. Hierfür wurde ein Systemsimulator verwendet, um eine ungewollte Beeinflussung der ausgeführten Benchmarks auszuschließen. Dieser simuliert Hardware auf der unmodifizierte Betriebssysteme ausgeführt werden können, erlaubt somit auch alle Speicherzugriffe transparent zu unterbrechen und aufzuzeichnen. Für diese Arbeit wurde eine Version des freien, quelloffenen Simulators QEMU verwendet, der um die benötigten Schnittstellen erweitert wurde. Da eine Simulation um mindestens zwei Größenordnungen langsamer läuft als ein reales System, haben wir die Aufzeichnung der Daten von der Analyse getrennt. Die Speicherzugriffe und die semantischen Informationen innerhalb des Betriebssystems werden erfasst, über einen Speicherserver komprimiert und für die spätere Verwendung abgelegt. Unsere Analysen nutzen die aufgezeichneten Daten und rekonstruieren ein Speicherabbild für die eigentliche Duplikatsanalyse. Diese wird wiederum mit semantischen Informationen aus dem untersuchten Linuxkern ergänzt. Dieses Vorgehen ermöglicht eine verfälschungsfreie Untersuchung des noch nicht genutzten Deduplikationspotentials, auch unter Einbeziehung der eigentlichen Verwendung einer Speicherseite innerhalb des Betriebssystems.

Unsere Untersuchungen bestätigen das Potential, das in Speicherseiten steckt, die von der Festplatte eingelesen wurden. Gleichzeitig zeigen sie aber auch die Abhängigkeit von den ausgeführten Programmen, z.B. können Datenbankanwendungen, die häufig ihre Daten modifizieren und zurück auf den Hintergrundspeicher schreiben, nur im geringeren Umfang davon profitieren. Das verbleibende Deduplikationspotential, das nicht vom Hintergrundspeicher stammt, ist noch wesentlich instabiler und variiert stark bei unterschiedlichen Anwendungen, z.B. verursachen Simulationen, wie sie in der Physik Anwendung finden, große Mengen an identischen Speicherseiten. Allerdings verändern sich diese derartig schnell, dass selbst ein spezialisierter Speicherscanner nicht in der Lage ist diese Seiten zu vereinen.

Ein Speicherscanner sollte sich allerdings die Tatsache zu Nutze machen, dass Speicherseiten unterschiedlich oft beschrieben werden und cache-affine Programme nur überschaubar viele Speicherseiten in einem Zeitinterval ändern. Die meisten von uns untersuchten Anwendungen ändern im Mittel ungefähr 1.850 Seiten (7,25 MiB) innerhalb einer halben Sekunde. Dieser modifizierte Arbeitsbereich kann von einem Scanner leichter bewältigt werden, als den gesamten Arbeitsspeicher regelmäßig eines aufwendigen Vergleichs zu unterziehen.

Mit der gleichen Methode wie sich das Working Set ermitteln lässt, können auch Speicherzugriffsfrequenzen ermittelt werden. Unsere Untersuchung zeigt, dass Seiten die stabil werden, also ihren Inhalt für ein gewisses Zeitfenster nicht ändern, in über 80% aller Fälle bereits vorher eine sehr niedrige Zugriffsfrequenz hatten. Leider reicht es nicht aus die Stabilität einer Speicherseite zu ermitteln, um direkt auf einen Kandidaten zur Deduplizierung zu schließen, dies gilt nur für Dateien die von einem identischen Festplattenabbild geladen wurden. Allerdings erweist sich Stabilität als sehr wichtig, denn sie stellt sicher, dass eine Seite nicht direkt nach dem Zusammenlegen wieder kopiert werden muss und so unnötige Rechenleistung vergeudet wird. Im Laufe unserer Untersuchungen hat sich des Weiteren gezeigt, dass ein Memory Scanner, ungeeignete Speicherbereiche, die für Kernelstacks oder Geräte verwendet werden, dauerhaft von einem Scan ausschließen sollte, da diese Seiten sich häufig ändern und keine ausreichende Stabilität zeigen, um sie gegebenenfalls zu deduplizieren.

Wir haben festgestellt, dass die einzige nutzbare Eigenschaft von redundaten Speicherseiten ihre Stabilität ist. Allerdings lässt sich trotzdem nicht allgemein sagen, ob sich stabile Speicherseiten in Zukunft zusammenlegen lassen.

# Contents

| Ab | Abstract i                    |                                 |    |  |  |  |

|----|-------------------------------|---------------------------------|----|--|--|--|

| De | Deutsche Zusammenfassung v    |                                 |    |  |  |  |

| 1  | Intro                         | oduction                        | 1  |  |  |  |

| 2  | 2 Background and Related Work |                                 |    |  |  |  |

|    | 2.1                           | Memory Deduplication Techniques | 5  |  |  |  |

|    | 2.2                           | Duplicate Memory Content        | 13 |  |  |  |

|    | 2.3                           | Full-System Simulation          | 14 |  |  |  |

| 3  | Analysis 23                   |                                 |    |  |  |  |

|    | 3.1                           | Analyzing Sharing Opportunities | 24 |  |  |  |

|    | 3.2                           | Required Analysis Data          | 26 |  |  |  |

|    | 3.3                           | Data Acquisition                | 27 |  |  |  |

|    | 3.4                           | Simulation                      | 31 |  |  |  |

|    | 3.5                           | Conclusion                      | 33 |  |  |  |

| 4  | Desi                          | gn                              | 35 |  |  |  |

|    | 4.1                           | General Design                  | 36 |  |  |  |

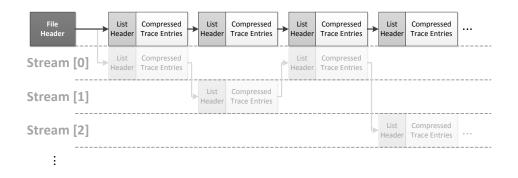

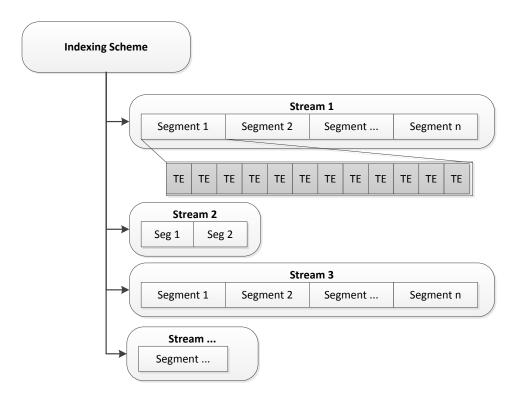

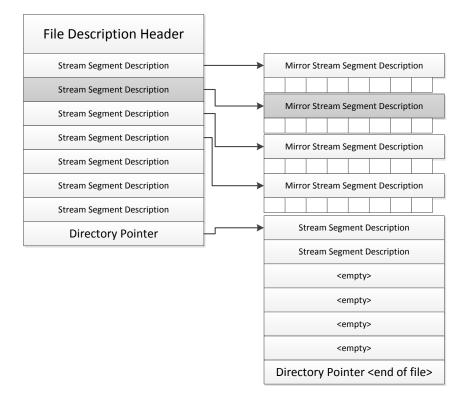

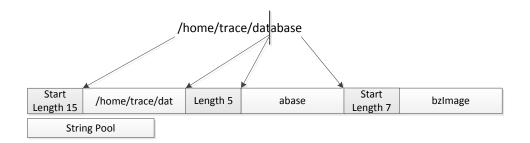

|    | 4.2                           | Trace Organization and Storage  | 37 |  |  |  |

|    | 4.3                           | Conclusion                      | 42 |  |  |  |

| 5  | Implementation 43             |                                 |    |  |  |  |

|    | 5.1                           | QEMU Modifications              | 43 |  |  |  |

|    | 5.2                           | Storage Server                  | 52 |  |  |  |

|    | 5.3                           | Trace Data Processing           | 57 |  |  |  |

|    | 5.4                           | Conclusion                      | 63 |  |  |  |

| 6  | Eval                          | uation                          | 65 |  |  |  |

|    | 6.1                           | Methodology                     | 65 |  |  |  |

|    | 6.2                           | Evaluation Setup                | 68 |  |  |  |

#### CONTENTS

|          | 6.3              | Benchmark Evaluation    | 72 |  |  |

|----------|------------------|-------------------------|----|--|--|

|          | 6.4              | Sharing Opportunities   | 75 |  |  |

|          | 6.5              | Memory Access Analysis  | 78 |  |  |

|          | 6.6              | Semantics and Stability | 81 |  |  |

|          | 6.7              | Write Working Set       | 88 |  |  |

|          | 6.8              | Conclusion              | 90 |  |  |

| 7        | Conc             | lusion                  | 93 |  |  |

|          | 7.1              | Future Work             | 94 |  |  |

| Appendix |                  |                         |    |  |  |

| Bił      | Bibliography 104 |                         |    |  |  |

|          |                  |                         |    |  |  |

Х

# Chapter 1 Introduction

The demand for main memory is increasing every year. In-memory databases and virtualization push the demand for memory even further. As virtualization has become widely used in cloud computing, memory consumption and data redundancies have reached a high level, for example, up to 79% [11] of data is redundant in such scenarios.

Although main memory is not a rare resource in most server systems, it still can be used for more *virtual machines* (VMs) than holding replicated data. The only justifiable redundancies are found on different *non-uniform memory access* (NUMA) nodes, where memory access comes at different costs and a local copy increases performance. In other cases, memory footprints of VMs and applications can be reduced by using memory deduplication techniques.

There are two different kinds of deduplication mechanisms. Firstly, systems that try to prevent the replication of data by proactively establishing shared pages instead of copying content. Widely used techniques are shared libraries and forking with *copy-on-write* (COW), or in a virtualized environment: VM forking [27]. Secondly, deduplication systems actively search all pages, identify replicated content and merge them to a single copy. This method is called memory scanning.

Memory scanning reduces the memory footprint of applications and VMs by detecting identical memory content on page granularity and remapping them to a single copy-on-write page. A recent empirical study shows that the amount of redundant data ranges from 11% up to 79% [11]. If this sharing potential can be harvested, the reduced memory footprint allows more VM instances to run in parallel. Furthermore, the CPU cache utilization and its hit ratio increases [41] and thus allows faster program execution.

Although, the sharing potential is already harvested by different deduplication approaches, there is still room for improvement. Even the most promising techniques, for example, Cross Layer Hints (XLH), still fail to fetch about 50% of theoretically shareable content in some workloads [35]. XLH uses hints from the I/O layer of the hosting OS and focuses its memory scan on pages originating from file operations. Although, these hints speed up deduplication for page cache pages in different VMs, other sharing opportunities must still be collected through periodical linear memory scanning.

#### **Objectives**

This thesis focuses on properties of unharvested sharing potential and tries to find new hinting sources to improve scanner based memory deduplication. We examine options to focus scanners on promising memory regions and determine memory pages that can be excluded from the scan.

The effectiveness and efficiency of a scanner depends on the stability of scanned and merged pages, we clarify the relations between semantics and stability.

#### Contributions

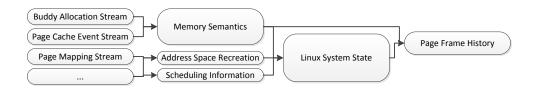

To analyze sharing opportunities and to identify new hinting sources, we collect memory modifications and semantic information from within a guest operating system (OS). We regard memory operations, trace OS page frame allocations, and the OS system state without influencing the guest OS by using a full-system simulator for our experiments. A simulator does not only hide memory inspection overhead from the guest OS, it is also the only feasible method to collect all memory modifications. Therefore, we augmented a simulator to allow flexible and fast recording of memory accesses and semantic information, store them efficiently, and replay memory modifications to reconstruct memory content for every point in time. We were able to perform false positive free sharing analyses, memory access frequency and pattern measurement, and enriched these data with semantic information.

Our evaluation is based on data acquired with the fast, open-source simulator QEMU and analyzed with an adapted framework of a previous research project [41]. To cover a wide-range of different use-case scenarios, we evaluated I/O-, CPU- and memory bound workloads, and a mixture of realistic database and filesystem benchmarks.

Our findings show that memory write frequencies correlate with page stability, even in otherwise unpredictable workloads. About 78% of all pages experience a low access frequency before they stabilize. A memory scanner should therefore prioritize pages that show a low write access frequency. A reasonable threshold appears to be about 4 accesses within a window of 1.5 seconds. Pages with high memory access frequencies such as device associated page frames can be excluded

permanently from scans, if their overall busy time exceeds 15 seconds. We further conclude that a scanner should focus on pages leaving the write working set instead of linear scanning all pages. These pages (on average about 1,800 pages per 480 ms) are guaranteed to have been recently modified, but are not currently written and are thus candidates for further examination by a scanner. Memory access patterns, however, do not show any predictability for sharing opportunities or at least stability. In contrary they mispredict the future development of pages and are often beaten by normal distributed random numbers. Fine-grained predictions, based on a hidden Markov model, which show good prediction rates for file deduplication, suggest that memory stability can only be predicted for each workload individually.

### Organization

The thesis is structured as follows. In Chapter 2 we describe memory deduplication techniques and recent memory deduplication systems, and introduce fullsystem simulation. In Chapter 3 we discuss our analysis objectives and define the data required for these analyses. Our design is presented in Chapter 4 followed by the description of our implementation in Chapter 5. The results of our evaluation can be found in Chapter 6 followed by our conclusion and future work in Chapter 7.

## Chapter 2

## **Background and Related Work**

Memory is a valuable resource and the demand for memory is increasing as more data is continuously produced and stored. Virtualization in conjunction with cloud computing, in-memory databases, and big data increase the demand for memory. Deduplication of files is a common technique for efficient background storage devices [32]. Similar techniques can be applied to main memory as well.

This chapter presents an overview of memory deduplication techniques, from early memory sharing approaches (*forking*), to the latest developments and improvements for VMs (*Cross Layer Hints*), and native applications (*Page Combining*). Additionally, this chapter gives an introduction to full-system simulation, its fundamental modes of operation (*binary translation*), and different simulation modes (*functional* and *micro-architectural*). It provides an overview of recent simulators, e.g., *Quick Emulator* (QEMU).

### 2.1 Memory Deduplication Techniques

Many techniques have been developed to reduce memory footprints of applications, *virtual machines* (VMs), or complete systems.

The overall sharing potential varies with the *operating system* (OS) and the executed workloads. It further depends on the mixture of workloads executed in different VMs. These redundancies vary from 11% to 79% [4, 11, 26] of all pages, considered for sharing.

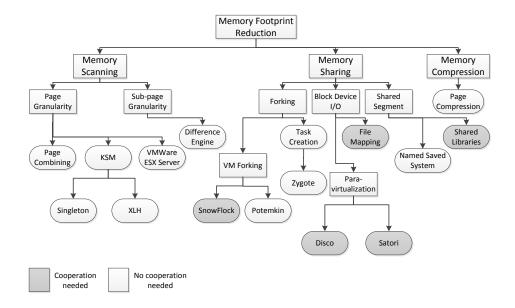

Figure 2.1 presents an overview and relations between the different approaches to reduce memory footprints. We differentiate between two categories of deduplication. In the first category, a VM or application is aware of the deduplication, and must be modified, and therefore *cooperate*, to benefit from deduplication, e.g., a paravirtualized OS. In the second category, deduplication can be applied without any cooperation and therefore tasks and VMs can benefit.

Figure 2.1: Overview and relations of memory footprint reduction techniques.

*Memory deduplication* aims to reduce the amount of consumed physical memory in two ways. Firstly, memory sharing, such system prevents the replication of data to different page frames proactively, i.e., it establishes shared pages instead of copying the content. Secondly, memory scanning, already replicated data is identified and merged re-actively to a single copy. Both methods reduce the memory redundancy. The amount of computational power of both approaches diverge: Where proactive mechanisms typically consume less CPU resources as re-active ones.

#### **2.1.1** Conventional Approaches

Virtual memory was invented in the 1950s and became available for commercial computers during the late 1970s. The virtualization of address spaces isolates programs from each other, allows paging content to disk, to increase the amount of available memory, and simplifies programming [29]. However, it also consumes more physical memory, since parts of programs have to be kept in redundant copies, compared to a single address space. As physical memory was much more limited than today, the first ideas of deduplication were invented, e.g., forking with copy-on-write to share memory content.

Traditional approaches contain two categories of proactive sharing. Firstly, *semantic sharing*, which considers libraries and files and secondly, *forking*.

**Semantic sharing** An OS can benefit from shared libraries, as an application only must be linked dynamically. The operating system's binary loader can map libraries into every address space, but must only retain a single copy in physical memory. Sharing is possible at per library granularity. Slightly different versions require an extra copy of all library associated pages, although only few pages might have changed. (Although different instances of such applications can still share their executable image.)

The idea of sharing libraries can be extended to all files. Commodity OSes provide mechanisms, e.g., file caches, for this purpose, but as for shared libraries, the application must explicitly use the file mapping mechanisms. Applications cannot rely on standard file APIs, or the standard C library, which make private copies into supplied buffers, rather than mapping the file's content into its address space. Afterwards two identical copies occupy memory, one in the address space and one in the file cache of the OS. These issues and the impossibility of sharing memory not backed by files (*anonymous memory*) with child processes led to the idea of *forking with copy-on-write semantic* [45].

**Forking** The process creation on POSIX-compatible operating systems invokes the fork system-call, which makes a shallow copy of the calling process' *virtual address space* (VAS). After this call, two identical virtual address spaces exist, sharing all content [45]. Both page tables point to the same physical memory, but to retain address space isolation all pages are marked as *copy-on-write* (COW). The OS creates a private copy of COW pages, if a write access occurs. That allows tasks to work without modification. However, as long as a identical task continues to execute inside the VAS, large parts of memory remain shared and only few pages, typically on the stack and heap, are copied.

#### 2.1.2 Initial Sharing Across Domains

The traditional deduplication techniques rely on relations between objects, such as libraries and files. This information is not available from outside hardwareaccelerated VMs without guest modifications. A VM forms an *isolation domain* with an independent system state, which separates the guests from its host. Therefore, the *virtual machine monitor* (VMM) lacks semantic information about memory allocations or open files within the guest operating system. It might not even be able to distinguish files on the used *virtual disk image* (VDI). As a result the traditional techniques cannot be applied to non-paravirtualized VMs, and new content deduplication schemes are necessary to deal with this situation. **VM Cloning** VM cloning was first implemented in Potemkin [51]. It leverages the same concept for VMs as the traditional fork for standard processes. Instead of allocating and booting a new VM. Potemkin creates an identical copy of an already running – *pre-warmed* – VM. This way, the virtual machines can share large parts of their allocated memory, e.g., the operating system kernel image. VM cloning, as done by Potemkin, allows a fast instantiation of VMs and overcommitting of physical memory. Although the primary intention was malware analysis in *honey pot* server farms, it has influenced cloud computing and other hypervisors.

Snowflock [27] extends this approach and includes a hypercall interface so every VM can signal the need of more resources or a further instance to cope with, e.g., incoming connections in a virtual server environment. The hypervisor can create a shallow copy of the VM, sharing most of their associated pages and keeping the memory consumption low.

The most prominent use of VM forking is the Zygote process of Android [8]. Since Android needs to run on energy and memory limited devices, it has to preserve resources whenever possible. To prevent content duplication, the DalvikVM, the Java runtime environment of Android, is hosted inside the *Zygote process* and forked on demand. This pre-warmed VM has already produced its common data structures and mapped all necessary libraries and resource files into its virtual address space. Thus, a fork enables a newly started application to share nearly all pages and the contained resources with its parent. Only few and typically fast changing pages are private to each process; in the case of the DalvikVM, the runtime generated code, as well as, heap and stack pages diverge.

**Named Saved System (NSS)** A different approach available on IBM's System Z are *Named Saved Systems* (NSS) [22]. NSS are similar to shared libraries. A NSS contains an OS binary image and the hypervisor maps it during VM initialization into the guest memory. These segments are shared across a large amount of VMs, with only one backing copy in memory. A *Discontinuous Saved Segment* (DCSS) [21] can also contain more shareable memory regions, e.g., parts of an already booted VM, which is instantiated and reinitialized by the z/VM hypervisor, allowing cloned, pre-warmed VMs with content sharing.

**In-place Execution** A slightly different concept available for Linux on System Z, is *In-place execution* [21]. Originally designed for embedded systems with limited RAM, it allows different VMs to load executable files from background storage without copying the content into VM private memory, instead it can directly execute them from a single copy in memory. Thus large and common binaries can be easily shared between different VMs without consuming additional memory.

#### 2.1. MEMORY DEDUPLICATION TECHNIQUES

A drawback is that the guest OS must be aware of this technique and requires a modified filesystem driver to allow direct execution.

#### 2.1.3 Paravirtualized Deduplication

A major drawback of VM forking – and forking in general – is, that once a COW page's content has changed, it is never shared again, although the contents might be redundant in memory or change back in the future. In paravirtualized environments the guest OS is aware of running inside a VM and communicates directly with its hypervisor. The hypervisor can therefore easily gain information about guest memory operations and can, for instance, intercept memory copy operations and instead establish respective page mappings to prevent memory duplication. It can further provide host to guest file cache sharing.

**DISCO** Bugnion et al. extended the DISCO hypervisor to serve as the basis for *transparent page sharing* [9]. This technique allows, in conjunction with a copy-on-write virtual disk, to share the content of the host's and guest's page caches. Copying the file content into each virtual machine instance is unnecessary; instead DISCO just maps the corresponding pages. All instances share a single copy of the disk content on a block granularity. As long as the same *virtual disk image* (VDI) is used and no write access takes place, no further copy operation is required. If file content is modified a private copy is created. Although this approach is limited to paravirtualized systems with special COW disk images and only available for few operating systems, it still influenced further memory deduplication techniques [52].

**Satori** Satori [36] extents the Xen hypervisor with similar capabilities as DISCO, but does not rely on a single shared disk. In a common usage scenario, every VM has its private VDI; therefore sharing content based on the same logical address is impossible. To overcome this limitation Satori allows sharing based on a page's content, rather than on disk block addressing. Every page gathered from backing store is hashed and inserted into a look-up structure. A request for identical content, from a different VM, causes a look-up and verification. On success the matching page frames are mapped into the requesting VM directly. It ensures that read-only data is present only once in system memory and not scattered in various copies across different VMs. A huge limitation of Satori and DISCO is that they cannot track changes in *anonymous memory* such as heaps and can only utilize data emerging from I/O requests in a paravirtualized environment.

#### 2.1.4 Memory Scanning

Memory scanners detect shareable content by periodically scanning memory pages, typically uncorrelated to a certain system event. Furthermore, memory scanners need no cooperation of the guest OS running inside a VM. Memory scanning can therefore be applied to OSes were paravirtualization is unavailable, or even impossible, due to lack of source code or copyright issues. Furthermore, it can also be applied to native applications, even to applications which do not benefit from traditional sharing techniques, i.e., forking or shared libraries. Memory scanners primarily focus on *anonymous memory*—pages allocated for heaps and stacks.

Although memory scanners differ in their heuristics, scanning intervals, merging granularity, and look-up structures for identical page identification, their common goal is to minimize memory usage of applications and VMs. Once a scanner has identified a pair of duplicate pages, it transparently replaces them with a single copy-on-write protected page, freeing the redundant page copies.

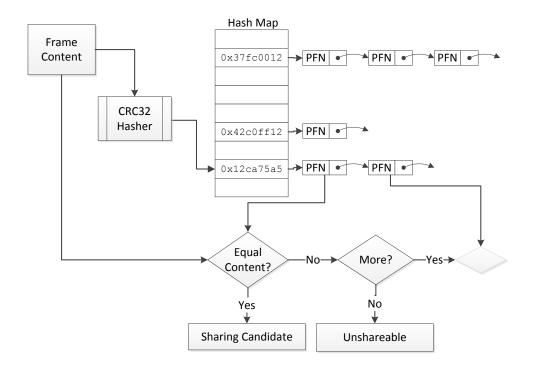

**VMWare ESX Server** The hypervisor VMWare ESX Server includes one of the first memory scanners [52]. Its primary aim is to reduce the memory consumption of VMs and allow more VM instances to run on the same system—for server consolidation. It does not require any adaptations of the guest OSes. The scanner works on page granularity and uses the hash of a page's content as an index into a *hash map*. This look-up structure reduces identification and verification complexity. The scanner is invoked periodically, i.e., every 20 minutes, or just before the hypervisor has to swap-out pages to comply with memory demands of VMs. This solution is dedicated to VMs only.

**Kernel SamePage Merging (KSM)** The Linux kernel has been extended with a memory scanner, which is upstream since Linux kernel version 2.6.32. It is called *Kernel Samepage Merging* (KSM) [3]. Its main purpose is to re-actively share *anonymous memory* across different virtual address spaces. Sharing is possible between regular tasks and VMs – hosted on the *Kernel Virtual Machine* (KVM). That is possible since every KVM-hosted machine allocates only *anonymous memory* to provide guest physical memory. KSM considers pages inside previously marked virtual memory regions and ignores file-backed pages, since Linux does not yet provide a method to merge them.

KSM runs in a single kernel thread that wakes up periodically to scan a configured amount of pages, ignoring current CPU utilization and resource limitations. It utilizes red-black trees to identify possible *shareable* pages. For this purpose, KSM maintains an *unstable tree*, containing all scanned pages, and a *stable tree*, which includes all pages already shared. The index into these trees is formed by the content of pages. A major drawback of this indexing scheme is that changes to

#### 2.1. MEMORY DEDUPLICATION TECHNIQUES

a page and therefore to the index are not tracked. The unstable tree can degenerate drastically since it is only rebuilt after a full scan of all advised pages [3]. The chances of finding mergeable pages declines rapidly [35] and ignores many shareable pages. As in VMWare ESX Server and other scanners, Linux uses copy-onwrite to protect merged pages from modifications. The efficiency of KSM depends heavily on the workloads executed. CPU- and memory bound workloads are least likely to benefit from KSM's scanning mechanism, whereas an I/O bound job, using large amounts of the guest's page cache, can benefit to a greater extent [11].

Page Combining Recent versions of Windows – namely Windows 8 and Windows 2012 Server - also include a memory deduplication technique for anonymous memory. This mechanism is called Page Combining [19]. It aims to reduce the memory consumption of user land programs. In contrast to KSM, Page Combining operates on page frames and not on virtual address space regions, thus, reducing the quantity of scanned content and the overhead caused by page table walks. It does not provide a mechanism to explicitly include or exclude page frames. Instead a default filter is integrated in the Windows kernel. It decides whether a frame is compatible for merging or not. In general, it excludes all frames dedicated to device drivers, working sets, free or zeroed memory lists, and pages already shared by file mappings or shared libraries. Another difference to KSM is its runtime behavior. Whereas KSM wakes up periodically and scans a certain amount of pages, Page Combining, once activated, wakes up in idle periods and scans the whole physical memory in a burst, as long as no other activity interrupts the scan. The background service responsible to host the scan thread wakes up and scans each NUMA node of the system. It acquires the necessary locks, to inhibit memory allocations and scans the page frame database of each node. Checksums for every suitable page frames are calculated and sorted to speed-up duplicate detection. Afterwards all identical page frames are merged to a single copy. The kernel maintains a simple hash table with binary trees to identify merging candidates in future passes more quickly. However, as noted earlier, Windows excludes driver associated page frames and focuses on user land programs. Due to this limitation, VMs cannot benefit from shareable pages between different VMs [46]. Instead, Page Combining is intended to run within the VMs, opposed to KSM.

**Difference Engine** The memory scanners, work on *page granularity*. Difference Engine [18] takes a different approach and identifies identical content on a sub-page granularity. For each found pattern, it creates shareable patched pages. That decreases the memory footprint of VMs beyond the other scanners, but it comes at a cost. Difference Engine has to ensure that the correct page content is

present on each memory access, thus, all patched pages are mapped inaccessible. Therefore, it can only be applied to pages, neither read nor written. Otherwise, page restoration overhead might easily exceed its benefits.

#### 2.1.5 Hinting

Pure memory scanning consumes lot of computational power and still it takes long periods of time – up to minutes – to identify identical memory content [35]. Thus, a hinting mechanism, utilizing semantic information, e.g., disk accesses, can focus a scanner to promising pages, avoiding exhaustive scans.

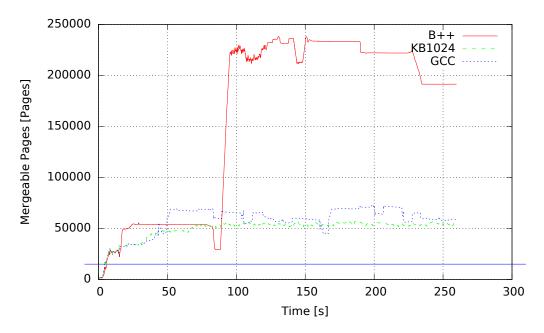

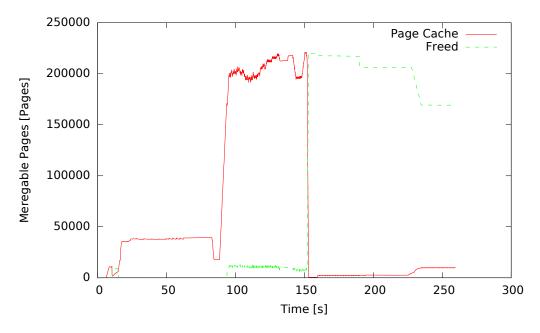

**Cross Layer Hints (XLH)** Previous research suggested a strong correlation between sharing opportunities and *named memory* [36]. To overcome the limitations of memory scanners and paravirtualized guests, *Cross Layer Hints* (XLH) [35] combines an improved scanning mechanism of KSM, with hints from the host's I/O layer. Regular scans take a long time – up to five minutes for small amounts of memory (1 GiB) [35]. This time penalty – for only one pass – prohibits KSM to harvest short living (between 10 and 30 seconds) identical memory pages. Furthermore, it cannot share them, because the *unstable tree* degenerates fast and is seldomly rebuilt. XLH introduces two improvements to KSM. Firstly, it prevents the degeneration of the *unstable tree* by tracking page content changes. Secondly, every time an I/O operation takes place, the virtual file-system layer issues a hint to XLH. These hints point to potentially shareable pages, and are therefore considered before any other page in the linear scan. On average, such I/O related pages are merged five times faster than with the pure improved scanning mechanism.

**Singleton** A different optimization of KSM is taken by Singleton. Singleton utilizes the merging capabilities of KSM [44] and also uses hints from the I/O layer of the hosting hypervisor. In contrast to XLH, it uses the hints to search KSM's stable tree for a match and on success, it tries to remove these identical pages from the host's page cache. It only retains a single content copy for all guest page caches, in contrast to XLH, where an additional copy is still available in the host's page cache. It, therefore, reduces overall memory consumption further than the I/O based hinting scheme of XLH can. It also avoids modifying large parts of the Linux memory subsystem, which otherwise must be adapted to allow sharing named memory pages with anonymous pages and vice versa.

#### 2.2. DUPLICATE MEMORY CONTENT

#### 2.1.6 Conclusion

Although there are many different approaches, which reduce the memory footprint of applications and VMs, all of these techniques are far from perfection or concentrate their afford only on parts of the deduplication potential.

Memory sharing proactively avoids content duplication, but is either limited to named memory such as DISCO and Satori, or cannot reunify duplicated content, for example, VM forking or Saved Named Systems. In contrast, memory scanning re-actively merges identical memory content, but consumes much computational power to harvest shareable content.

For instance, even a reasonable configured memory scanner can only fetch less than 50% of anonymous guest pages [35]. There is no system yet, which harvests nearly all shareable pages with low overhead. Furthermore, to avoid exhaustive scanning, a guest OS must still be instrumented to re-actively share anonymous pages, which is in general not a satisfying solution.

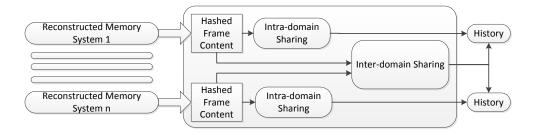

### 2.2 Duplicate Memory Content

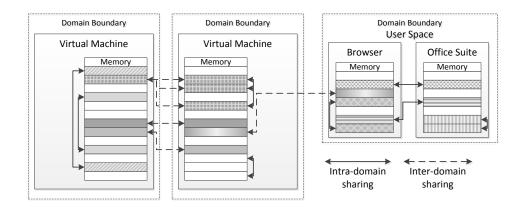

As most applications and VMs produce redundant data on a page, or sub-page granularity, previous work tries to reduce memory footprints by merging content into a single copy [3, 18, 35]. This identical and redundant content is called a *sharing opportunity*. Deduplication tries to harvest these opportunities to decrease the memory consumption. There are two different types of sharing opportunities, an *intra-domain* sharing opportunity – also called *self-sharing* – and an *inter-domain* sharing. They differ mainly in the pages considered for merging, as depicted in Figure 2.2.

**Intra-domain** In this case, only pages within the same domain, e.g., NUMA node or the same VM are considered for merging. These sharing opportunities are always available, whether a similar workload is executed or not. Intra-domain sharings are similar to compressed files, where only a single file is used to find compressible patterns, and all other files are ignored. In most cases these sharings are by a magnitude smaller than inter-domain sharings [26]. Their primary sources are redundancies within files and typical desktop workloads such as browsers, office applications, etc. [41].

**Inter-domain** In contrast to intra-domain sharings, all content of all accessible VMs is considered for matches. In a non-virtualized environment, inter- and intra-domain sharings are identical, since there is no additional domain. The *inter-domain* sharing heavily depends on the workloads residing inside the VMs. Har-

vesting inter-domain sharings must be done with care. Merging pages for instance across different nodes in a NUMA system, might slow down overall application performance. Furthermore, depending on the deduplication mechanism, security concepts such as strict domain isolation might be weakened [48]. Intra-domain sharings do not interfere with protected resources and remain in their own restriction boundary, whereas inter-domain sharings break this boundary. However, their sharing potential is higher and can reduce memory usage up to 79 % [41].

Figure 2.2: The figure shows two VMs (two semantic domains), and native applications, a domain of its own. Pages can be shared within the same domain (*intra-domain*) and across domain boundaries (*inter-domain*).

### 2.3 Full-System Simulation

Full-system simulation enables a thorough analysis of computer systems from coarse- to fine-grained detail. They enable the analysis of program behavior, memory operations, and other properties *without interrupting* the data flow, changing *memory content* or the *timing* of the guest system. In contrast to user land introspection tools, i.e., Valgrind [38] or Pin [30], full-system simulators provide a compatible system environment – a bare simulated hardware – for the guest OS. They further offer different levels of simulation detail, starting from pure *system-call emulation*, over *functional simulation*, to timing accurate *micro-architectural simulation*. There are two kinds of execution modes for this purpose: An *interpretive mode*, where each guest instruction is directly emulated via respective simulator routines and a *translation mode*, where, prior to execution, instructions

#### 2.3. FULL-SYSTEM SIMULATION

from the guest system are translated into a semantically identical instruction sequence of the host's *instruction set architecture* (ISA) [5]. The primary aim of the interpretive mode is typically a complex simulation of pipelines, CPU models and timing, whereas the translation mode favors speed and emulates only the result of an operation at a function level. Both approaches can be combined to achieve different levels of detail and increase execution speed.

#### 2.3.1 Binary Translation

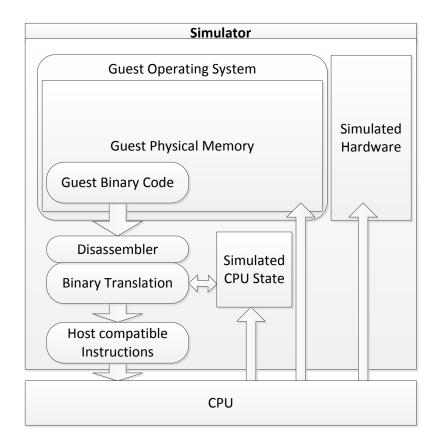

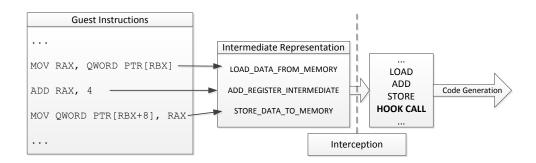

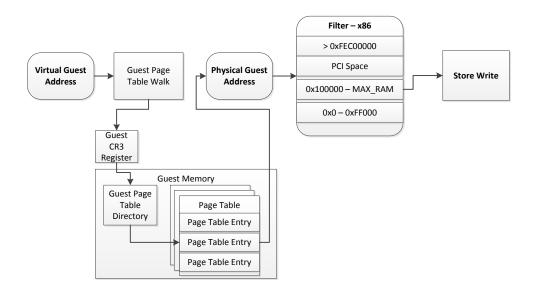

Every simulator has to decode and transform guest instructions into an operation, which can be executed on the host system. As illustrated in Figure 2.3, the primary step is to *disassemble* the guest code, and then feed this information into a *binary translator*. The binary translator will produce a semantically identical code sequence, which can be executed directly on the target platform. All produced code sequences alter only guest memory and the simulated system state [5].

Binary translation is the core element of most simulations. It reduces the bottleneck of conventional, interpretive emulation and speeds-up the execution of a simulated system [5]. Binary translation can be done in two flavors, *statically* or *dynamically* [40]. Static binary translation is done in advance, and no extra instruction decoding or compilation must be done during runtime. However, it has major drawbacks; it cannot translate all code paths correctly, since some information such as conditional jumps or privileged operations depending on the current CPU state are unknown in advance. Furthermore, *dynamic code generation*, often used by Just-In-Time compilers or *self-modifying code* cannot be used at all. Static code translation is thus not applicable to all programs and especially not feasible for whole operating systems. Full-system simulators thus typically execute guest code in an *interpretive mode* or switch to *dynamic translation*.

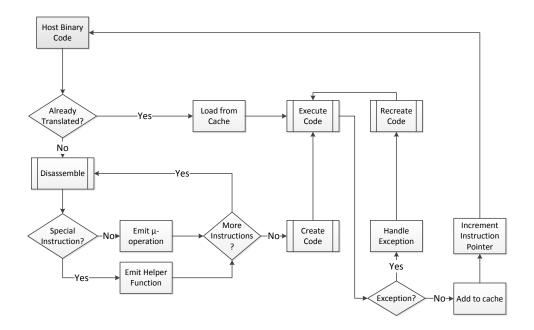

Dynamic binary translation (DBT) has been used in many system simulators and in early x86-compatible VMMs (VMWare Workstation, VirtualPC, etc. )[1] before hardware accelerated virtualization became available. It overcomes the drawbacks of static translation and enables the simulation to provide all features as present in the simulated ISA. The translation process, as depicted in Figure 2.4, is executed during the simulation and transforms the guest code on demand, following the current program flow of the guest. That allows the guest OS to run unmodified. However, it can be transparently extended with introspection functionalities. That is because, the resulting binary code, with modification and extensions, is invisible for the guest system.

The translator breaks the guest code down into *basic code blocks* [50]. A code block contains consecutive instructions till the next jump instruction. A jump terminates each basic block, since the jump's destination is unknown in advance and has to be evaluated after execution. This code partitioning allows to translate a

Figure 2.3: The general work-flow of a simulator using *binary translation*. The guest code is disassembled, translated, typically instrumented, and executed on the hosting platform. All memory accesses have been modified to point into the guest assigned memory regions.

complete block into its host equivalent. During the execution of the translated block, *program exceptions* or CPU state changes can occur, which require a *code block* to be modified and re-executed. For instance, if a *divide-by-zero exception* occurs, the following instructions cannot be executed without handling it. Therefore, the translator creates a new slightly different code block handling the exception and re-executes it. If a code block has been successfully executed, the translator can add it to its optional *translation cache* [40] to by-pass the complex block creation in the future. However, to support *self-modifying code*, already cached code blocks must be invalidated, if the guest code changes. Afterwards, the translation cycle starts again, at a new *Instruction Pointer* (IP).

Figure 2.4: Dynamic binary translation and the typical work-flow of disassembling, translation, and execution to correspond to the guest ISA. The binary translator must recreate a *code block*, if an exception, e.g., a page fault has occurred. A successfully executed block is added to a cache to speed up re-execution.

In more detail, the *dynamic binary translation* for full-system simulators follows the following four basic steps.

**Disassembling** The guest code is disassembled, split up into its *instructions* and its *operands*. Some ISAs, e.g., ARM, are easier to disassemble than others, e.g., x86. The decoding of instructions can only be done as far as no conditional jump is encountered [40]. As jumps change the instruction pointer, all following instructions might become invalid and can therefore only be decoded after the execution of the jump. A problem of the x86 ISA is its *variable* instruction length. An instruction ranges from one up to 15 bytes, and are not aligned on a machine word boundary [23], which makes decoding even more complicated [1]. Once an instruction has been successfully decoded, it can either be directly passed to the *recompilation*, or it can form an *intermediate representation* (IR) [5]. An IR aims to match two different instruction set architectures. It typically consists of much simpler operations (load, store, arithmetic, branch instructions, etc.) – a sub-set of all supported instructions.

**Recompilation and Instrumentation** The disassembled code or its intermediate representation cannot run unmodified, since it still contains wrong, or incompatible memory addresses, privileged, or even unsupported instructions. They would alter the state of the host system, rather than the state of the simulation. Thus, addresses must be recalculated to map into the *guest's memory*, or at least comply with the simulated *memory management unit* (MMU). All privileged instructions have to be replaced with equal functionality, otherwise they cannot be executed at all. Furthermore, modifications to a simulated device state or the configuration of a simulated CPU would be unavailable, since typically these instructions can only be executed in a privileged execution mode. The simulator also needs to add exception handling code to cope with faulty memory accesses or to comply with the guest ISA's exception mechanisms. After these necessary modifications to the guest code, the simulator can further add *instrumentation* code, for system state *inspection*. That allows to add tracing functionality such as memory or instruction hooks. The resulting code blocks can either be directly executed or passed to a *relinking* procedure.

**Relinking** In this step the previously generated code blocks are linked, if possible. To achieve better performance, the *relinking* [5] can make use of previously compiled blocks and produce in the best case a long phase of uninterrupted program execution.

**Execution** The execution of the recompiled binary code is straight forward. All critical operations have been replaced and only conditional jumps, exceptions such as page faults and illegal operations, or interrupts might alter the instruction flow. In such conditions, the code block is typically discarded and recreated, starting from the faulting instruction and extended with exception or interrupt handling routines. A different approach is to directly jump to a suitable handling function and continue afterwards. Once the available blocks have finished execution, the translator typically adds them to a translation cache and determines the new *instruction pointer* and starts decoding from this point.

#### 2.3.2 Full-System Simulators

A variety of full-system simulators exist. They are designed to simulate different aspects of a system in more or less detail. Simulators vary from emulation – *functional simulation* – at the instruction level to provide *functional correctness* to timing accurate *micro-architectural simulation*. The following list of simulators is not complete, since various variations exist and many different research projects [37, 39] have extended or adapted them to their needs. We therefore give an overview of the most commonly used simulators.

**Bochs** Bochs [28] was one of the first freely available system simulators, providing the facilities to run unmodified x86-compatible operating systems on different CPU architectures. To allow these OSes to run, Bochs simulates PC-compatible hardware. However, due to its interpretive mode, each instruction's equivalent is directly executed after disassembly. Bochs thus remains a factor of 30x slower than other simulators using DBT [5]. In general, it is a slow virtual machine, providing functional correctness, but no timing accuracy or micro-architectural simulation.

**Gem5** Gem5 is a fusion of the M5 and the GEMS simulator and combines M5's CPU and interconnection model with GEMS's memory and cache coherent protocol simulation [6]. It forms a highly flexible simulator with a fine to coarse grained simulation. Gem5 is capable of emulating different ISAs such as ARM or x86, on different host architectures. It offers two operation modes: A systemcall emulation only suitable for user land programs and a full-system simulation. The system-call emulation is very high level and does only intercept system service requests, similar to a sandbox and is therefore limited. The full-system mode presents a bare machine with a wide range of emulated devices necessary to run commodity operating systems, such as Linux. This mode of Gem5 is slower compared to other simulators, since it does not use a sophisticated binary translator [6]. Instead, it creates a list of virtual calls to emulate functionality of each disassembled instruction. Although, this approach is faster than a pure interpretation due to saving repeated disassembling, it cannot compete with full DBT; especially if a functional simulation is sufficient for a particular analysis. However, an advantage lies in its flexibility in terms of simulation detail and extensibility.

**MARSSx86** In contrast to the previously described simulators, MARSSx86 [39] utilizes a dynamic binary translator and augments its code with cache, pipeline, inand out-of-order CPU simulation functionality. It provides support of single- as well as multi-core configurations. It simulates complete cache hierarchies down to the cache synchronization protocol level, similar to the micro-architectural simulation mode of Gem5, but combined with a faster instruction simulation. Although it is based on the open-source simulator QEMU, it is far more flexible and allows switching from a fast result driven simulation to a more complex micro architectural accurate mode. However, it is only available for x86. **WindRiver Simics** WindRiver Simics [31] is a commercial simulator, used in various scenarios, from debugging faulty programs, to malware analysis, and hardware simulation. It allows deterministic, cycle accurate simulations and supports various, flexible hardware configurations. Simics supports binary translation for various instruction sets, generic parametrized cache simulations, and runtime inspection of CPU and memory. The simulation guarantees functional correctness with optional accurate timing. A pipeline simulation, as in MARSSx86, is omitted for performance reasons, CPU models comprising a pipeline simulation can however conceptionally be added. The performance of an un-introspected function level simulation varies from 2.1 MIPS to 5.7 MIPS on an ancient Pentium III processor [31]. On recent hardware, intercepting every memory access leads to a simulation speed of about 3 MIPS [42].

#### 2.3.3 Quick Emulator (QEMU)

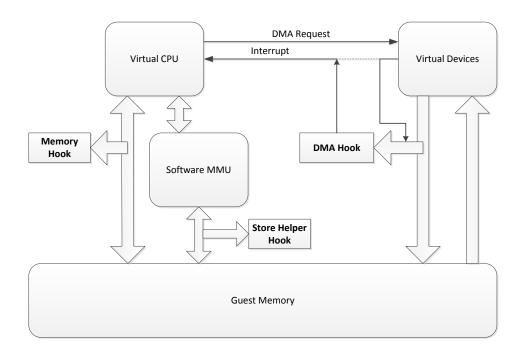

In contrast to the previous described simulators, *Quick Emulator* (QEMU) [5] is widely used for virtualization in Linux environments. As hardware-virtualization became available on a wide range of processor architectures, the DBT is only used to simulate a different architecture, e.g., ARM on x86. QEMU is often used in conjunction with the *Kernel Virtual Machine* (KVM), but just provides emulated I/O devices. The instruction stream is directly executed on the processor and only privileged operations fallback into QEMU for handling. QEMU still comprises a

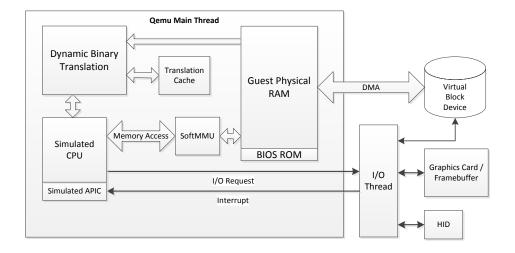

Figure 2.5: The organization of QEMU. It consists of two threads, one for CPU simulation and one for device emulation. The interaction is similar to a real system, but interrupt delivery can be postponed.

#### 2.3. FULL-SYSTEM SIMULATION

*dynamic binary translation (Tiny Code Generator* (TCG)) and can be extended to provide similar simulation features as present in Gem5 or Simics [37, 39].

The simulation mode of QEMU uses DBT with an *intermediate representation* (IR), to translate the guest ISA to the host ISA. The IR enables QEMU to support a sub-set, common denominator of all ISAs. The used intermediate representation consists of *micro operations*, a subset of all possible instructions of different architectures.

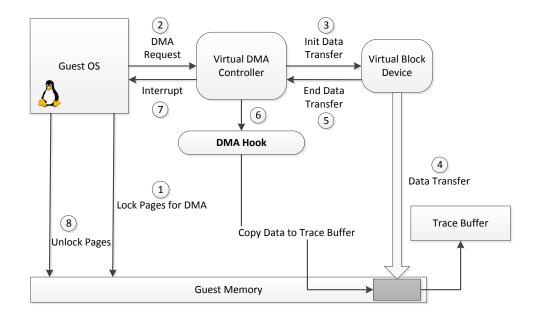

Figure 2.5 shows the general organization and operation of QEMU. QEMU provides two threads of execution. The main thread simulates the CPU state and executes the resulting code from the DBT. If QEMU simulates multi-core CPUs it schedules them to this thread in a round robin fashion, avoiding complex synchronization and locking mechanisms. A second thread handles DMA and I/O requests and triggers interrupts on completion, which will be processed after every successfully executed code block. QEMU emulates the behavior of real hardware, with a DMA controller and asynchronous operations, but with a slightly different timing, since interrupts can be postponed for longer periods, as they would do in a real system.

# Chapter 3

# Analysis

Previous research has been concentrated on pages related to the Linux page cache and I/O operations, since these pages are a primary source for duplicate page content in a virtualized environment [9, 35, 36]. The *page cache* buffers content read from or stored to block devices. Thus, in a virtualized environment identical page content resides in guest and host page caches. Existing page deduplication approaches either prevent duplication proactively, e.g., *Satori* [36], or merge the replicas instantly, e.g., *XLH* [35]. The hypervisor can easily collect page frames associated with the guest page cache by simply monitoring I/O operations – i.e., data transfers from and to virtual block devices – even without paravirtualization. That is because every I/O operation must be handled in the hypervisor or the host OS. It is an example of how information about pages can help to focus on promising memory regions and how these information can be collected.

However, there might be even more sources, which can easily be harvested to increase the efficiency and effectiveness of memory scanners. Although XLH and *Singleton* exploit nearly all sharing opportunities stemming from the guest page caches up to five times faster than regular memory scanners [35], they still cannot merge other sharing opportunities with similar speed. Their memory scanners still consume a large amount of time and computational power trying to identify and merge identical pages originating from anonymous guest memory. As suggested [41], some pages (e.g., about 54% of pages in desktop workloads) even change too fast to be harvested through periodical scans at all, while at the same time they are stable long enough to justify merging. Scanning with higher scan rates and more computational power might already solve some of these problems, but as memory can always be used for better purposes, the same is true for CPU resources; including the energy they consume when active. A direct hint to fetch moderate changing pages as quickly as possible or to exclude unstable pages could concentrate memory scanners on more promising regions and increase their effectiveness beyond what solely I/O focused scanners achieve today. To avoid expensive and futile scans, a restricted scan domain, with a high sharing probability is advisable. Otherwise, all pages of a VM have to be considered during scanning, even if a region contains stacks or virtual device memory and the probability of a *stable* memory page is low. Non-paravirtualized VMs lack semantic information and a memory scanner can therefore not exclude memory regions based on their internal allocation.

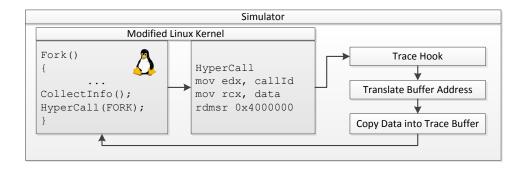

There are different ways to bridge this semantic gap. Firstly, a paravirtualized OS can be used to report allocation changes and other relevant system events. Secondly, techniques for *VM migration* and *memory reclamation* can collect similar information without modifying the guest OS. One way is to analyze the VM guest memory, searching for memory management structures and parsing the contained information [12]. Another way, is taken by XLH [35], as it monitors I/O operations to and from virtual block devices inside a hypervisor to identify and prioritize a VM's page cache pages. Another source of information are page tables, e.g., dirty bits might indicate changing page contents. Additionally, a statistical analysis might bridge the semantic gap as well and provide (workload specific) heuristics, minimizing the scan regions or prioritizing regions with high sharing probabilities.

As previous work showed, if a scanner focuses on pages with high sharing potential [35, 44], it achieves better and faster memory footprint reduction. However, there are still pages, which are shareable, but cannot be harvested due to slow scanning. We aim at discovering correlations between *duplicate memory pages* and statistical information to either focus on stable regions or to exclude unsuitable pages, *permanently* or *temporarily* from the scanning process and thus increase the effectiveness of memory scanners.

### 3.1 Analyzing Sharing Opportunities

We focus our research on sharing opportunities not yet harvested by a hinting mechanism, and thus, if merged at all, need to be fetched by a periodical memory scan. A requirement for merging sharing opportunities is *stability*. Otherwise, the likeliness of breaking a merged page is very high. Less is known about other properties of these remaining sharing opportunities.

**Sharing Opportunities** As we want to focus a memory scanner to unused sharing potentials, at first we have to detect all *sharing opportunities* in examined workloads. Without this quantification of the overall sharing potential an analysis of their properties is impossible. Sharing analyses, comparing every page's content with every other page, can be done in two ways. They can consider only

#### 3.1. ANALYZING SHARING OPPORTUNITIES

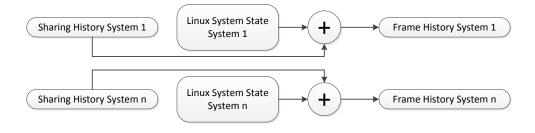

a single system and detect content duplicates within its own domain – an *intra-domain sharing*. Another way is to perform an *inter-domain sharing analysis*. It considers not only a single system, but also many systems, e.g., all VMs on a host, and detects sharing opportunities in all systems, which drastically increases the available sharing potential [41].

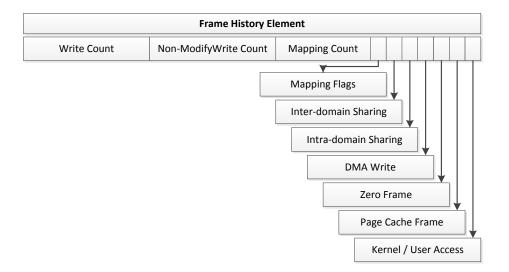

**Semantic Information** As shown in previous research [35, 36, 41], *semantic information* can help to provide better hints for a memory scanner. If a memory deduplication system is aware of a page frame's allocation, it can easily decide whether it should consider it during a scan, or leave it unexamined. For example, a scanner would be able to exclude stacks and virtual device memory permanently from its scans, as these regions have shown no sharing potential in the past [41].

**Memory Access Frequency** A frequently written page frame is an unsuitable candidate for memory sharing. Even if a sharing partner exists, it is most likely that the content will change in the near future and an already established sharing would break. Thus, a write access frequency for every page frame might help to determine pages, which should be skipped (at least for one scan pass), as long as they are changing fast. Low frequencies indicate probably more stable page frames.

**Memory Access Patterns** Extending the idea of memory access frequencies, it is possible that a distinct *memory access pattern* directly indicates the usability of a page frame for sharing. Memory access patterns use the temporal or spatial distribution of memory write accesses to provide a more complex identification scheme. It could be possible that different write access patterns directly lead to *stable* and shareable pages, whereas other patterns indicate the contrary. It is unclear, if more information about the history of each page helps to identify stable regions, or if access patterns show no statistically significant correlation to page (in-)stability. If such correlations on these pages, or skip them.

**Semantics and Stability** The conjunction of *semantic information* and *stability* of a page frame should improve scanning even further. Thus, as already shown, page cache pages remain stable for long periods of time [36, 41], the same might be true for, e.g., heap pages with a specific write frequency, access pattern, or write history. We have to examine, if and to what extend such correlations exist and if they can be used to improve memory scanning.

Write Working Set A working set describes the amount of accessed memory pages in a time interval [14]. It indicates the amount of memory and the pages used within the last observed period. As working sets are often estimated to determine, which pages can be evicted from physical memory and moved to swap space, it might also be useful for a memory scanner. We slightly modify this idea and consider only modified pages, which form a *write working set*. We exclude read pages, since reading a page does not change its stability, nor its sharability. Only write operations change content, and therefore break shared pages. If a page leaves a write working set, it could be considered for a memory scan, as we assume it to remain stable, i.e., unmodified. Afterwards for a sufficiently long time period to justify examination by a memory scanner.

### 3.2 Required Analysis Data

To verify if memory access patterns and stability criteria for duplicate memory pages exist, we have to collect different data for analysis. First of all, we have to ensure, we can identify *sharing opportunities*. Therefore, we have to collect memory content of the analyzed system. Information on memory accesses build the foundation for analyses of memory access frequencies and patterns as well as page stability. In contrast to reads, write operations may invalidate the information a scanner has about pages or even leads to breaking already shared pages. In consequence, at least every memory modification needs to be tracked.

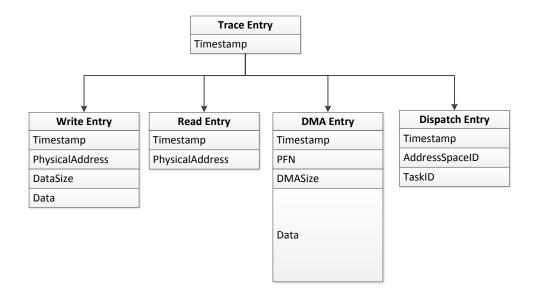

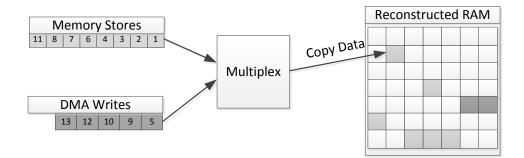

**Memory Content** As program execution progresses memory content is modified. To be able to analyze sharing opportunities, a consistent memory image for every point in time must be available. Otherwise, shareable page content might be missed. *Memory content* is modified in two ways. Firstly, a program running on a CPU issues store operations, which change the content of main memory. Secondly, devices utilize *direct memory access* (DMA) to move content to and from main memory. To maintain a consistent memory view, these two operations must be traced. Monitoring these operations provides us also with the information necessary to analyze the memory access frequency, write access patterns and the access history of each page frame.

**Memory Semantics** To allow a more thorough and detailed analysis, we require additional *semantic information* associated with each page frame. Every page and its corresponding page frame have semantics associated with them. Most prominently, each page is allocated for a specific purpose, for instance to serve as a page for *named* or *anonymous* memory. The *allocation* of a page is important, but it can be further enriched with *mapping information* and *page table flags*. Only

this combination allows us to tell stacks and heaps apart, since both are allocated as anonymous memory. To further understand *memory access patterns* it might be helpful to distinguish the source of a memory operation, i.e., if it has been issued by the kernel or by a user-land program.

**System State** To trace store operations back to the issuing address space and in conjunction with scheduling information even back to the issuing thread, it is necessary to consider the current state of the examined system's OS. We, therefore, consider all *address space events*, regardless whether an address space is created, modified, or destroyed. The same is true for *task creation and destruction*. Furthermore, we want to track *kernel events* to be able to correlate different store operations to the dedicated kernel sub-system.

To improve memory scanning, we must identify new hinting sources or patterns, which allow to reduce the scanning overhead, by including or excluding pages. We came to terms that at least the information in Table 3.1, must be considered for our analyses.

# 3.3 Data Acquisition

To analyze sharing opportunities, page stability, and memory access patterns, all data for these analyses should be captured on a *non-interfering* level to avoid distortions of the examined workloads. As our analyses require different data sources, they should be collected in a single pass. Otherwise, correlation of semantic data, with memory accesses becomes difficult or might be impossible.

To measure the sharing potential some approaches regularly dump the memory of (hardware accelerated) VMs [35, 36], but typically that changes guest timing, affects the CPU caches, and scheduling policies. In the worst case it changes the complete behavior of a workload and cannot produce reliable data for analyses. Furthermore, memory dumps require large amounts of disk space and suffer from low temporal resolution. In the case of *Satori*, their snapshot resolution was only 30 seconds [36]. In contrast to *Satori*, we require every memory modification to calculate *memory access frequencies* in a high temporal resolution, not only long lasting sharing opportunities. To acquire memory accesses different methods come to mind.

One way to collect memory accesses is to map pages inaccessible in every referenced page table and modify the page-fault handler to trace read or write accesses. Then, a faulting instruction must be restarted in a single-step execution mode, with a temporally accessible page to perform the actual operation.

| Purpose          | Data to collect                                                                                                                                                     |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Memory Content   | <ul><li> Memory Writes</li><li> DMA Writes</li></ul>                                                                                                                |  |

| Memory Semantics | <ul> <li>Memory Accessor (Kernel or User space)</li> <li>Guest Memory Allocations</li> <li>Mapping Information</li> <li>Page Flags</li> </ul>                       |  |

| System State     | <ul> <li>Task Creation and Destruction</li> <li>Scheduling Information</li> <li>Address Space Creation, Modification, Destruction</li> <li>Kernel Events</li> </ul> |  |

Table 3.1: The three major data categories for a thorough, semantically enriched, sharing opportunity and pattern analysis.

Immediately after this operation the debug-exception handler can reset the page table bits to mark it inaccessible. These modifications are not only very complex and come with a high overhead, they also require a disassembler to decode the faulting instruction and to determine the performed operation. Another way is to utilize performance counters, which issue an interrupt every time a memory access occurs which is processed by a handler routine. This routine must analyze the operation, but might not be able to determine the actual written data, since it happens after a memory access. These two methods are not only expensive due to overhead, they typically miss memory accesses, e.g., from DMA capable devices. However, a VM might be able to ensure that no accesses are missed, but that implies a radical change of the hosting OS and the hypervisor. Furthermore, it still disturbs scheduling, guest timing, and CPU caches. A better and more reliable way to retrieve memory content without distortions, is a *simulation*.

#### 3.3. DATA ACQUISITION

Previous research clearly showed the capabilities of *full-system simulators* and their advantages over other data acquisition methods (for a detailed analysis of different techniques see [41]). In contrast to a hardware-accelerated VM, tracing memory accesses is simple in a full-system simulator and does not affect the timing, execution order, or scheduling within the guest system, at all. We therefore decided to use a *full-system* simulation.

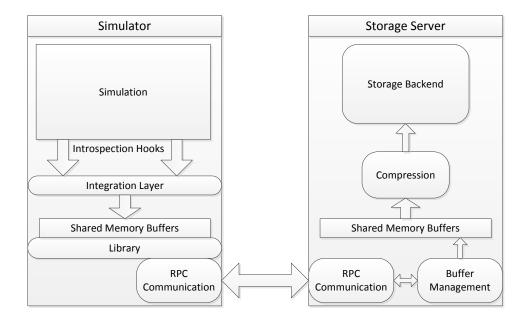

A great drawback of this approach is the slow execution of simulated systems. They tend to be slower by magnitudes than real systems [42]. As they are already slow – even without complex introspection – a data analysis during simulation becomes even more expensive and reduces flexibility as online analyses require a rerun of a simulation for every considered question. Therefore, and to allow a simple correlation of different analyses, it is best to only collect data during simulation, save it and process it offline.

A full-system simulation can simulate various aspects of a system and recording all information is unfeasible. As we focus on memory access patterns and semantic information, we only collect all necessary information. The required data fits into three groups. Firstly, *direct recordable data* produced by a simulation, e.g., memory accesses. Secondly, *semantic information* from within a guest OS, such as memory allocations. The third group consists of data which can be inferred from *memory content* or *semantic information* by an analysis, e.g., *sharing opportunities* and must therefore not be recorded explicitly.

### **3.3.1** Memory Content

The first category of data is sufficient to analyze *memory access frequencies* and *memory patterns*, or to infer *sharing opportunities*. In a full-system simulator, memory accesses are traceable without any change of operating system code. This important data can therefore be collected independent of guest OSes, workloads, and simulated ISAs.

In contrast to many previous works [4, 35, 36], we cannot rely on periodical memory dumps. Although dumps are sufficient to provide sampled statistics about the sharing potential in a system, they are not a basis we can draw conclusions about the memory access frequencies or patterns on. That is because dumps only capture memory content, but not modifications, and write operations must not lead to changed content<sup>1</sup>. We therefore need to instrument the simulation to provide information on every write operation to be able to analyze access frequencies and access patterns afterwards. At the same time, we still need to be able to find sharing opportunities based on these information.

<sup>&</sup>lt;sup>1</sup>Previous work reported that up to 34% of write accesses do not change memory [41].

There are two ways to store memory modifications: Firstly, like in previous work [41], after each memory modification event, a hash can be calculated for the target page frame and stored for later retrieval. In that case, identifying sharing potential is based on page hash comparisons. Secondly, memory operations can be traced directly with destination address and data. That allows to replay every memory modification and recreate a complete memory image. Both methods are in general suitable to base our measurements on.

The first method is inspired by previous studies on memory duplication, which are mostly done with hashes or checksums [1, 36, 41]. That suggests to save page content hashes and avoid a memory content rebuild during analyses. Although it seems to speed-up sharing opportunity analysis, this method has two major drawbacks. Firstly, a suitable hash, with nearly no hash collisions, consumes at least the same amount of memory as the data actually written by a memory operation. Secondly, a hash calculation for every memory modification slows down simulations by a magnitude. A fast hash function such as CRC32 on the other hand, is not sufficient to avoid *false positives* – i.e., wrongly identified duplicate page content – during recording. Although a *cryptographic hash function* or larger hash value might minimize this probability, it is harder to compress, due to its higher entropy and thus less suited to be recorded.

The second method stores every write with its destination address and the actual written data. Thus, the complete memory content can be restored and different questions can be answered with the same trace data. As stored write operations can rebuild the complete memory content on different temporal and spatial resolutions, they allow flexible inter-domain sharing analysis, and furthermore, an extraction of instructions and loaded file content if needed. Identifying sharing potential from a reconstructed memory image is trivial and precise. A drawback of a memory rebuild is however, that the analysis requires at least the same amount of memory as the examined simulation did. We conclude that storing memory writes directly, will provide most flexible trace data for an offline analysis.

A subsumed comparison of both methods can be found in Table 3.2.

## **3.3.2** Memory Semantics and System State

As mentioned earlier, important semantic information, e.g., memory allocations, must be recorded. It is not directly included in a memory image and complicated to extract with tools, such as *crash* [2] or *Volatilitux* [17]. Such an extraction from a reconstructed memory image, can be erroneous due to missing symbols or partially written data structures. Furthermore, it is slow. Directly recorded *operating system events* allow to reconstruct the system state faster. Therefore, we explicitly record *memory allocations* and *system events* changing the current *system state*

| Stored Data | Pro                                                                       | Contra                                             |  |

|-------------|---------------------------------------------------------------------------|----------------------------------------------------|--|

| Hash        | Fast Sharing Analysis                                                     | False Positives<br>High Entropy<br>Low Flexibility |  |

| Actual Data | Fast Simulation<br>Good Compression<br>High Flexibility<br>Memory Content | High Memory Utilization                            |  |

Table 3.2: A comparison of how to store memory modifications. Storing actual written data is fast and allows most flexible analyses. Our chosen method is in bold.

from within the analyzed OS. That does not only reduce the reconstruction overhead, it also allows flexible OS introspection.

# 3.4 Simulation

Many different simulators are available with a coarse- to fine-grained simulation detail, providing *function level* to *micro-architectural* simulation modes. As a *micro-architectural* simulation must simulate, for instance, a CPU pipeline, the memory bus, and cache coherency protocols, it has to execute more code per simulated instruction, whereas a *functional* simulation can just simulate the result of an operation. Thus a functional simulation is faster. We focus on execution speed, since previous work [25, 41] clearly showed simulation speed as a bottle-neck in the analyses process. If simulations take up to weeks, and making only little progress, simulating complex and long-running workloads becomes unfeasible. Rittinghaus et al. compared different simulators and measured their execution speed, which ranges from 3 MIPS up to 93 MIPS for memory inspection [42].

There are three main goals, which a simulator should provide. Firstly, it should be able to allow memory inspection and pass information from within the guest OS to the tracing infrastructure. Secondly, it should be able to provide an accurate timing source to correlate system events with memory accesses. Thirdly, the simulation should run as fast as possible.

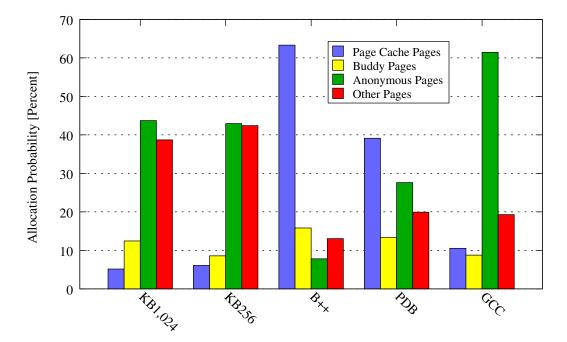

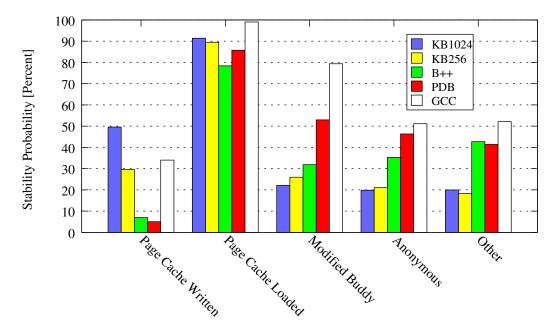

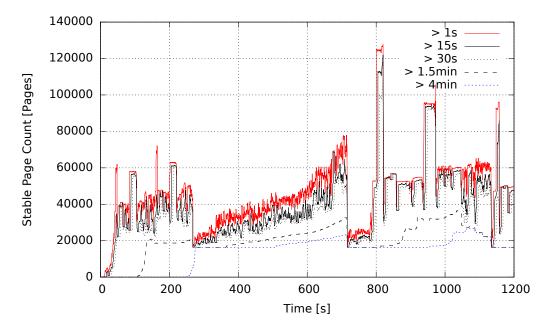

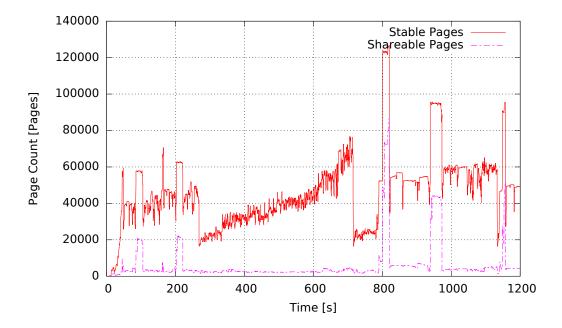

## 3.4.1 Full-System Simulator Comparison