# Accurate Record & Replay of x86 MMU Behavior for SimuBoost

Masterarbeit von Benedikt Morbach

an der Fakultät für Informatik

Erstgutachter: Zweitgutachter: Betreuender Mitarbeiter: Prof. Dr. Frank Bellosa Prof. Dr. Wolfgang Karl Dipl.-Inform. Marc Rittinghaus

Bearbeitungszeit: 14. März 2018 – 13. September 2018

Karlsruhe, den 13. September 2018

Ich versichere wahrheitsgemäß, die Arbeit selbstständig verfasst, alle benutzten Hilfsmittel vollständig und genau angegeben und alles kenntlich gemacht zu haben, was aus Arbeiten anderer unverändert oder mit Abänderungen entnommen wurde sowie die Satzung des KIT zur Sicherung guter wissenschaftlicher Praxis in der jeweils gültigen Fassung beachtet zu haben.

iv

### Abstract

In order to speed up record and replay of full virtual machines systems like *SimuBoost* employ hardware-assisted virtualization to limit the impact of the recording process on the virtual system's performance. Like all record and replay systems this requires accurate logging of non-deterministic events that occur during the recording and injection of these events during the replay. The deterministic instructions between these events are being replayed directly.

However, current record and replay systems do not account for non-deterministic events that can be introduced by the x86 memory management unit (MMU). The unpredictable behavior of the translation lookaside buffer (TLB) and its potential incoherency with the page tables in RAM can cause the MMU to either set accessed and dirty bits in the page tables or skip this step depending on the TLB's contents. When the recorded system reads the state of these bits, the replay can diverge from the recorded execution if the TLB's contents or its behavior differ between the two, which is almost unavoidable.

We propose a way to record the changes the MMU makes to the status bits in the guest's page tables and implement it as part of the SimuBoost system. We achieve this by protecting the page tables in using the extended page table (EPT) mechanism on modern Intel CPUs and emulating these instructions using the emulation facilities for x86 code within the KVM Linux module. We implement support for replaying these events in the QEMU fork QSIMU that SimuBoost utilizes for heterogeneous replay.

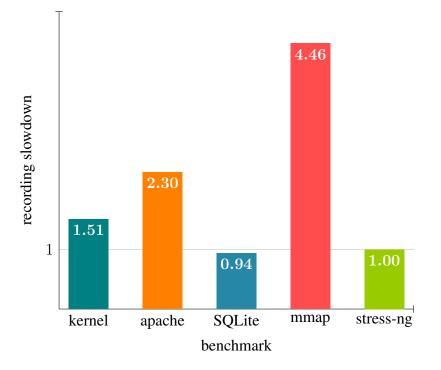

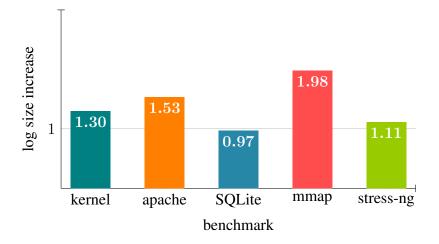

Our results show that this approach can be a feasible solution. While we observe a 350% slowdown during recording for worst-case micro-benchmarks, the impact on some real-world applications is only 50% and CPU intensive workloads as well as the replay of any of the workload are not affected at all. This system is also able to successfully replay workloads the existing system consistently failed to replay before.

ABSTRACT

vi

# Deutschsprachige Zusammenfassung

Systeme zur Ausführungswiederholung (engl. *record and replay*) haben das Potential ein wichtiges Werkzeug zur Fehlersuche in komplexen Softwaresystemen zu werden. Anstatt ein Programm mehrmals ausführen zu müssen um einen Fehler zu reproduzieren und schrittweise ein Areal im Programmcode einzugrenzen das als Fehlerursache vermutet wird reicht es, eine einzige Ausführung des Programms aufzuzeichnen. Anschließend kann diese beliebig oft wiedergegeben und sogar zurückgespult werden um so von den Symptomen des Fehlers zu dessen Ursache zu finden.

Aufgrund der zunehmenden Verbreitung von virtuellen Maschinen in vielen Anwendungsgebieten, allen voran im Serverbereich, wurden diverse Systeme vorgeschlagen die dieses Prinzip der Ausführungswiederholung auf die Maschinenbefehlsebene übertragen und somit das Aufzeichnen und Wiedergeben eines gesamten virtualisierten Systems ermöglichen. Dies ist nicht nur ein hilfreich im Bereich der Fehlersuche, sondern erlaubt auch die forensische Analyse von Schadsoftware nachdem ein solcher Befall entdeckt wurde da das System zur Ausführungswiederholung nicht von der kompromittierten virtuellen Maschine beeinflusst werden kann.

Um Systemressourcen zu schonen vermeiden Systeme zur Ausführungswiederholung es nach der Ausführung jedes Befehls eine vollständige Kopie der virtuellen Maschine zu erstellen. Stattdessen machen sie sich die Tatsache zu Nutze, dass die Ergebnisse der meisten Maschinenbefehle in deterministischer Weise von ihren Eingaben abhängen. Nur der initiale Zustand und solche Ereignisse die inhärent nichtdeterministisch im Zeitpunkt ihres Eintretens oder ihrem Inhalt sind, wie z.B. Unterbrechungen, müssen aufgezeichnet werden. Die restlichen Stadien des aufgezeichneten Systems zwischen diesen Ereignissen können jedoch wiederhergestellt werden indem die deterministischen Befehle auf den vorliegenden Eingabedaten berechnet werden.

Um die Leistungseinbußen durch die Ausführungsaufzeichnung der virtuellen

Maschine in einem akzeptablen Rahmen zu halten verwenden Systeme wie SimuBoost [1] die Hardwareerweiterungen zur hardwareunterstützten Virtualisierung die in die von den meisten aktuellen Systemen unterstützt werden und führt einen Großteil der Befehle des aufzuzeichnenden Systems direkt auf dem Gastgebersystem aus. Dies führt jedoch zu einer neuen Klasse von Problemen. So verwendet die x86 Architektur die von den meisten PCs und Servern verwendet wird verwendet eine Speicherverwaltungseinheit welche die linearen Adressen, die von Software verwendet und referenziert werden, in physische Speicherblöcke im Direktzugriffsspeicher übersetzt. Während dieses Vorgangs aktualisiert die Speicherverwaltungseinheit einige Statusinformationen zu der jeweiligen linearen Adresse in den Seitentabellen, die sie für diese Übersetzung verwendet. Da dieser Übersetzungsvorgang relativ zeitaufwändig ist werden diese Übersetzungen im Übersetzungspuffer zwischengespeichert um Zugriffe auf den Direktzugriffsspeicher zu beschleunigen.

Allerdings ist das Verhalten dieses Übersetzungspuffers bewusst nicht spezifiziert und die Dokumentation verweist explizit darauf, dass er seinen Inhalt jederzeit unaufgefordert leeren kann. Dies hat zur Folge, dass die Übersetzung einer linearen Adresse durch die Speicherverwaltungseinheit entweder die Statusinformationen in den Seitentabellen aktualisiert oder nicht, abhängig davon ob die entsprechende Übersetzung im Übersetzungspuffers zwischengespeichert ist. Wenn dieser Fall während der Aufzeichnung einer virtuellen Maschine auftritt kann dies dazu führen, dass der Ausführungspfad während der Ausführungswiedergabe von dem der ursprünglich aufgezeichneten Ausführung divergiert, wenn das Gastbetriebssystem den nichtdeterministischen Inhalt der Seitentabellen liest und abhängig davon einen Ausführungspfad wählt. Dies führt dazu, dass die Ausführungswiederholung letztendlich fehlschlägt, da die aufgezeichneten nichtdeterministischen Ereignisse nicht mehr zum korrekten Zeitpunkt wiedergegeben werden können, da dieser nur auf dem ursprünglichen Ausführungspfad definiert war, was zur Folge hat, dass auch der deterministische Zustand zwischen diesen Ereignissen nicht korrekt wiederhergestellt werden kann.

Das Ziel dieser Arbeit ist es ein System zu entwickeln, welches eine Ausführungswiederholung inklusive des im vorherigen Absatz beschriebenen Nichtdeterminismus erlaubt ohne vollständig auf die Leistungssteigerung durch die Verwendung von hardwareunterstützter Virtualisierung während der Aufzeichnung verzichten zu müssen und die Leistung dieses Systems sowohl während der Ausführungsaufzeichnung als auch der Ausführungswiederholung zu evaluieren.

Um dieses Ziel zu erreichen werden wir die Ausführungskomponente des SimuBoost Systems, die als Teil des *KVM* Moduls im Linux Betriebssystemkern implementiert ist, erweitern um jegliche Änderung an den Seitentabellen des Gastsystems innerhalb der virtuellen Maschine zu überwachen, gleichwohl ob diese durch das Gastbetriebssystem oder die Speicherverwaltungseinheit vorgenommen werden. Wir erreichen dies indem wir die Hardwarevirtualisierungstechnologie der geschachtelten Seitentabelle verwenden, die als *EPT* (engl. *Extended Page Table*) in aktuellen Intel x86\_64 Prozessoren implementiert ist, um die Speicherbereiche die die Seitentabellen des Gastsystems enthalten als nur-lesbar markieren und jeder Befehl, der auf diese Speicherbereiche schreibend zugreift mithilfe der Emulationssoftware für x86 Befehle, die Teil des KVM Moduls ist, emulieren. Des Weiteren modifizieren wir *QSIMU*, eine Abspaltung des *QEMU* Emulators die SimuBoost zur Ausführung der Ausführungswiederholung verwendet, um diese zusätzlichen Informationen die während der Ausführungsaufzeichnung gesammelt wurden zu verwerten und die gleichen Änderungen an den Seitentabellen auch während der Ausführungswiederholung vorzunehmen.

Unsere Resultate zeigen, dass dieser Ansatz eine vielversprechende Lösung des beschriebenen Problems bietet. Die nötigen Modifikationen am bestehenden Programmcode waren von relativ geringem Umfang und unser modifiziertes System ist in der Lage auch solche Ausführungen zu wiederholen für die dies zuvor unmöglich war. Während wir keinen messbaren Einfluss auf die Laufzeit der Ausführungswiederholung feststellen konnten, variiert der Einfluss auf die Laufzeit der Ausführungsaufzeichnung stark in Abhängigkeit von der Zusammensetzung der Last der aufgezeichneten Ausführung. Berechnungsintensive Ausführungen verlaufen mit der selben Geschwindigkeit wie bei einer Aufzeichnung ohne Unterstützung für nichtdeterministische Speicherverwaltungsereignisse. In einem konstruierten Minimalbeispiel für einen schlechtestmöglichen Fall konnten wir jedoch eine Verlangsamung um 350% feststellen. Für reale Anwendungsbeispiele liegt der Leistungsabfall zwischen diesen Extremen, tendiert jedoch zum besseren Ergebnis.

# Contents

| Abstract Deutschsprachige Zusammenfassung v |                          |                                                                                                                                               |                                  |  |  |

|---------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

|                                             |                          |                                                                                                                                               |                                  |  |  |

| 1                                           | Intr                     | oduction                                                                                                                                      | 3                                |  |  |

| 2                                           | Background               |                                                                                                                                               |                                  |  |  |

|                                             | 2.1                      | Virtual Memory                                                                                                                                | 7<br>8<br>10                     |  |  |

|                                             | 2.2                      | Virtual Machines                                                                                                                              | 11<br>11<br>13                   |  |  |

|                                             | 2.3                      | QEMU/KVM                                                                                                                                      | 15                               |  |  |

|                                             | 2.4                      | Record and Replay                                                                                                                             | 16                               |  |  |

| 3                                           | Ana                      | lysis                                                                                                                                         | 19                               |  |  |

|                                             | 3.1<br>3.2<br>3.3<br>3.4 | TLB Induced Non-Determinism in RecordingImpact of Non-Deterministic TLB Behavior on ReplayPreliminary Measurements and Related WorkConclusion | 20<br>21<br>24<br>25             |  |  |

| 4                                           | Desi                     | gn                                                                                                                                            | 27                               |  |  |

|                                             | 4.1<br>4.2               | Recording                                                                                                                                     | 27<br>29<br>31<br>33<br>33<br>33 |  |  |

| <b>CONTENTS</b> |

|-----------------|

|-----------------|

| 5            | Imp                          | lementation                    | 35 |  |  |  |

|--------------|------------------------------|--------------------------------|----|--|--|--|

|              | 5.1                          | SimuBoost                      | 35 |  |  |  |

|              | 5.2                          | Recording MMU Events in KVM    | 36 |  |  |  |

|              |                              | 5.2.1 Data Storage             | 36 |  |  |  |

|              |                              | 5.2.2 Context Switches         | 37 |  |  |  |

|              |                              | 5.2.3 Changes to Page Tables   | 37 |  |  |  |

|              |                              | 5.2.4 Emulation in KVM         | 38 |  |  |  |

|              |                              | 5.2.5 Resuming Guest Execution | 40 |  |  |  |

|              | 5.3                          | Replaying MMU Events in QSIMU  | 40 |  |  |  |

|              | 5.4                          | Conclusion                     | 41 |  |  |  |

| 6            | Eval                         | uation                         | 43 |  |  |  |

|              | 6.1                          | Test Setup                     | 43 |  |  |  |

|              | 6.2                          | Qualitative Evaluation         | 44 |  |  |  |

|              | 6.3                          | Quantitative Evaluation        | 45 |  |  |  |

|              |                              | 6.3.1 Methodology              | 45 |  |  |  |

|              |                              | 6.3.2 Benchmarks               | 46 |  |  |  |

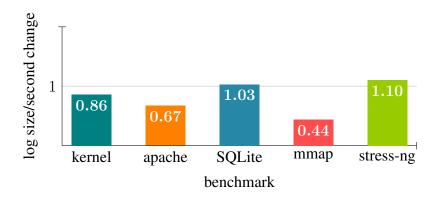

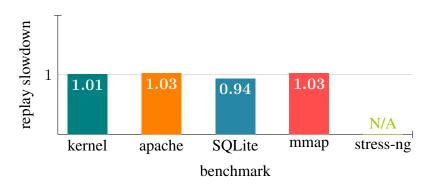

|              |                              | 6.3.3 Results                  | 48 |  |  |  |

|              | 6.4                          | Conclusion                     | 53 |  |  |  |

| 7            | Conclusion 55                |                                |    |  |  |  |

|              | 7.1                          | Future Work                    | 56 |  |  |  |

| Bibliography |                              |                                |    |  |  |  |

| Ap           | Appendix: Raw Benchmark Data |                                |    |  |  |  |

2

# Chapter 1

# Introduction

Record and replay systems aim to provide an important tool in debugging by allowing the user to record a single faulty execution of a program and subsequently replaying this execution accurately without the replay being affected by any external inputs. This causes any bug that is being tracked down to occur in exactly the same way every time and greatly simplifies the debugging experience. It can even allow the debugger to inspect an earlier state in the programs execution, working backwards in time from the symptoms of a bug to its cause.

Due to the prevalence of virtual machine software in today's computing environments, it has been proposed to apply the same principle of record and replay at the machine instruction level, allowing the recording and subsequent replay of a virtual machine. This can not only be useful for debugging but also as a tool in intrusion detection because the software that records the virtual machine will be unaffected if the virtual machine itself is compromised.

In order to avoid performing a full copy of the virtual machine after every instruction, record and replay systems exploit the fact that most machine instructions are deterministic in nature. Only events that are non-deterministic such as interrupts need to be recorded and the state of the recorded system between these events can be recreated by simple executing the deterministic instructions.

To provide acceptable performance when recording a full virtual machine, record and replay systems for virtual machines such as SimuBoost [1] make use of the hardware-assisted virtualization capabilities of modern processors and execute a majority of the recorded system's instructions directly on the host hardware. While this severely improves the performance of the recording, it also introduces new problems. The x86 architecture that is used by most personal computers and servers utilizes a memory management unit (MMU) to translate linear memory addresses that are used by the software running on the system into physical locations in RAM. While doing this, it also updates some status information in the page tables that define these translations. Because this operation is relatively slow, the translation lookaside buffer (TLB) is used, which caches these translations to speed up RAM accesses.

However, the operation and contents of the TLB are non-deterministic, which can cause the status of the translations that the MMU manages to either get updated or not, depending on the presence of the given translation in the TLB. If this happens during a recording of a virtual machine, it can cause the corresponding replay to diverge from the code path that the recording took when the operating system in the virtual machine inspects this non-deterministic state in the page tables and chooses different actions depending on their contents. This will then cause the replay to fail when its state deviates from the recording and the following non-deterministic events cannot be lined up correctly.

Our goal in this work is to develop a system that allows a replay of a virtual machine that is faithful to the previously recorded execution, including the non-determinism caused by MMU changes to page tables depending on the TLB's state, while still reaping the benefits of hardware assisted virtualization and evaluate the impact that this has on the performance of the system during both recording and replay.

To achieve this goal, we extend the recording component of the SimuBoost system, which is implemented within the Linux kernel's KVM module to track any change that either the guest operating system in the virtual machine or the MMU makes to the page tables. We achieve this by using the *extended page table (EPT)* hardware-assisted virtualization extension in recent Intel x86\_64 CPUs to mark the memory that contains the page tables as read-only and emulating any write to them using the emulation facilities present within KVM. We then modify QSIMU, the fork of the QEMU emulator that SimuBoost uses to perform the replay, to process this additional information gathered during the recording and recreate the same changes to the page tables during the replay.

Our work shows that this approach is a feasible way to record these events, with only small additions to the existing recording code being needed. We confirm that it allows the replay of workloads that would previously fail to replay correctly. While there is no measurable impact on the performance of the replay, our implementation causes varying amounts of slowdown to the execution during recording, with the magnitude of the slowdown greatly depending on the characteristics of the recorded workload. While computationally heavy workloads suffer no slowdown, the worst-case that we evaluated slows down by over 350%, with real world applications falling between these extremes.

4

### Outline

In Chapter 2 we introduce the concepts of paging and the operation of the x86 MMU and TLB and explain more details on the operation of virtual machines, record and replay systems and various implementations of the latter. In Chapter 3 we analyze the origin and impact of the observed problem and the degree to which existing record and replay solution acknowledge or solve it. In Chapter 4 we present the design of our proposed solution and weigh it against alternatives that we considered. After this, we elaborate on some of the details of our implementation in Chapter 5 before evaluating its correctness and performance using multiple benchmarks in Chapter 6. Last but not least we summarize our work, offer a conclusion and suggest potential improvements for future work in Chapter 7.

## Chapter 2

### Background

In this chapter we will introduce the concepts and mechanisms that build the foundation on which our work builds and which are necessary to fully describe the problem we intend to solve and our proposed solution. First we give a short introduction to virtual memory and the Translation Lookaside Buffer. Next we introduce virtual machines and describe the differences between emulation and hardware-assisted virtualization. Lastly we describe how QEMU and KVM implement these concepts and how Record and Replay of virtual machines can be used to facilitate debugging applications and operating systems.

### 2.1 Virtual Memory

In order to provide isolation between different processes running on the same system and allow a single system to run more than one instance of a program, modern processors implement what is called paged virtual memory.[2] In this mode of operation the memory addresses that a program accesses are not treated as literal locations in physical memory but are instead treated as so called *linear addresses*. The MMU of the system translates these linear addresses into physical addresses which describe a specific location in physical memory which is then used by the given instruction. These translations — or mappings — of linear to physical addresses are different for each running process and are configured by the operating system's kernel. This prevents malicious or malfunctioning processes from accessing other processes' memory because the kernel only adds translations to physical memory locations that the process is allowed to access. It also avoids conflicts between different instances of the same program because while the addresses that are hard-coded in their binary are identical and thus

both instances intend to use the same memory addresses. However, by using paged virtual memory their mappings refer to different pages in RAM. The set of mappings that define the linear addresses that a program is able to use and which physical memory locations back these addresses is called the program's *address space*.

#### 2.1.1 Page Tables

The translations from linear to physical addresses are described by a set of cascading tables in memory. We will now briefly describe the process by which the MMU uses these tables to translate linear to physical memory addresses on current x86\_64 systems. While these tables are organized in levels and the tables on each level have a distinct name that can be seen in Figure 2.1 on page 9, we will refer to all of them as *page tables* unless otherwise noted because they are structured identically and the differences between them will not be of importance to our work.

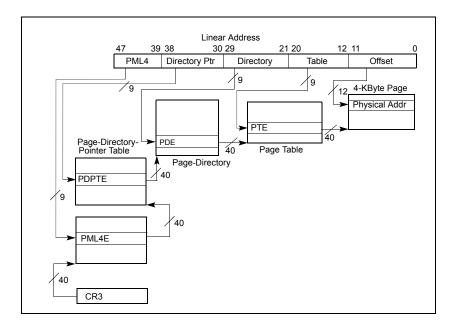

The physical address of the first of these page tables is recorded in the processor's CR3 register at all times. The MMU loads this table from memory and selects one of its entries using the first 9 bits of the linear address as the index. Each entry contains the physical address of the next table in the page table hierarchy as well as a set of status flags. The MMU then loads the next table from the physical memory address given in this entry and uses the next 9 bits of the linear address to select an entry in this table. On current x86\_64 systems the translation of a single linear address uses up to 4 page tables each of which contain 512 entries. The last PTE contains the address to a physical memory location of a fixed size, called a *page frame*, and the remaining bits of the linear address are used as an offset into this page frame. The specifics of this process can vary depending on the configuration of the processor — e.g. in 32bit mode there are only two or three levels of page tables, they each contain 1024 32bit entries instead of 512 64bit entries and each step uses 10 bits of the linear address to select a PTE — but the general principle remains the same.

To allow the operating system to keep track of which regions of memory are in active use by a process the MMU maintains a set of status flags in each of the PTEs. Two of these flags will be of interest to our work, the *accessed* and *dirty* bits. The accessed bit is set by the MMU whenever it uses the corresponding PTE to translate a linear to a physical address but before it returns the resulting address. The dirty bit only exists in the entries of last level page table and is set by the MMU when the memory that the entry references is written to. Together these two bits allow the operating system to make an informed decision on which contents to evict from memory when the amount of available memory runs low. Data that

Figure 2.1: Linear Address Translation with 4-Level Paging.[2, p. 124]: Every 9 bit interval of the linear address selects an page table entry in the current page table and 40 bits of the 64 bit sized page table entry are used to locate the next level page table until the final 4 KiB sized page frame is located.

has been read from persistent storage, e.g. a file, and whose PTE does not have the dirty bit set can simply be dropped from memory. Only the information from where the data can be restored when the process tries to access it again needs to be recorded. On the other hand if the memory is dirty it has to be written to persistent storage before being dropped from memory. In both cases the accessed bit helps inform the decision which specific pages to evict from memory. (The operating will usually decide to keep data that has been accessed before under the assumption that it will be accessed again.)

Another status flag and arguably the most important one is the *present* bit which signifies if the page table entry is considered valid. If this bit is cleared the MMU will not use this entry to translate a linear address and will instead upon encountering it raise an exception, the so called *page fault*. This allows the operating system to overcommit memory by clearing the present bit when creating a page table for an application. As long as no linear address that uses the page table entry in questing is accessed the operating system does not need to allocate any memory to hold its contents or even load data from a hard disk to fill this memory. Only when the memory is first accessed will a page fault be raised, invoking the operating system's kernel which will either fill in the corresponding page table entry, allocate a page frame for this linear address and set the present bit to 1 or

terminate the application if it is not allowed to access memory at the given address.

When the operating system determines the currently running process has exhausted the amount of time that it was allowed to run, it determines which process should run instead. Once it has done this, it switches the active address space so that the new process is able to access its memory at the linear addresses that it expects. This is performed by simply writing the physical address of the top-level page table to the CR3 register. This process is called a *context switch*. The same operation may take place when a process uses a system call to interact with the operating system kernel, except that the kernel's address space is activated, though this depends on the implementation of the kernel.

#### 2.1.2 The Translation Lookaside Buffer

While paged virtual memory brings some important advantages as detailed above, a naive implementation would also come with a significant performance penalty. Accesses to memory are relatively slow compared to data that is already in a processor cache or even a register, with a single access requiring up to two orders of magnitude more time to complete[3] and for each access to memory, up to four additional memory accesses to page table entries have to be performed when paging is being used. This would be prohibitively expensive, especially because every instruction in a running program is also referred to by and loaded from a memory address. In order to avoid quintupling the time it takes to load each instruction and putting more pressure on the CPU caches by having to cache each individual page table entry, the *Translation Lookaside Buffer (TLB)* is used. The TLB caches translations from linear addresses to physical addresses. After the MMU has resolved a translation of a linear address, determined it to be a valid translation and set the accessed and dirty bits in the corresponding page table entries it creates a TLB entry for this linear address. The TLB entry contains the physical address that the translation points to as well as some of the status flags oft the page table entries that were used in the translation, indicating among other thins if the linear address is read-only or writable, as well es the dirty bit of the last level page table entry.

At the time the TLB entry is created the linear address is implicitly readable because TLB entries are only created for valid translations from linear to physical addresses. Furthermore the state of the accessed bit is not cached explicitly by the TLB because each page table entry used by the corresponding translation already has its accessed bit set by the MMU at the time the TLB entry is created. While the MMU creates TLB entries automatically it is up to the operating system to ensure that they remain consistent with the contents of the page tables. For example when removing an entry from a page table or marking an entry read-only, the MMU must be notified of this fact. If the operating system does not flush the relevant TLB entries the MMU might use the cached translation from the TLB for a future access to the linear address, potentially ignoring the changed permissions. Whether this happens or the changed permissions from the page tables are used depends on the size and exact behavior of the TLB which is generally implementation defined. [2]

### 2.2 Virtual Machines

Many computer system resources are underutilized because the applications that run on them are either idle for longer periods of time or only run on demand. However the isolation of different services on individual systems is often desired, for example for security or compatibility reasons. In order to solve this conflict virtual machines (VMs) [4] can used to allow these applications to run on the same physical machine while maintaining the required isolation between them. This is used extensively in cloud computing infrastructure to improve hardware utilization while at the same time providing isolation between the individual machines that might be rented out to different customers. A virtual machine allows an unmodified operating system to run as an application on another operating system while keeping it under the illusion that it is running on its own physical hardware. To do this a hypervisor or virtual machine monitor (VMM) implements the interface (i.e. I/O devices, memory, CPU,...) that a physical machine provides to the operating system while preventing individual virtual machines — also called *guest systems* — from influencing each other or the *host system*. The hypervisor runs the guest system as an unprivileged application and employs either emulation, hardwarevirtualization or a combination of both to handle the privileged operations that the guest wants to perform. An example for such a privileged operation is setting and modifying the active page table hierarchy as that allows controlling which parts of memory the running application can access, as we explained earlier. We will now give a brief explanation of both emulation and hardware-assisted virtualization and their use cases.

#### 2.2.1 Emulation

When the hypervisor *emulates* [4] the guest instructions it does not run them directly on the hardware but instead performs different operations while providing the same results to the guest as if its code had been run unmodified. There are multiple reasons why a hypervisor has to emulate some or even all of the guests

instructions. For example the guest might be compiled for a different instruction set, making it impossible to run it directly on the existing hardware. Another reason would be that the instruction can't be executed by the guest if the hypervisor wants to maintain the isolation between guests and host. For example in the Intel x86 instruction set some instructions will cause errors if they are not run in protection ring 0 and some instructions will return different results depending on which ring they are executed from. If the guest were to run one of these instructions and receive an error it would behave differently compared to running on a physical machine so the instruction has to be handled by the hypervisor. However the hypervisor can't run the guest's code in ring 0 because that would give the guest control over the physical system. Instead the hypervisor analyzes the guests code and performs an analogous action that yields the intended result for the guest.

To return to our earlier example, we will explain what happens when the guest wants to change the active page table hierarchy to allow a different application inside the guest to run. This instruction can't be executed as is because page tables are accessed by physical addresses but the physical addresses that are visible to the guest are part of the virtual machine that the hypervisor simulates so the MMU would be unable to find the page tables. To conform with the guests expectations the hypervisor has to inspect the page tables that the guest has constructed and map the guest's physical addresses referenced in the page tables to the actual physical memory on the host that it uses to provide the guest's memory. It then re-creates these page tables using the correct physical addresses and finally informs the MMU about these new page tables. This process is called *shadow paging* and the page tables that are allocated by the hypervisor are referred to as *shadow page tables*.[4] Additionally the hypervisor has to keep track of any additional changes the guest makes to its page tables, mirroring them to the shadow page tables and replace any instruction by the guest that queries the active page table hierarchy to ensure that the guest only ever sees the page tables that it constructed itself. This ensures that for the guest the resulting state of the system is indistinguishable from the state if it's original page tables were being used.

There are multiple approaches to implementing an emulator for a given instruction set. In any case the hypervisor has to parse the guest's instructions and replace those which can not be executed directly by (potentially multiple) native instructions that can be executed directly. If the binary was compiled for a different instruction set every instruction has to be replaced. This can either be done by an interpreter that translates each instruction one by one as it is about to be executed or by translating bigger blocks of the binary to native code at once which are then cached and executed as needed. However both approaches come at a significant performance cost due to the need to decode and translate each original instruction. In the example above a single write to a register to activate a new set of page tables turned into the hypervisor reading all of the guests page tables from memory, transforming their contents and writing new page tables before performing this single write to a register. While some optimizations can be applied such as caching some of the generated page tables this has to occur on each context switch in the guest system resulting in a significant slowdown.

#### 2.2.2 Hardware-Assisted Virtualization

In order to avoid this slowdown associated with emulation, many processors and chipsets now implement hardware-assisted virtualization. Hardware-assisted virtualization adds additional instructions to the processor's instruction set that allow the hypervisor to run a large portion of the guests code directly without emulation. To do this the Intel VT-x hardware-assisted virtualization for example adds two new modes to the processor, VMX root mode and VMX non-root mode. The hypervisor runs in VMX root mode and can configure the behavior of the VMX non-root mode which the processor enters before executing a virtual machine. In VMX non-root mode the guest's code can be executed directly and the guest is able to use all protection rings 0 - 3. However, when the guest tries to execute privileged instructions it will be suspended and the processor will exit into VMX root operation and supply the hypervisor with information on which instruction the guest tried to execute. The hypervisor is then able to emulate the instruction and allow the guest to resume execution. This scheme of implementing virtual machines is known as trap and emulate. Some privileged instructions can be executed by the guest directly without intervention by the hypervisor. For example the guest is allowed to enable and disable interrupts directly but this setting does not affect the host or other virtual machines because it is stored in a structure for the specific virtual machine when the processor exits non-root operation and restored when entering the same virtual machine again. The hypervisor can also configure which instructions cause the processor to suspend the guest which allows the hypervisor a fine grained control over the guests state and can be used for debugging purposes.

While hardware-assisted virtualization offers better performance than emulation it also has some limitations. In general it is only possible to run guest systems that are compiled for the instruction set that the CPU supports natively using hardware virtualization.

#### The Extended Page Table

While the implementation of hardware-assisted virtualization outlined above describes the initial support for this feature that was available on x86\_64 CPUs, different levels of hardware-assisted virtualization have since been added which allow the guest to directly manage some resources that the hypervisor previously needed to emulate, such as the managing of the guest's page tables via shadow page tables.

To obviate the need for shadow paging newer x86\_64 processors by both Intel and AMD implement *Extended* or *Nested Page Tables*, respectively. [5] Though the technologies differ in details the basic concept is identical and we will now describe the Extended Page Table (EPT) which we also used in our implementation. The EPT is another set of page tables that is configured by the hypervisor. However unlike the regular page tables it does not map from linear to physical addresses but instead maps from what the guest considers its physical address space to the actual hardware's physical addresses.

When the guest wants to access a physical memory address the EPT is a walked by the MMU exactly like the regular page tables but the indices in the individual tables are derived from the guest physical address instead of the linear address. When the EPT is enabled the guest is allowed to manage its own page tables without intervention from the hypervisor because the CR3 register that stores the topmost page table's address is now part of the virtual machine's state that is saved and restored by the processor on transitions between VMX root and non-root mode and cannot affect other guests or the host. In order to translate a memory access to a linear address in VMX non-root mode the MMU will now first have to consult the EPT to translate the guest physical address of the top-most page table that is stored in the CR3 register to a real machine physical address and be able to load the guest page table. Then it will find the address of the next level page table using the normal process described in Section 2.1.1. However this page table is again referenced by a guest physical address which has to be translated using the EPT. This process is repeated up to 4 times after which the guest physical address of the desired memory location has been determined and can be translated to a machine physical address using the EPT. In order to avoid the overhead of loading up to  $4 \cdot 4$  page tables/EPT tables from memory the TLB also caches translations from (guest) linear addresses to machine physical addresses as well as translations from guest physical to machine physical addresses when the EPT is enabled.

If they are invalid for the requested access a page fault is raised directly with the guest otherwise the EPT is consulted. The entries of the EPT tables contain permission bits much like the regular page table and if the requested access is not allowed under the given permission (e.g. a write access where one of the

#### 2.3. QEMU/KVM

corresponding tables does not have the writable bit set or a read access where the present bit is not set) a VM exit occurs and an *ETP violation* which is the EPT equivalent of a page fault is raised with the hypervisor. The hypervisor is then able to modify the EPT to allow the access or emulate the instruction if it does not want to allow the guest direct access to the memory address or if the address is part of an memory-mapped I/O range of an emulated device.

This greatly improves performance because the hypervisor is not invoked for each context switch in the guest and as long as the location of the guest's memory in the physical address space remains constant (i.e. it is not swapped to disk or migrated to another physical machine) the EPT does not need to change. Later revisions of the EPT also include support for accessed and dirty bits within the EPT entries which allow the hypervisor to make better decisions on which parts of guest memory to write to persistent storage and remove from the EPT under memory pressure similar to how the accessed and dirty bits in the page tables are used by the operating system kernel.

### 2.3 QEMU/KVM

In this section we will give a high level overview of how QEMU/KVM implement the concepts described above to form a state of the art hypervisor under Linux. As the name implies the hypervisor is really separated into two parts, the *Kernel-based Virtual Machine (KVM)* which is part of the Linux kernel and QEMU which runs in user space.

The KVM kernel module [6] allows the Linux kernel to act as a hypervisor using hardware-assisted virtualization. It contains implementations for multiple architectures while exposing a common interface to the user space application managing the virtual machine. For example for the x86\_64 architecture KVM is able to utilize both the AMD SVM as well as the Intel VMX hardware extensions and implements shadow paging as well as nested paging using EPT/NPT with either being used depending on processor support and the configuration of KVM and the virtual machine. It also supports emulation of the targeted instruction sets which is used in cases where direct execution is not possible. However, KVM does not implement any emulated devices. It is instead intended to be used by a user space application that implements the rest of a virtual machine.

QEMU [7] on the other hand implements a hosted virtual machine monitor, i.e. it runs as an application on top of a regular operating system while executing a virtual machine. QEMU handles the emulation of devices and includes among others support for storage, memory, input, graphics and network devices. These

emulated devices each run in their own thread with another thread simulating the CPU of the virtual machine. This thread runs the *Tiny Code Generator (TCG)* [8], a binary translator that allows QEMU to execute both user space programs that were compiled for a different architecture as if they were running natively as well as — as described here — to run a full virtual machine for a guest system. In both cases TCG translates contiguous blocks of emulated application's instructions to an intermediary language, which is then either translated to the host's instruction set and executed directly or — if no backend for the second translation step is implemented — run by a generic interpreter for the intermediary language. If the system supports hardware-assisted virtualization QEMU is also able to utilize this support to improve the performance of the virtual machine, replacing the use of the TCG. On Linux this support is provided by the aforementioned KVM kernel module and execution of the CPU thread is implemented by calling into this module. The CPU thread then blocks while the execution of the guest's code is handled by KVM until it is either interrupted because an interrupt from an emulated device needs to be handled or until KVM returns control to QEMU, for example to handle a memory-mapped I/O request for one of the emulated devices.

### 2.4 Record and Replay

Often computer programs exhibit bugs that are exceedingly hard to find and thus fix because they happen non-deterministically. This can for example happen due to race-conditions in multi-threaded programs. Depending on how rarely the conditions that cause the bug to trigger appear it can take many invocations of the program until one of them even exhibits the unwanted behavior. However, the most commonly used scheme of debugging is cyclic debugging [9] whereby the program is executed multiple times with each execution narrowing down the suspected area in which the bug is located using breakpoints to inspect the state of the program at certain points. Unfortunately the effectiveness of technique is greatly reduced when the bug in question is triggered non-deterministically because it takes longer to find an execution of the program in the invalid state and a single bug can manifest itself in multiple ways at a later point in the execution making it hard to narrow down the scope of the debugging process. Some bugs are even so called "heisenbugs" which either disappear or alter their behavior when the program is being debugged. This can for example be caused by the debugger altering the timing of some operations, making threads of the same program run at a different speed relative to each other which can change the probabilities for race-conditions to manifest themselves.

In order to solve this problem and make it easier or even possible to find this class of bugs, *Record and Replay* [10] techniques can be used. Instead of only

#### 2.4. RECORD AND REPLAY

inspecting the state of the program at a given time and trying to deduce the cause of any inconsistencies the complete execution of the program is recorded and thus this exact execution can be replayed later in a deterministic way. This allows inspecting the state of the program can be inspected at any point in time and even work backwards across the timeline of the recording. By using Record and Replay a given bug only needs to be reproduced once and can then be analyzed in depth working backwards from the symptoms to the actual bug that caused them.

Because it would be prohibitively expensive to copy the entire step of the execution for each point in time, requiring both immense amounts of memory and slowing down the program enough to make it unusable, only non-deterministic events that affect the execution are recorded. The execution can then be replayed by injecting these events at the correct time and computing the deterministic operations inbetween these non-deterministic events normally. Examples of such events are the time at which a network packet is received or the data that a read from a hard drive returns. It is sufficient to record these non-deterministic events because the replay can reconstruct the state of the program by combining them with the deterministic instructions.

While the same concept of Record and Replay can be applied to whole virtual machines to allow debugging of hard to reproduce bugs even withing the operating system, performance has historically suffered due to the use of emulation until the widespread implementation of hardware-virtualization. Because the virtual machine exposes a different interface to the operating system a different set of non-deterministic events needs to be recorded to ensure that the execution of the whole system can be replayed deterministically. Examples of these events include the timing of interrupts, the data returned from emulated devices (e.g. network interfaces) or the count of the system timer.

Different implementations of Record and Replay for Virtual Machines have been proposed, operating at different levels of abstraction. ReVirt [11] uses UMLinux<sup>1</sup> [13] to run a modified Linux guest system as an unprivileged application on a Linux host, replacing privileged hardware instructions with system calls into the host kernel. This approach is however not very portable due to the requirement to modify the guest kernel. ExecRecorder [14] on the other hand utilizes the Bochs simulator that emulates a full x86 system at the hardware level, though at a significant slowdown.

With the growing prevalence of hardware-assisted virtualization extensions in common x86 hardware there have been efforts to leverage these additional capabilities to lower the performance impact of recording a virtual machine execution increase

<sup>&</sup>lt;sup>1</sup>Not to be confused with the similarly named User Mode Linux[12]

the compatibility with different guests. ReTrace [15] builds on the VMware Workstation's hypervisor and allows the replay to occur on a different machine from the recording. This allows the recorded system to continue operating normally without being affected by increased load from the replay. Building on top of this, Aftersight [16] uses QEMU to replay the execution, greatly increasing the amount of architectures the system can run on and allows the replay to run in parallel to the recorded execution to allow analyzing the replay, e.g. for intrusions via buffer overflows, while the system is running but without having to run these potentially slow analyses on the production system itself. The approach taken Crosscut [17] on the other hand allows transforming a VMware Workstation recording at machine instruction level into a replay at a different level of abstraction, for example allowing the user to replay a single process that has been identified of being of interest after the recording was created.

Other applications for record and replay have been proposed as well, with V2E leveraging heterogeneous record and replay like Aftersight though in this case the recording is implemented with hardware-assisted virtualization in KVM while the replay is performed in TEMU, a tool for dynamic binary analysis built on top of QEMU [18], to analyze malware without the malware being able to detect and evade this analysis and SMP-ReVirt [19] building on the Xen hypervisor to enable record and replay of multiprocessor virtual machines by guaranteeing the ordering of accesses to shared memory to stay consistent during replay.

# Chapter 3

# Analysis

It can be difficult to debug and fix hard to reproduce bugs using only cyclic debugging because the cause of the bug is generally not known and in some cases it is even difficult to impossible to reproduce the problem with a debugger attached to the program in question. So called Heisenbugs seem to actively avoid inspection because their occurrence are influenced by subtle differences in timing. Employing record and replay allows analyzing a single execution in depth without changing the timing of external events or needing to reproduce the bug in question in each debugging cycle. It has been proposed [11] to apply the same principle to whole virtual machines to allow easier debugging of such bugs in the operating system kernel or even monitor production systems, which often run in virtual machines today, via recording. This would allow debugging bugs without having to reproduce them even once and has also been suggested as an improvement to intrusion detection [11] because an attacker might be able to alter log files and other traces of his presence on the attacked system but would be unable to hide his presence in the recording of the virtual machine that exists on the host.

Despite these advantages the application of record and replay techniques to virtual machines has not been widely deployed yet and the solution that was commercially available as part of the VMware Workstation hypervisor [15] has even been removed in a later version[20]. It is clear that in order for record and replay of virtual machines to be useful in practice one of the most important concerns if not the most important concern is the accuracy of the replay. In order to keep the amount of data that needs to be recorded as low as possible, all current implementations of record and replay only log non-deterministic events that could otherwise not be reproduced only from the current state of the system at the time of replay. There is however a class of non-deterministic events that can be caused by incoherencies between the TLB of x86 CPUs and the state of page tables in memory that none of the implementations we mentioned in Section 2.4 cover.

In this chapter we will explain the cause of these events as well as their impact on record and replay solutions. In the rest of our work we will describe our implementation to enable recording these events for single-processor hardwareassisted virtual machines as a part of Simuboost [1].

### 3.1 TLB Induced Non-Determinism in Recording

As mentioned in Section 2.1.1 the MMU does not ensure consistency between the page tables in RAM and the TLB entries that it creates to decrease the overhead caused by virtual memory. When the MMU translates a linear address to a physical address and TLB entry exists for this linear address, the page tables in RAM are not consulted even if their permission bits or the physical address that they reference have been changed. Instead the TLB entry is used directly to resolve the physical address and assert if the current process is allowed to read, write or execute the referenced memory. The same principle applies to the accessed and dirty bits of the page tables. The MMU only sets these bits in the relevant page table entries that were used to translate the current linear address when they are not already set in the structure that it used to perform the translation. If the instruction that caused the translation writes to the linear address and the dirty bit needs to be set it is already set in the relevant TLB entry, it will not be set in the last page table entry. The accessed bit never gets set when a TLB entry is used for the translation because every TLB entry is implicitly considered accessed because the MMU only creates entries in the TLB when translating an access to the given linear address at which point it set the accessed bit in the page table entries.

This implies that if the guest operating system fails to invalidate the TLB when clearing either the dirty or accessed bit in one of its page table entries, the state of these bits after a future access to the linear address depends on implementation defined behavior of the TLB. While this behavior can still be deterministic for a system running on bare hardware, it is certainly non-deterministic when the TLB is being shared between the host system and potentially multiple guests in virtual machines. At any point the guest's execution can be preempted, for example because its scheduled time slice elapsed or because it tried to execute a privileged instruction that trapped into the hypervisor. At this point any amount of host code can run or the host can schedule another virtual machine to run on the same CPU. All of these actions utilize virtual memory and will create new entries in the TLB for any translations that are not already present, possibly evicting the TLB entries that were created from translations in the recorded VM. The host might even sometimes explicitly flush the TLB depending on what operations it performs at this time. Also, according to Intel's documentation [2, p. 1215] on the behavior

of the TLB in their processors, "[a] logical processor may invalidate any cached mappings at any time".

Operating systems generally flush the relevant TLB entries when clearing the dirty bit from page tables because they need to accurately track which pages have been written to. This is needed to avoid data loss from erroneously discarding these memory contents when the system runs out of RAM because they are considered *clean*, i.e. saved to persistent storage. Some operating systems, such as for example Linux since version 3.16 and up to the present day, do not apply the same rigor to keeping the state of the accessed bits consistent with the TLB. [21] When the Linux kernel clears the accessed bit in a page table entry, it does not flush the corresponding TLB entry to avoid the performance hit that would result from the TLB miss if the address is accessed again and the MMU has to read the relevant page tables from memory. The inconsistency between the TLB and page tables is being tolerated in this case because the state of the accessed bits is only used as a heuristic to predict which pages will likely be accessed again in the future and should be kept in memory and the chance of a misprediction due to this inconsistency is considered "relatively low" by the authors of the change due to the TLB being flushed regularly due to e.g. context switches between applications.

The result of this non-determinism is that if the TLB contains an entry for a particular linear address during the recording of the virtual machine but does not contain such an entry during the replay, an additional accessed or dirty bit will be set in at least one page table entry in memory during replay. If the conditions are reversed, a bit will be set during the recording but not the replay. It should also be noted that even if the TLB's behavior was deterministic and an entirely separate TLB could be instantiated for a given virtual machine, the TLB that is used during replay can still differ from the one that was used during recording, such as in a heterogeneous record and replay solution in which e.g. the recording is performed using hardware virtualization and the replay using emulation.

# 3.2 Impact of Non-Deterministic TLB Behavior on Replay

Some evaluation metrics for implementations of record and replay have been outlined in [22], which include:

• **probe effect**, which measures how much the original execution is slowed down due to the recording compared to a normal execution that is not being recorded

- **log size**, the amount of data per instruction that is generated by the recording and needs to be stored in the replay log

- **replay slowdown**, the difference in run-time between the recorded execution and the replay

- **replay accuracy**, which describes how accurately the replay matches the recorded execution at the chosen level of precision

A record and replay system will generally have to make trade-offs between these variables. For example implementations that record at machine instruction level such as ReTrace[15] or SimuBoost[1] use periodic checkpoints at which the state of the virtual machine is recorded while the states between these checkpoints are computed during the replay. If checkpoints are created more often during recording, both the probe effect and log size increase. On the other hand the replay can proceed faster if it can be parallelized such as in SimuBoost where each checkpoint interval is can be emulated on its own machine, drastically lowering the replay to "seek" closer to the part of the execution that they are interested in without waiting for the intermediate state to be replayed.

As mentioned before, only non-deterministic events need to be logged during the recording. These events can be further separated into two categories according to [19]:

- Synchronous Events These events always appear at the same point in the instruction stream but their output is non-deterministic and needs to be recorded. Examples include the x86 RDTSC instruction which returns the number of processor cycles since the system was started or the data that devices returned for I/O instructions.

- Asynchronous Events These events occur at a non-deterministic point in time but their content can be deterministic. An example for this are interrupts, which cause a deterministic change, e.g. changing certain registers but occur at non-deterministic time.

When using hardware-assisted virtualization to run the guest during the recording, most synchronous and asynchronous events can easily be tracked by configuring the hardware to cause traps into the hypervisor when they occur, which will then log them. Synchronous events can simply be recorded and when replayed in order when the corresponding instruction that caused them is encountered (e.g. when using hardware virtualization the hypervisor would configure the hardware to trap

#### 3.2. IMPACT OF NON-DETERMINISTIC TLB BEHAVIOR ON REPLAY 23

on these instructions). Asynchronous events on the other hand have to be handled differently. For these events a unique identifier that specifies the exact point in the execution at which they occurred needs to be recorded. Because the instruction pointer is not enough to identify a specific point in the execution (consider the existence of loops for example), this so called *landmark* has e.g. been described in [23] to also include the state of registers and flags, the branch counter or as in SimuBoost the retired instruction performance counter. Only when this landmark is hit — i.e. the current state of the machine during replay matches the landmark — will the asynchronous event be injected into the replay. Implementing a record and replay system that is able to correctly replay any given guest is extremely challenging and it is impossible to ever test every single combination of host, hardware and guest. Because of this it can be helpful to include additional state in the landmark that can be used to verify that the replay did not diverge from the recording.

While the accuracy of the replay is immensely important to the usefulness of a record and replay system, some (theoretical) inaccuracies might be tolerated to improve the other areas of concern. If the difference in accessed bits would not affect the replay accuracy it could be tolerated if the impact on the probe effect of accurately tracking these events was to high. For example writes to the guest's memory could in theory be discarded if it was known ahead of time that the guest will never read this memory location. It has however been observed in [24] that even "single bit in the state of the replayed system can potentially alter its execution path". This problem is further exacerbated by the fact that the divergence between recorded execution path and replay usually does not happen directly but is only later influenced by such a small change.

These differences between recording and replay can not only change the layout of virtual memory because a different page will be evicted or swapped to persistent storage depending on the state of the accessed bits (e.g. Linux uses a complicated algorithm [25] that among other factors takes into account how often a file has been accessed), but also alter the flow of execution. If a process accesses memory that was swapped out in the replay but not the recording, it will trigger a page fault, causing additional code to run to re-load the affected data. This can then lead to landmarks being missed if the counters that are being used no longer match the recorded value, causing the replay to abort because asynchronous events can no longer be injected correctly. The same result can even be expected just because the kernel read a different value from the page table entry at the time a landmark was supposed occur, causing the register contents to differ from the landmark.

Accurately tracking the changes to accessed as well as dirty bits is also important to enable the use of record and replay to debug the guest operating systems memory management code. While we mentioned earlier that the specific behavior of not flushing the TLB when clearing accessed bits is an optimization and the flush is normally performed after clearing a dirty bit, this of course only applies to guests that behave correctly. To be useful as a debugging tool however, a record and replay implementation must also be able to precisely replay a system that does not behave correctly.

### **3.3** Preliminary Measurements and Related Work

Our tests with a virtual machine running Ubuntu 16.04.1/Linux 4.8.10 show that depending on the amount of RAM that is allocated to the virtual machine, inconsistencies in the state of the accessed bits happen with different probabilities. They can be observed regularly even just during the boot process of the guest that is being recorded using the current SimuBoost system if the virtual machine is given 256 MiB of RAM. This subsequently leads to landmark misses during replay, while the same does only occur extremely rarely at 4 GiB of RAM. We believe this happens because the Linux kernel's page aging algorithm that clears the accessed bits and later checks which have been set again by the MMU to determine which pages are actively being used is invoked more frequently when the system only has a low amount of free RAM available.

Despite the fact that this issue seems comparatively easy to observe in practice, we are not aware of any performant record and replay solution that aims to track and replay these events accurately. Of the implementations that we mentioned in Section 2.4, only ExecRecorder is able to do so completely, by virtue of using the Bochs simulator that implements the TLB in software and is thus not influenced by any state outside the guest, can behave deterministically for each execution and uses the same TLB implementation for both recording and replay. Implementations like ReVirt that run entirely as a user mode application while re-using the host's resources are unable to track these events because they operate only on virtual memory. The paper that describes SMP-ReVirt is the only work we could find that mentions the problem. It uses shadow paging and avoids any non-determinism by flushing the TLB after performing any changes to the shadow page tables that the MMU uses and being able to mirror the state of the accessed bits deterministically to the guest's page tables. This does cause a recorded execution to behave differently from a normal virtual machine that would nowadays run using hardware virtualization and thus changes the behavior of the guest. For example it would be impossible to debug a problem in the guest's memory management code that is being caused by missing TLB flushes on real hardware because the recorder adds those flushes behind the guest's back.

It is possible that the implementations of record and replay that we examined

simply did not notice this problem because they used a different portion of the guest's state to define their landmarks. However this does not negate the problem's existence but could hide it or make its it less likely to cause a landmark miss during the replay.

### 3.4 Conclusion

In this chapter we have identified how optimizations of TLB flushes can in some instances introduce non-determinism into the state accessed and dirty bits inside the page tables in RAM. We also discussed how this can affect record and replay systems that aim to accurately replay an entire virtual machine by causing the memory contents of recording and replay to diverge and how even these minuscule changes can introduce larger derivations in the replay or cause it to fail completely by changing the course of the execution of the replay, leading to landmarks being missed.

While this effect can be observed even when recording simple executions such as the boot process of a Linux distribution, we were unable to find any record and replay system that aims to eliminate it by accurately logging and replaying these events. While some systems are unaffected by this problem, either because they operate at a higher level in virtual memory or because they operate at a lower level and emulate their own implementation of a TLB, to our knowledge none of the implementations that replay at machine instruction level and use hardware-assisted virtualization to limit the probe effect are able to handle these events correctly.

Investigating a way to log these TLB induced non-deterministic events using hardware virtualization and evaluating the impact this has on the evaluation metrics for record and replay systems outlined in Section 3.2 will be the goal of this work.

## **Chapter 4**

## Design

This chapter concerns itself with the design of our proposed solution to log all writes of dirty and accessed bits by the x86 MMU due to the non-determinism inherent in the specification of the TLB using hardware-assisted virtualization. Our design will not not only be influenced by the problem itself but also by the choice to find and evaluate a solution using the hardware-assisted virtualization capabilities in modern Intel x86\_64 CPUs and implement this solution as part of SimuBoost.

Our primary goal is to enable tracking the setting of accessed and dirty bits with very high accuracy for any unmodified guest, even if the guest does not issue TLB flushes on some of the changes it makes to its page tables, with a secondary goal of keeping the overhead of our implementation over the existing record and replay capabilities that SimuBoost provides to an acceptable level.

We will now discuss both the recording and replay of MMU events in detail, explaining our proposed design while contrasting it with other possible solutions that we discarded.

## 4.1 Recording

The problem of recording non-deterministic events can be generalized as follows: The guest that is being recorded must not be allowed to be aware of any event that the hypervisor is unaware of. In many cases this can be achieved by configuring hardware-assisted virtualization to trap into the hypervisor when these events occur. However even with the virtualization extensions that are available in current x86\_64 CPUs it is not possible to configure the virtual machine in a way that causes only the setting of accessed and dirty bits to trap into the hypervisor but not other accesses to the guest's page tables. This leaves two possible options to achieve the goal stated above:

Either

1. The guest system must be prevented from reading from its own page tables by any means as long as their state is not synchronized with the TLB. This restriction applies both to the currently active page tables as well as any other memory that has been used as a page table and not has been reused in for another purpose before the attempted read. At the same time the MMU can be allowed to freely access the currently active page tables and write the accessed and dirty bits to them.

or

2. The MMU must be prevented from writing to the guest's page tables without the hypervisor being informed. The guest on the other hand can be allowed to freely read the state of the accessed and dirty bits because it is never able to be influenced by an event that the hypervisor has not logged yet.

The first option would allow an optimal solution (in the amount of events that need to be logged) to the problem of non-determinism induced by the accessed and dirty bits to be implemented by to detecting when the page tables are being read by the guest and at this specific point log their state to the replay log, allowing them to be replayed exactly. While this might introduce small differences in the memory contents of recording and replay because the changes to the guest's page tables that are never read do not get logged, we would still prefer it because we believe it offers the best performance overall in all 4 metrics outlined in Section 3.2. As mentioned there, such small differences between the state of recording and replay at a specific point could be tolerated in some cases to improve performance, if it can be proven that they will not cause any changes further down the line. In any case where these bits might either be set or cleared, but are never read by the guest and thus can never influence its state and the execution, they would not necessarily need to be logged, just like the contents of any memory that is only written and never read could be discarded from the replay log.

However, the only way of guaranteeing these conditions on current x86\_64 hardware while preserving the isolation of virtual machine and host system that we are aware of is the use shadow page tables. When shadow paging is being used the hypervisor already has to make sure that any changes the guest makes to its page tables are reflected in the shadow page tables and thus needs to protect the guest's page tables. Additionally, it could also protect the guest's page tables from reads and log the setting of accessed and dirty bits when it mirrors them to the guest's

### 4.1. RECORDING

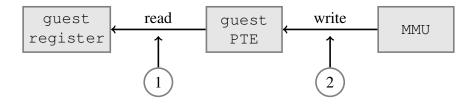

Figure 4.1: Overview of the point at which each of the proposed methods intercept the and log the accessed and dirty bits being set.

page table on demand as described above. Sadly, the use of shadow paging would also come at a significant performance cost. (The use of the EPT mechanism for nested paging has been credited with a performance improvement over shadow paging of up to 48% for MMU intensive workloads [5])

When the EPT is in use, the MMU uses the guest's page tables directly and the access permissions that are set in the EPT apply to both regular guest accesses and MMU accesses. For the first option described above this would imply disallowing all read access to the guest's page tables, which would cause any address translation by the MMU to trap into the hypervisor, resulting in a significant performance loss. This caused us to focus our efforts on the second option, developing a more brute-force system that intends to log every single accessed and dirty bit being set. Some of the steps that are required to successfully log MMU writes of these status bits to the page tables are however similar to those that are needed to implement shadow paging, though less work needs to be done by the hypervisor. We will now give an overview of the individual steps of our design for the recording phase.

## 4.1.1 Tracking Guest Page Tables

The first necessary task to needs to be completed to accurately record changes to the guest page tables is locating them in the guest's memory and keeping track of any changes that the guest makes to them while it is running.

### **Context Switches**

This requires trapping into the hypervisor when the guest sets the CR3 register to a new top-level page table and recursively iterating through all the entries that are marked as present in the table it points to, recording the location of each encountered guest page table.<sup>1</sup> How often this needs to be repeated depends on the current configuration of the virtual machine's CPU, which influences how many layers of page tables are used to translate linear addresses, from 2 layers in 32bit operation to up to 5 layers in upcoming CPUs, support for which is already present in the Linux kernel.

#### **Changes to Active Page Tables**

The hypervisor also needs to ensure that any subsequent changes that the guest makes to the currently active page tables also cause a trap, allowing the hypervisor to adjust its list of guest page tables. The reasons for this are twofold.

- 1. It might have to track additional page table that the guest added at lower levels of the hierarchy by either replacing a present entry or adding a new entry.

- 2. It is also important to notice when a page of memory is no longer used as a page table. This is most easily implemented at this time because the first point already requires changes to the guest's page tables to trap into the hypervisor.

Making sure that the dropping of page tables by the guest is tracked is important because otherwise unrelated memory will be assumed to contain guest page tables and writes to this memory would cause the hypervisor to assume that the guest changed a page table, interpreting this memory as page table entries leading to unpredictable results. It is important that changes to page tables are handled efficiently as this is a very frequent operation in many operating systems. When a program forks off a child process, their page tables are set up to share all data currently available to the parent process read-only and any writes they perform to their memory will lead to a page fault in the guest to duplicate the affected data and adjust the page tables to allow the write.

#### **Old Page Tables**

Consideration also needs to be given to the page tables of the previously active page table hierarchy. It could be advantageous to remember a number of previously

<sup>&</sup>lt;sup>1</sup>Care needs to be taken not to run into an endless loop because of a common implementation trick in operating system kernels called *recursive page* tables, in which the last entry of the top-level page table points to itself greatly simplifying the implementation of accessing the page tables (which are normally only referenced using physical addresses) from the kernel using linear addresses.

### 4.1. RECORDING