# Interconnect Adapter State Migration for Virtual HPC Clusters

Diplomarbeit von

# cand. inform. Simon Sturm

an der Fakultät für Informatik

Erstgutachter: Zweitgutachter: Betreuende Mitarbeiter: Prof. Dr. Frank Bellosa Prof. Dr. Hartmut Prautzsch Dipl.-Inform. Marius Hillenbrand Dr. Jan Stöß

Bearbeitungszeit: 19. Juni 2012 – 18. Januar 2013

Ich erkläre hiermit, dass ich die vorliegende Arbeit selbständig verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel verwendet habe.

Karlsruhe, 18. 01. 2013

# **Deutsche Zusammenfassung**

Live-Migration von virtuellen Maschinen wird als eines der mächtigsten Werkzeuge im Bereich der Systemvirtualisierung angesehen. Es kann insbesondere in Rechenzentren erhöhte Fehlertoleranz durch Ausfallsicherungssemantiken und dynamische Lastverteilung in einem Cluster ermöglichen.

High Performance Computing Infrastructure as a Service (HPC IaaS) legte in der letzten Zeit erheblich an Bedeutung zu. Es verspricht Elastizität und Flexibilität in den Bereich des High Performance Computing (HPC) zu bringen. Im Gegensatz zu traditionellen *Ethernet*-basierenden Cloud Rechenzentren, benutzen HPC Cluster typischerweise hochperformante Verbundnetzwerktechnologien mit intelligenten Netzwerkkarten, wie beispielsweise Infini-Band. Sie erreichen eine erstklassige Kommunikationsleistung durch aggressives Auslagern des Protokollhandlings, OS-bypass-Techniken und erweiterte Funktionen wie Remote DMA. Obwohl die neueste Generation solcher Karten bereits Hardwarefunktionen zur Verfügung stellen, die ihre Virtualisierung erleichtern (bspw. mit SR-IOV), ist die Unterstützung für transparente Live-Migration noch immer eine ungelöste Fragestellung der Forschung.

In dieser Diplomarbeit stellen wir ein neuartiges Design vor, welches gasttransparente Live-Migrationen von virtuellen Maschinen ermöglicht, denen eine virtuelle Instanz einer selbstvirtualisierenden Hardware direkt durchgereicht wurde. Wir nutzen dabei gezielt die Selbstvirtualisierungsfunktion der Hardware aus um die eigentliche Zustandsmigration der durchgereichten Instanz durchzuführen. Obwohl wir uns auf HPC IaaS fokussieren, kann unser Ansatz auch in anderen Szenarien verwendet werden. Eine prototypische Evaluation, die auf einem *Mellanox ConnectX-3 VPI InfiniBand* Adapter und dem Linux KVM Virtual Machine Monitor (VMM) basiert, beweist, dass sich dieses Design in aktuelle VMMs integrieren lässt.

# Abstract

Live migration of virtual machines is considered as one of the most powerful tools available in the context of machine virtualization. Specifically in data centers, it can enable higher fault tolerance through fail-over semantics and better load-balancing within a cluster.

High performance computing infrastructure as a service (HPC IaaS) has gained substantial momentum in the recent past, as it promises to bring elasticity and flexibility to the area of high performance computing (HPC). In contrast to traditional *Ethernet*-based cloud data centers, however, HPC clusters typically use high-speed interconnects with intelligent network adapters, such as *InfiniBand*. They provide cutting-edge communication performance and use aggressive protocol offloading, OS-bypass techniques, and advanced features such as remote DMA. While the latest generation of such cards already provides hardware capabilities to ease their virtualization (with SR-IOV, for instance), support for transparent live migration of these self-virtualizing adapters is still an open question in virtualization research.

In this thesis, we propose a novel design enabling guest-transparent live migration of a virtual machine configured with a directly assigned virtual device instance of self-virtualized hardware. We take advantage of the self-virtualization features to perform the actual state migration of the assigned instance in software. Despite we focus on HPC IaaS, our approach can be also employed in other scenarios. A prototypical evaluation, based on *Mellanox's ConnectX-3 VPI InfiniBand* HCA and the Linux KVM virtual machine monitor (VMM), proofs that this design integrates with recent VMMs.

# Contents

| De | eutsc | he Zus  | sammenfassung                                    | 7        10        12        1aaS        15        15        15        17        20        20        20        21        22        21        22        23        24        HCAs        27        28        31        31        32        33        33        33        33        33        33        33        33        33        33        33        33        34        35 |

|----|-------|---------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A  | ostra | ct      |                                                  | vii                                                                                                                                                                                                                                                                                                                                                                           |

| 1  | Intro | oductio | on and Motivation                                | 3                                                                                                                                                                                                                                                                                                                                                                             |

| 2  | Bac   | kgrour  | nd and Analysis                                  | 5                                                                                                                                                                                                                                                                                                                                                                             |

|    | 2.1   | High I  | Performance Computing in the Cloud               | 5                                                                                                                                                                                                                                                                                                                                                                             |

|    |       | 2.1.1   | Challenges of Virtualization for HPC IaaS        | 7                                                                                                                                                                                                                                                                                                                                                                             |

|    |       | 2.1.2   | VMM-based I/O Virtualization                     | 10                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 2.1.3   | Self-Virtualizing Devices                        | 12                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 2.1.4   | Interconnect Network Virtualization for HPC IaaS | 14                                                                                                                                                                                                                                                                                                                                                                            |

|    | 2.2   | Challe  | enges of Live Migration for HPC IaaS             | 15                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 2.2.1   | State involved in Live Migration                 | 15                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 2.2.2   | Live Migration Strategies                        | 17                                                                                                                                                                                                                                                                                                                                                                            |

|    | 2.3   | InfiniE | Band as HPC Interconnect                         |                                                                                                                                                                                                                                                                                                                                                                               |

|    |       | 2.3.1   | Subnets and Network Management                   |                                                                                                                                                                                                                                                                                                                                                                               |

|    |       | 2.3.2   | Queue Pairs and Transport Services               |                                                                                                                                                                                                                                                                                                                                                                               |

|    |       | 2.3.3   | Remote DMA (RDMA)                                | 24                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 2.3.4   | Fabric Partitioning                              | 24                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 2.3.5   | Resource Sharing Logic of Self-Virtualizing HCAs | 25                                                                                                                                                                                                                                                                                                                                                                            |

| 3  | Des   | ign     |                                                  | 27                                                                                                                                                                                                                                                                                                                                                                            |

|    | 3.1   | Overv   | iew                                              | 27                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 3.1.1   | Live Migration for HPC IaaS                      | 28                                                                                                                                                                                                                                                                                                                                                                            |

|    | 3.2   | Migra   | tion Strategies                                  | 31                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 3.2.1   | Local Migration Strategies                       | 31                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 3.2.2   | Global Migration Strategy for HPC IaaS           | 32                                                                                                                                                                                                                                                                                                                                                                            |

|    | 3.3   | Migra   | tion Assistance Interface (MAI)                  | 35                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 3.3.1   | State Stabilization                              | 36                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 3.3.2   | State Migration                                  | 37                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 3.3.3   | Emulation Assistance                             | 37                                                                                                                                                                                                                                                                                                                                                                            |

|    | 3.4   | Hardw   | vare State Migration                             | 38                                                                                                                                                                                                                                                                                                                                                                            |

|    | 3.5   | InfiniE | Band specific Hardware State Migration           | 40                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 3.5.1   | Endnode Address and Port Configuration Migration | 41                                                                                                                                                                                                                                                                                                                                                                            |

|    |       | 3.5.2   | Slave Resource State Migration                   | 43                                                                                                                                                                                                                                                                                                                                                                            |

| 4   | Prot         | otypical Evaluation                            | 45 |

|-----|--------------|------------------------------------------------|----|

|     | 4.1 Overview |                                                |    |

|     | 4.2          | Evaluation Platform                            | 46 |

|     |              | 4.2.1 Virtualization with KVM and QEMU         | 47 |

|     |              | 4.2.2 Mellanox ConnectX-3 VPI                  | 48 |

|     | 4.3          | MAI Support in QEMU                            | 49 |

|     |              | 4.3.1 Guest Device Migration Framework in QEMU | 51 |

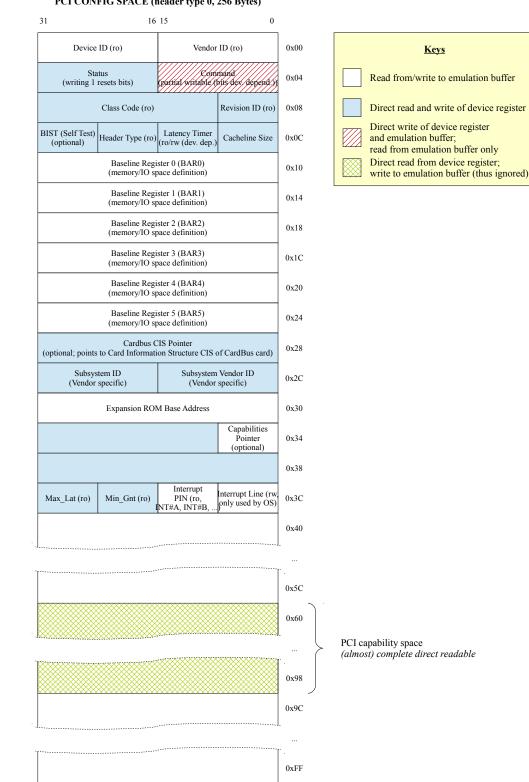

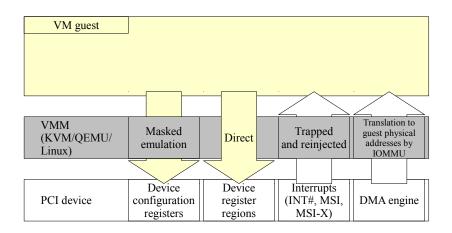

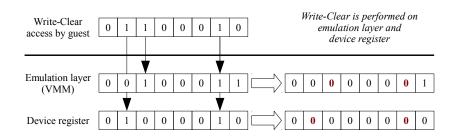

|     |              | 4.3.2 PCI Pass-Through in KVM/QEMU             | 51 |

|     |              | 4.3.3 Extending QEMU's pass-through code       | 56 |

|     | 4.4          | MAI Integration in Master Driver               | 57 |

|     | 4.5          | Evaluating MAI Integraton                      | 58 |

|     | 4.6          | Summary                                        | 60 |

| 5   | Rela         | ated Work                                      | 61 |

|     | 5.1          | Ethernet-based Approaches                      | 61 |

|     | 5.2          | InfiniBand-based Approaches                    | 63 |

| 6   | Con          | clusion                                        | 67 |

|     | 6.1          | Future Work                                    | 68 |

| Glo | ossai        | ry and Abbreviations                           | 69 |

| Bił | oliog        | raphy                                          | 75 |

# **1** Introduction and Motivation

Virtual High Performance Computing (HPC) clusters, or also referred to as High Performance Computing Infrastructure as a Service (HPC IaaS), is an upcoming trend in the computer service industry. Renting a scalable virtual HPC cluster on-demand instead of operating and owning a physical cluster by oneself promises new possibilities and opportunities for users and providers. However, HPC IaaS combines two different developments in computer science with different and colliding key aspects: (1) Machine Virtualization and (2) HPC. Virtualization focuses on machine abstraction, thus providing the guest an abstract view of the machine on which it is actually running. In contrast to this, HPC benefits from using huge amounts of parallel computing and memory resources as directly as possible to achieve high performance. Typical HPC applications are computational fluid dynamics, seismic data analysis, online transaction processing, and real-time control systems, amongst others [14].

Machine virtualization has developed over time and its beginning was primarily marked by a publication of Popek and Goldberg in the early 1970s [61, 62]. They provided a set of formal requirements for a computer architecture to enable machine virtualization. During that time, *IBM* was one of the first companies that commercially published a virtual machine environment for the *IBM System/370* mainframe [18]. It allows customers to consolidate multiple guest systems on a single physical host.

Machine virtualization is the key technology enabling IT infrastructure as a cloud service. Advanced features, such as migration, sever the binding of a virtual machine (VM) to a particular physical host. With live migration, which is seen as one of the most powerful tools, a VM can be moved to another host almost seamlessly - even while it is currently running. It enables higher fault-tolerance and is a useful feature for dynamically balancing load within a datacenter.

Nowadays, virtualization is becoming increasingly relevant to the area of HPC. Since hardware virtualization features became more and more publicly available, for instance with *Intel's VT-x* and *AMD's AMD-V* technology, performance oriented virtualizing is possible: They enable running a VM at almost native speed since most of the guest instructions can run directly on the physical hardware. This way, virtualization provides scalability and flexibility for HPC, as shown in recent research [21, 24, 33].

Supercomputing requires high performance interconnect technologies, since such computers are typically built from a large number of computer nodes that are interconnected with each other. The interconnect network becomes a vital part, since supercomputers achieve their performance from extreme computing parallelism and huge memory resources. For this purpose, these high-speed interconnects, such as *InfiniBand*, provide cutting-edge commu-

nication performance by utilizing aggressive protocol offloading, OS-bypass technologies, and advanced features such as remote DMA (RDMA). With HPC IaaS, however, those technologies substantially complicate the task of transparently migrating a VM to another host. While the latest generation of such cards, such as the *Mellanox ConnectX-3 VPI InfiniBand* host channel adapter [42], already provides hardware self-virtualization to ease their use in virtualization scenarios with SR-IOV [59], for instance, transparent support for live migrating directly assigned devices is still an open question in virtualization research. Direct device assignment promises best I/O utilization results in virtualization [15] and migration transparency is the important key to provide full flexible cloud infrastructures services, because it removes the dependency to particular systems for the guest which support running on the according service.

In this thesis, we propose a novel design enabling guest-transparent live migration of a VM with a directly assigned virtual instance of self-virtualized hardware. For this purpose, we take advantage of the self-virtualization features of the hardware to perform the actual state migration of the assigned instance in software at the virtual machine monitor (VMM) layer. Despite we focus on HPC IaaS, we introduce our approach in a generic way, since we are confident that this approach is also a base for migrating states of other self-virtualized devices.

This thesis is structured as follows: We present some background information and analyze the challenges of device state migration in Chapter 2 on the facing page. We focus on self-virtualizing hardware in the area of infrastructure as a service (IaaS) and HPC. In Chapter 3 on page 27 we introduce our novel design. It consists of two orthogonal components that are composed together. The first component is a migration strategy and the second is a novel interface. Such a strategy coordinates the migration process in a way to enable migration transparency to the guest and also to remote nodes that are interacting through this device. The interface, that we call migration assistance interface (MAI), provides necessary mechanisms to a VMM to enable guest-transparent state migration of an assigned device. It utilizes the self-virtualization feature of the hardware to break up device state opaqueness. Additionally, we provide an *InfiniBand* specific slave device migration approach. In Chapter 4 on page 45, we evaluate our proposed design with focus on the integrability on Linux's KVM VMM stack. After that, we discuss related work in Chapter 5 on page 61 and contrast to our approach. Finally, in Chapter 6 on page 67, we conclude our work and summarize our results.

# 2 Background and Analysis

In this chapter, we provide some background and analyze challenges of live migrating virtual machines (VMs) to that a slave device of a self-virtualizing hardware is assigned. We focus thereby on the area of High Performance Computing (HPC), especially on the scope of HPC infrastructures as a cloud service. Since live migrating directly assigned devices covers a wide range of area, we present our analysis and background as generic as possible.

First, we provide relevant background on HPC as a cloud service in Section 2.1. After that, we point out how machine virtualization is utilized for HPC and what are the challenges for its implementation in Section 2.1.1 on page 7. In this section, we also analyze recent virtualization techniques, since machine virtualization covers resource virtualization of computing time, memory, I/O, and the high performance interconnect network. I/O virtualization is covered in more detail in Section 2.1.2 on page 10, because it imposes challenges for migration, especially to direct device assignment. After an introduction to self-virtualizing devices and an overview of their potential for HPC in Section 2.1.3 on page 12, we analyze the live migration process of virtual machines focused on virtual HPC clusters using self-virtualizing high performance interconnect adapters in Section 2.2 on page 15. Finally, we give a brief overview of *InfiniBand* and details of hardware-based *InfiniBand* adapter virtualization in Section 2.3 on page 20. Since we primarily focus our scenario on HPC clusters built with the modern *InfiniBand* interconnect, we shall introduce the concepts and properties of *InfiniBand*.

# 2.1 High Performance Computing in the Cloud

HPC in the cloud, also called HPC Infrastructure as a Service (HPC IaaS) [21], fuses HPC with the aspects of Cloud Computing. It delivers a flexible virtual HPC cluster as a service which promises more flexibility and reduced operating costs compared to a physical owned cluster. Furthermore, benefits of Cloud Computing are in general a better utilization, higher energy efficiency, and lower overall operation costs by consolidating multiple users on a single data center [13]. And because resources can be added or removed at a fine grain within short time periods, these resources can be matched to workload needs more closely [13].

Typical high performance applications are simulation, data mining, information access, or information integration [14]. Examples are computational fluid dynamics, seismic data analysis, online transaction processing, and real-time control systems [14]. One of the most no-

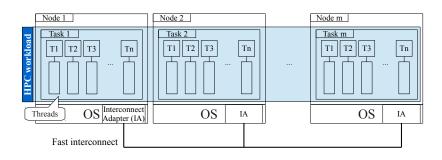

ticeable properties of HPC workloads is the high degree of computation parallelism. This parallelism is exploited by many computation threads which are spread over multiple processors and even multiple HPC cluster nodes. A fast interconnect network is used to exchange interim results and for task synchronizations during processing (compare with Figure 2.1). However, the characteristics of high performance workloads differ significantly from typical server or workstation workloads in their high dependence on computational performance, data storage access rates, as well as communication transfer speed and low latency [14, 19].

Figure 2.1: Typical runtime environment of an HPC workload

The term of Cloud Computing stands for a new trend of computing, the realization of the long-held dream of computing as a utility [13]. With new technologies, operators are now able to deliver services at different programming abstraction levels that can be quickly scaled on-demand and can be charged by usage [13]. Flexibility and illusion of infinity resources of the service are achieved by virtualizing the underlying resources and hiding the implementation details from the users [13]. By using cloud services, end-users do not have to operate the underlying infrastructure by themselves but rather can rent the needed services from a cloud provider and scale the resources on-demand. Actually, this underlying infrastructure, the datacenter hardware and software, is what is called a cloud [13]. Delivering a service at an abstraction level, which can be accessed by users on-demand by themselves, follows the Everything as a Service (XaaS) model [75]. The following three types are commonly known [63, 75]:

#### Software as a Service (SaaS)

delivers service in form of web applications [63]. Prominent examples are the Cloud Office Suites *Google Docs*<sup>1</sup> and *Microsoft Office*  $365^2$ .

#### Platform as a Service (PaaS)

delivers service in form of a programming interface on which web applications can be developed [63]. Because details about how data is stored or requests are processed are hidden by the interface, such applications can easily be executed on different scales of computing power and storage increments. *Microsoft Azure*<sup>3</sup>, for example, delivers PaaS [75] for several programming languages, such as *.NET*, *PHP*, or *node.js*.

<sup>&</sup>lt;sup>1</sup>http://docs.google.com

<sup>&</sup>lt;sup>2</sup>http://www.microsoft.com/ofice365

<sup>&</sup>lt;sup>3</sup>http://www.windowsazure.com

#### Infrastructure as a Service (laaS)

delivers service in form of an IT infrastructure and looks much like physical hardware [13]. For example, *Amazon EC2*<sup>4</sup> is a service providing VMs on which users can (nearly) control the entire software stack [13]. Furthermore, cloud storage belongs to this category [63] which delivers data storage as a service. Examples are *Amazon*  $S3^5$  and *Dropbox*<sup>6</sup> that can be used by end-users to store and access data from "everywhere".

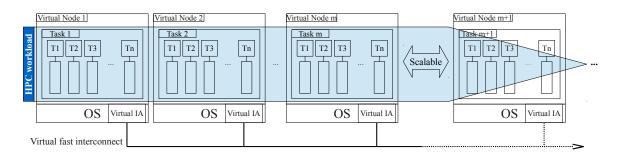

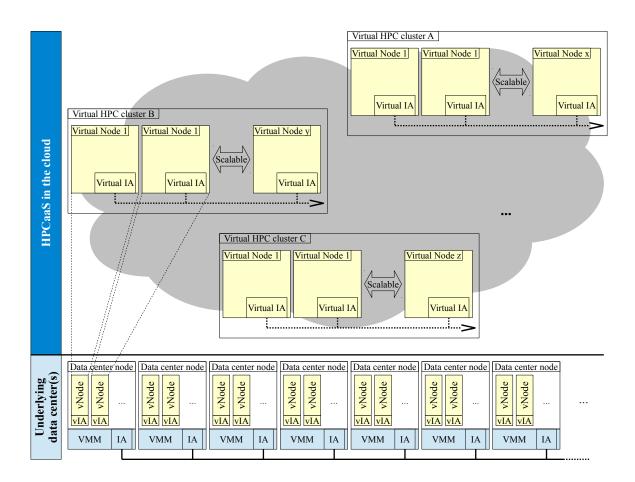

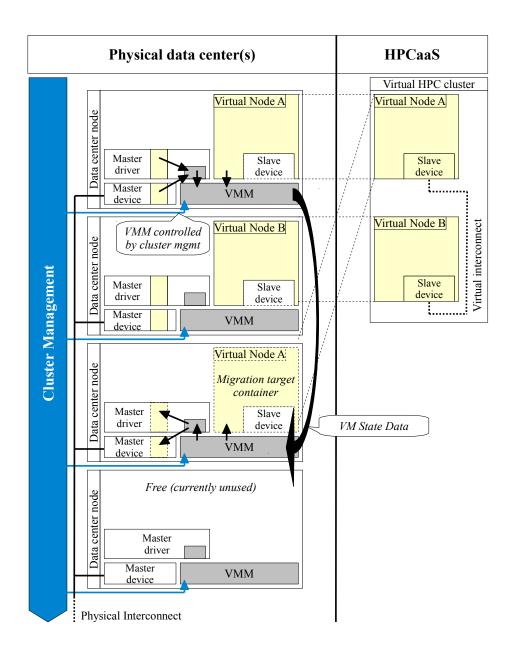

Figure 2.2: HPC IaaS pretends on-demand scalable HPC clusters to its users

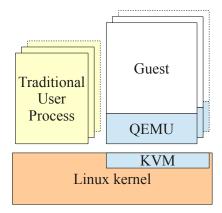

HPC IaaS itself is understood as a special type of Infrastructure as a Service. This service is implemented by using machine virtualization as well as interconnect network virtualization (see Figure 2.2 and Figure 2.4 on page 9) [21]. It provides users an on-demand scalable virtual HPC cluster which can be typically scaled on amount of virtual nodes, as well as memory and storage per node.

## 2.1.1 Challenges of Virtualization for HPC laaS

To deploy HPC IaaS, every HPC node and the interconnect of a virtual HPC cluster are virtualized. The main goal is to pretend an independent and scalable cluster that acts closely like a physical owned one. However, the requirements of HPC workloads differ significantly from typical server and workstation workloads which requires special optimizations in the virtualization setup. Typical HPC applications are compute intensive and task synchronization points often require equally placed compute units in the whole setup [21]. Also these workloads have higher demands on the underlying resources and on their guaranteed and timely delivery [21].

Virtualization is done by a hypervisor, also named as Virtual Machine Monitor (VMM) [44, 61]. It is a small program that virtualizes computing time, memory space, and I/O devices and therefore safely multiplexes the VMs onto the physical machine. Unfortunately, virtualization introduces overhead that potentially slows down the execution speed of a guest

<sup>&</sup>lt;sup>4</sup>http://aws.amazon.com/ec2

<sup>&</sup>lt;sup>5</sup>http://aws.amazon.com/s3

<sup>&</sup>lt;sup>6</sup>http://www.dropbox.com

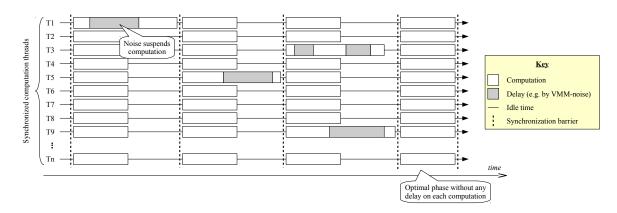

system compared to its speed running on a bare-metal system. Major keys to improve the guest performance are reducing the time of a processing unit spending in the VMM [15], minimizing the number of VMM traps needed by virtualization, as well as execute the VM, as long as possible, directly on the hardware [76]. This overhead is noticeable as delays in the VM execution, also called VMM-noise. Figure 2.3 provides an intuition on the potential effects of delays on workloads that are running with barrier-synchronized computation phases [60]: If noise introduces impact on a single thread, the computation phase of this thread is delayed and it will probably reach its synchronization point later than other threads of the workload. In such a case, the whole workload will run by this delay slower [60]. The likelihood of having at least one delayed thread per iteration increases, when the workload runs a large number of threads [60]. So, depending on the HPC workload, VMM-noise can cause fatal overall performance impacts and limits the scalability of parallel applications significantly [21].

Figure 2.3: Illustration of the impact of noise on synchronized computation (source: [60])

Most recent and popular processors, including the *x*86 models from *Intel* [27, Volume 3, Chapter 23: Introduction to Virtual-Machine Extensions] and *AMD* [2, Chapter 15: Secure Virtual Machine], provide hardware virtualization features that can be utilized by the VMM to decrease some of these performance costs [15]. Most compute unit instructions can be executed natively in the guest, with the exception of a few privileged operations that are trapped by the VMM [40]. However, this overhead carries almost no weight because typical HPC workloads seldom call them [40].

Furthermore, for instance, Hillenbrand et al. [21] reduce jitter, caused by timesharing and memory overcommitment, by assigning dedicated compute resources to a virtual node for exclusive access. Also memory assigned to a virtual node is completely allocated from physical memory of the VMM host which avoids preemption and paging activity by the VMM. Kocolski et al. [33] even implement a dual stack virtualization approach to fuse HPC workloads with traditional workloads on a VMM and to retain workload consolidation [33]. For this purpose, a single system is partitioned into zones to provide isolated environments for the different workload requirements [33]. Each zone has its own underlying system software to provide optimal behavior for its zone [33]. For example, a NUMA-based multi-processor

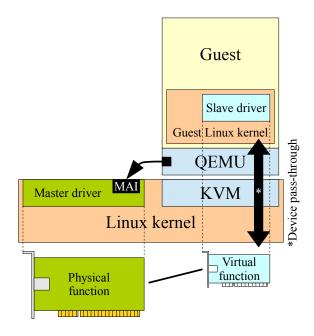

Figure 2.4: HPC IaaS is implemented by using machine virtualization

system is partitioned in such a way that an HPC VM is executed in an own HPC context on pre-selected processors and memory regions, while traditional applications are executed simultaneously on the rest of processors and memory [33]. The partitioning of the system is done in such a way that memory traffic is restricted as much as possible to the memory contained in the NUMA zones of the corresponding processors and their contexts [33]. Such an arrangement ensures that cross VM interference is minimized [33].

On the one hand exclusive resource usage leads to a decreased degree of virtual machine consolidation per VMM host, but on the other hand, due to the compute-intensive characteristics of HPC workloads, consolidation aspects are less relevant to HPC virtualization [44]. These aspects become beneficial whenever consolidation can be done with underutilized VMs running, for instance, traditional workloads.

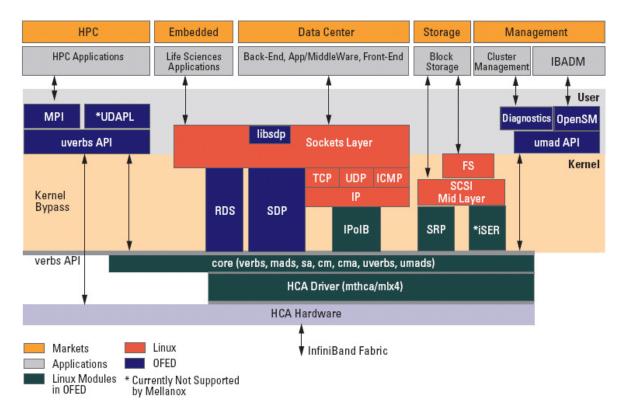

### 2.1.2 VMM-based I/O Virtualization

I/O virtualization (IOV) is still a challenge for non-HPC virtualization, especially for network devices [53]. Moreover, it becomes a central role in HPC IaaS: Former research, such as Kocolski et al. [33] and Gupta et al. [19], identified I/O network performance as the main potential performance bottleneck. Gupta et al. [19] even evaluated several recent IaaS clouds by running communication-intensive HPC workloads on them. Their results show that cost benefits of Cloud Computing versus operating a physical cluster are overturning in this scenario, caused by poor network performance. Furthermore, supercomputers are typically built with special interconnect technologies [79], such as InfiniBand [25] and Myrinet [47] (also see Section 2.3 on page 20). These interconnects match HPC demands of minimum guaranteed bandwidth and bounded access latency [21], as well as low performance overhead. They provide cutting-edge communication performance by using aggressive protocol offloading, OS-bypass technologies (operating system bypass), and advanced features such as remote DMA (RDMA). For instance, InfiniBand as such hardware, show in comparison to typical Ethernet adapters lower latency and higher throughput [29]. Further, OS-bypass technologies offer hardware interfaces directly to HPC workloads that can be used without any OS-involvement during communication [21]. The OS is only involved in establishing connections, registering memory buffers, and to ensure protection [21].

Because of these reasons, knowledge about IOV technologies performance and overhead is vitally important for deploying HPC IaaS. Additionally, HPC workloads running on a virtual HPC cluster would optimally benefit from direct access to communication buffers of the physical hardware. In such a case, an HPC thread can circumvent all layers of system software during interconnect communications [21]. Generally, recent IOV techniques that are provided by the VMM can be classified into four different characteristics [39] which have different advantages and disadvantages measured against different disciplines. Further, Table 2.1 on page 12 shows a short comparison overview of these techniques.

#### **Emulated devices**

An emulated device, also called full virtualized device, simulates completely an existing hardware in software. Therefore, the VMM traps I/O operations issued by the guest to such a device and completely emulates its behavior [76]. I/O operations may also be issued on a connected physical, possibly different, device by the VMM [82] if configured. For instance, packets from and for emulated network devices will be sent and received through a physical network adapter in the VMM host by using the MAC address of the emulated device [76].

Emulation is intended for compatibility [76], thus for use with guests that come already with a driver software for this device and for those guest where para-virtualization (see next technique) is not applicable. However, in terms of efficiency this technique offers the worst performance in comparison [39]. The behavior of the physical hardware has to be completely emulated by the VMM. Guests do not get any access to a underlying hardware directly. But on the other hand, full device emulation is applicable for all types of devices [39] and because only a pure software instance is instantiated per

device emulation instance, the number of emulated devices per VMM can easily be scaled [39].

#### Para-virtualized devices

On para-virtualizition, guests are aware of virtualization. Para-virtualized devices are intended to reduce dramatically the overhead caused by device behavior emulation (compare with previous technique). They employ an optimized pure software interface to the guest. Guests still do not have any direct access to an underlying hardware and I/O operations may also still be issued on an connected physical device by the VMM if configured. But various optimization of the VMM-guest interface in former researches [36, 70] promises huge performance improvements compared to traditional device emulation.

Unfortunately, recent implementations are focused on para-virtualized interfaces for block devices (e.g., storage), char devices, and network devices [39], but similar to device emulation, the number of para-virtualized devices per VMM can easily be scaled [39].

#### Accelerated para-virtualized devices

Accelerated para-virtualized devices are similar to para-virtualized devices, but provide guests direct access to I/O buffers of a physical underlying hardware [70]. It is commonly implemented with shared pages, which avoids copying of data between virtualized and physical device [53, 70].

For example, OS-bypass features of different I/O hardware can be utilized by the VMM to implement VMM-bypass [23, 40]. Another example is *Intel's* Virtual Machine Device Queues (VMDq) technology, which provides guests direct access to hardware network work queues [6, 53].

Performance measurements of systems implementing this type of technique [6, 40, 70] show that near direct I/O performance can be achieved [70]. Unfortunately, availability of this technique depends on the I/O hardware and the VMM which has to support the feature of this hardware [39]. Also the number of devices per VMM is limited by the hardware [39].

#### **Device pass-through**

Device pass-through, also called direct device assignment, means that a VM sees and interacts with a real device of the VMM host without software intermediary [82]. Main advantages are that nearly bare-metal performance is possible [15] and all device features are accessible by the guest.

However, hardware support in form of an IOMMU, an MMU for I/O devices, is at least required to ensure overall system security and stability [81]. It can pretend a device from accessing memory regions which are not belonging to its assigned guest, thus retaining the isolation between the VMs. In virtualized environments VMs have their own view of physical memory which typically distinct from the VMM host physical memory [82]. The IOMMU, such as *Intel's VT-d* [26] or *AMD's IOMMU* [1], can be

|           |                     | Efficiency | Characteristics<br>Applicability | Scalability |

|-----------|---------------------|------------|----------------------------------|-------------|

| Technique | Emulation           | Low        | All devices                      | High        |

| niq       | Para-virtualization | Medium     | Block, network                   | High        |

| ech       | Accel. para-virt.   | High       | VMM dependent                    | Medium      |

| E         | Device pass-through | High       | All devices                      | Low         |

Table 2.1: Comparison overview of IOV techniques (source: [39])

programmed by the VMM to translate physical memory addresses into guest physical addresses for each assigned device.

A limitation of bypassing the virtualization layer [82] is that the VMM looses completely control of the device and cannot observe the device state which imposes challenges to VM migration and device monitoring (we will go in a more detail in Section 2.2 on page 15) [53, 70, 83]. Also recent implementations require the pinning of the entire guest memory as long as no para-virtualized interface is implemented for the guest to map and unmap guest physical memory regions for a device [15, 72]. On the other hand, entire pinning introduces only minimal overhead [15] and we pointed out that, in terms of HPC IaaS, an approach to avoid paging activity of guest physical memory by the VMM pins this memory as well. Unfortunately, an assigned device cannot be shared with other VMs because the intermediate layer, which could perform resource multiplexing, is removed.

In terms of HPC IaaS, accelerated device para-virtualization and the device pass-through technique will perform well for virtualizing interconnect hardware since they permit HPC VMs to directly access memory buffers of the underlying hardware. These techniques further introduce only a minimal virtualization overhead and fulfill the major keys to improve HPC IaaS performance: reducing the time of a processing unit spending in the VMM and minimizing the number of VMM traps needed by virtualization (review Section 2.1.1 on page 7). Especially, device pass-through allows VMs to directly access I/O devices, without VMM intervention for data movement resulting in high performance [35].

## 2.1.3 Self-Virtualizing Devices

Recent hardware enhancements move more and more I/O virtualization logic from the VMM to the hardware [68], mainly to increase performance by reducing software virtualization overhead [28]. Early studies on self-virtualizing devices [68, 80], which appear as multiple separate interfaces, promised great performance improvements compared to software-based IOV techniques. Such natively shareable devices also defeat the drawbacks of direct device assignment, such as device sharing, potential underutilization, and scalability [35, 39]. These

devices typically provide unique memory space, registers, and interrupts for each exposed virtualized device while utilizing shared resources in a resource sharing logic [28].

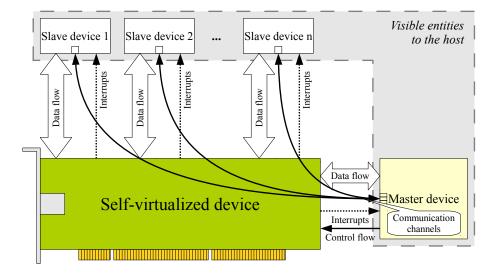

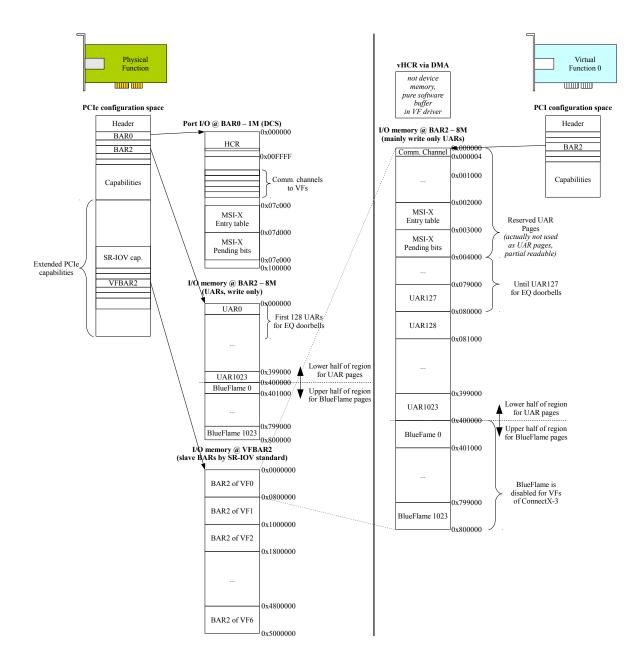

The former approach of Raj et al. [68], as well as the industrial standardization Single Root I/O Virtualization (SR-IOV) [59] by PCI-SIG [58], an organization that releases and develops the PCI [57] and PCI Express [55] standard, introduces an unequal device exposing scheme. This scheme distinguishes master devices, also called physical functions (PFs), from slave devices, also called virtual devices or virtual functions (VFs). Primarily, the master device provides a special interface to manage and configure multiple slave devices and a slave device is typically controlled by exactly one master device. Furthermore, each slave device is a lightweight device that is intended to be assigned to a VM. It owns resources necessary for data movement, including DMA, and a carefully minimized set of configuration resources [28]. In terms of device drivers, this distinction leads to separate drivers, one for master devices and one for slave devices. They do not have to be necessarily split into multiple driver programs, we also observed combined drivers that execute separate program flows depending on the device type (compare with *Mellanox ConnectX-3* driver architecture in Section 4.2.2 on page 48).

#### Figure 2.5: Principle of a self-virtualizing device using unequal device exposure and communication channels

In the SR-IOV standard, the basis on that we later introduce our migration approach, a slave function needs only hardware for accessing performance critical resources while nonperformance critical resources are emulated by the master driver [10]. The idea is that the master driver keeps control over the hardware while slave devices are lightweight access interfaces to performance critical resources. For this purpose the SR-IOV standard suggests to implement a communication channel between slave driver and master driver [28, 59]. VMM independence is achieved by a hardware-based or hardware-assisted implementation. With this channel, a slave driver is able to request operations through the master driver, as well as able to receive event notification from the master [10]. The master can then inspect slave requests and enforce policies concerning performance and security isolation as well as manage and monitor the resources used by slaves [10]. For example, a slave may request operation that would have global effects [28] or would affect isolation between VMs. In such a case the master driver could take appropriate actions or even simulate a behavior. Furthermore, the master driver may also need to notify changed resource status to its slaves (e.g., network port link status change) [10].

The actual resource sharing logic and management is implemented in hardware or software or even both. Typically, only the master driver has access to it for configuration (e.g., to assign an I/O buffer to a slave device). The implementation of the logic depends highly on the resource technology itself and on design decisions by the vendor of a specific hardware. For example, self-virtualizing *Ethernet* devices typically implement a physical Layer 2 switch with sort logic, to place incoming packets on receive queues dedicated to its target slave device [28, 68]. We will provide a more detail of *InfiniBand* interconnects in Section 2.3 on page 20.

In conclusion, using device pass-through with self-virtualizing devices has the following benefits: (1) (almost) no VMM interceptions needed when VMs are performing I/O on slave devices, (2) virtual guest can use device-specific hardware features that are only limited by the vendors design, and (3) VMM still would have the ability to control device sharing via a master driver interface. Unfortunately, assigned self-virtualizing devices still impose challenges to live migration, which is one of the most important virtualization features [83]. We go in a more detail in Section 2.2 on the next page.

## 2.1.4 Interconnect Network Virtualization for HPC laaS

Besides virtualization of the node resources computing time, memory, and I/O, each virtual HPC cluster should get the impression of using the interconnect network by itself [21]. Therefore, each virtual interconnect has to be isolated from others running on the same cloud. In general, the basic concept is similar between HPC IaaS and IaaS besides higher requirements on HPC IaaS, such as minimum guaranteed bandwidth and bounded access latency [21].

Interconnect network virtualization, or network virtualization in general, is typically done by partitioning the underlying interconnect network to isolate network traffic. Every virtual interconnect adapter is associated to a single partition and all nodes of a virtual cluster are bound to the same partition. However, how partitioning is implemented in detail, depends highly on the deployed interconnect technology and its available isolation techniques.

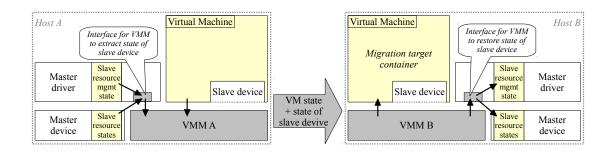

# 2.2 Challenges of Live Migration for HPC laaS

VM migration is seen as one of the most powerful features of virtualization [83]. It is used to move VMs to different physical nodes, for example for maintenance, high availability, consolidation, or load balancing. For these reasons, VM migration is an important tool for running and maintaining a cloud data center for IaaS (thus, for HPC IaaS, too). There are various different definitions of migration types [17, 64]. We categorize VM migration into cold and live migration (also called hot migration): Cold migration stands for the traditional way to migrate a VM by shutdown, moving its storage (if necessary), and then restarting the VM at the destination host [17, 64]. Live migration means relocation of a running VM to a destination host. Thus, it involves stopping the execution of the original VM, moving the VM runtime state to the migration target, adapting the configuration of the interacting environment, and at last resuming VM execution at the destination. Furthermore, a guest-transparent migration must not involve a guest into state restoration during migration. It has to be done completely at VMM layer.

We examine the feasibility of extracting and reconstructing a slave device state of a selfvirtualizing hardware at VMM layer in this thesis. Therefore, we give an overview of migration itself in this section. First, we discuss in Section 2.2.1 which components and states are included by a VM live migration. After that, we provide more detail about several migration procedures in Section 2.2.2 on page 17. Several designs of hardware that is migrated can add further requirements and dependencies to migration. For instance, such a design involves remote hosts in the environment configuration adaptation process. Therefore, we introduce two different kinds of migration strategies: (1) common migration approaches, which are applicable whenever hardware migration can be implemented transparent to interacting parties, and (2) cluster checkpoint approaches, whenever this transparency cannot be achieved.

### 2.2.1 State involved in Live Migration

A VM migration moves the machine state to a different host and adapts the configuration of the interacting environment, so that all involved parties can continue operation (almost) seamlessly after migration.

Adapting the configuration has to be done in order that all parties that are interacting with the VM retain connectivity and reachability to the VM after a migration. In terms of networking, this means that services provided by the VM are reachable after a successful migration in the same way as before and communication connections are maintained during the migration process or reestablished. For instance, approaches using conventional *Ethernet* migrate the MAC address of virtual network interfaces together with the VM instance. After the migration proceeding, communications stay alive as long as the migration destination is connected to the same subnet as the original machine [48]. In contrast to that, some popular interconnects in HPC, such as *InfiniBand*, are managed by a dedicated network instance that sets up routings and end point node addresses [25]. These addresses are bound to the physical hard-

ware, and thus, they cannot be migrated with the VM. In such a case, all involved parties in connectivity have to adapt to the new situation.

Like Nelson et al. [48], we differentiate between three kinds of VM state:

#### Virtual device state

State of virtual devices of the VM, such as computing unit, system devices, graphic adapters, network adapters, etc.

#### Location dependent resources

Location dependent resources are resources on the VMM host to which virtual resources are connected. For example, virtual networking is often associated with real network hardware that enables VMs to communicate with hosts on other physical machines.

#### **Guest memory**

Memory that is seen as physical memory by the guest.

In general, guest memory and virtual device states are just copied to the destination. Connections of virtual resources are reestablished to the new host-local resources. This reestablishment of connection is dependent on the resource itself. Earlier works propose solutions to solve issues on common full-virtualized or para-virtualized I/O, such as virtualized Ethernet networking and storage [7, 48]. However, despite former research on live migrating VMs configured with a pass-through device [17, 23, 30, 53, 71, 83], there is no generic approach available yet. As described in Section 2.1.2 on page 10, the VMM loses control of an assigned device and is typically not able to copy the device state to the target. Internal device states may not be accessible and state transitions may be still in flight at migration time [83]. But, as we pointed out, better results are achieved in terms of overall performance and lower virtualization overhead, whenever VM gets direct physical access to the device. However, the more state data is located or visible at the VMM layer, which applies for example to emulated and para-virtualized devices, the straighter forward should be the implementation of migration support. These correlations seem to be in conflict. Zhai et al. [83] identifies that approaches for device migration have to be addressed either with a VMM having device knowledge or with guests that are involved into migration to perform the device reinitialization. In the second case, a guest becomes aware of migration and thus, such approaches are not guest-transparent [17, 23, 30, 53, 71, 83]. Giving up guest-transparency restricts users to run modified driver, kernels, or even libraries in the guest that are implementing the mechanisms needed for reinitialization. Only they can guarantee errorless operation to the users, whenever migrations are performed in the data center.

However, as we show in Chapter 3 on page 27, self-virtualizing devices implementing an unequal device exposure (see Section 2.1.2 on page 10) can turn back control to the VMM while retaining the performance benefits of device pass-through. We consider these self-virtualizing devices as a hardware-implementation of accelerated para-virtualization, where a VMM can manage and control the resources of slave devices by using the master device interface.

### 2.2.2 Live Migration Strategies

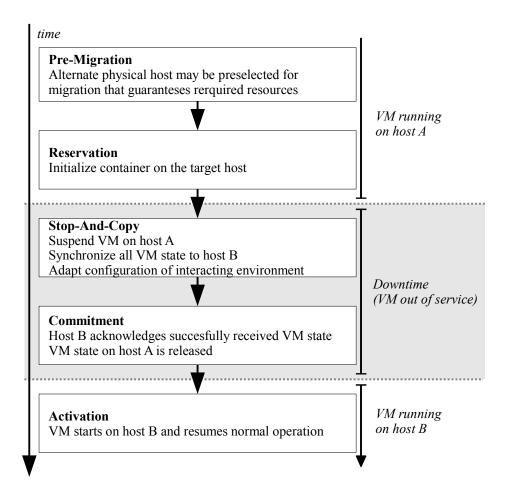

Like Clark et al. [7], we consider live migration as a transactional interaction between two VMMs (in the following: Host A and host B) that are involved into the migrating a VM. This interaction is done by a process of five common stages starting on host A that runs the VM that will be migrated to host B (also shown in Figure 2.6 on the next page):

#### Stage 1: Pre-Migration

A target host (called host B in the following) is selected that guarantees resource availability of host-local resources that are equal to the host-local resources currently connected to the VM [7].

#### Stage 2: Reservation

Host B confirms that the requested host-local resources are available and creates a VM container for the migration [7].

#### Stage 3: Stop-And-Copy

Host A stops the VM execution and copies the VM state into the container on host B [7]. Host B also establishes connections to its host-local resources. Actions to adapt the configuration of the interacting environment by the VMMs may also take place in this stage. At the end of this stage the VM is cloned to host B and both instances is stopped.

#### Stage 4: Commitment

Host B indicates to host A that the image was successfully copied and its copy is in a consistent state [7]. After that, host A may now discard its VM instance that was hold to resume it in case of migration failures [7].

#### Stage 5: Activation

Host B resumes VM execution.

Various improvements to the above-mentioned *stop-and-copy* approach were introduced to reduce the long service downtime due to the copy process of memory while the VM is stopped. Prominent examples are *pre-copy* [7], *pure demand-migration*, *post-copy* [22], and even combined hybrid techniques (see [7, 22] for an overview). These improvements try to shift a huge part of the memory page copy process into stages where the VM is running. Only a required minimum is then transferred at the Stop-And-Copy stage. For example, *pre-copy* copies memory pages in several iterations starting with copying all memory pages and followed by multiple iterations copying modified pages while the VM remains running prior the actual Stop-And-Copy stage. In doing so, the typical downtime is reduced, since only a small set of remaining modified memory pages has to be copied when the VM execution was stopped. *Pure demand-migration* migrates only a minimal required set at the Stop-And-Copy stage and transfers remaining memory pages on-demand on their first access after the VM is resumed on host B.

Nevertheless, recent improvements are not feasible with direct device assignment on common hardware platforms. For example, *pure demand-migration* suffers on devices that need

Figure 2.6: Five common stages of live migration (derived from [7])

to access data from guest memory pages that are not already migrated. Dong et al. [11] and Pan et al. [53] identified missing dirty page tracking in existing IOMMU that is needed to track memory pages dirtied by device access, such as DMA, and which is needed by pre-copy migration. Migrating an obsolete page state can cause fatal guest malfunction or even system crashes. To avoid this, the VMM needs knowledge of potential memory pages accessed by the device via device knowledge and resource monitoring or it has to view the whole guest memory as dirty. This in turn makes memory migration optimizations useless. Another problem may occur whenever the assigned device does not provide any suspend mode that still allows access by a driver to load and store the hardware state. Especially on devices using RDMA, it is difficult to get the device in a quiescent state to perform a hardware state migration. In these cases, the hardware may still write to guest memory even when the VM execution is stopped. But we believe that in most cases, when using passthrough of self-virtualizing devices using unequal device exposure, it is possible to utilize some device specific operations in the VMM to bring a slave device into a quiescent state. In this state, the slave device stops accessing guest memory which ensures that the VMM is able to migrate guest memory pages in a consistent state.

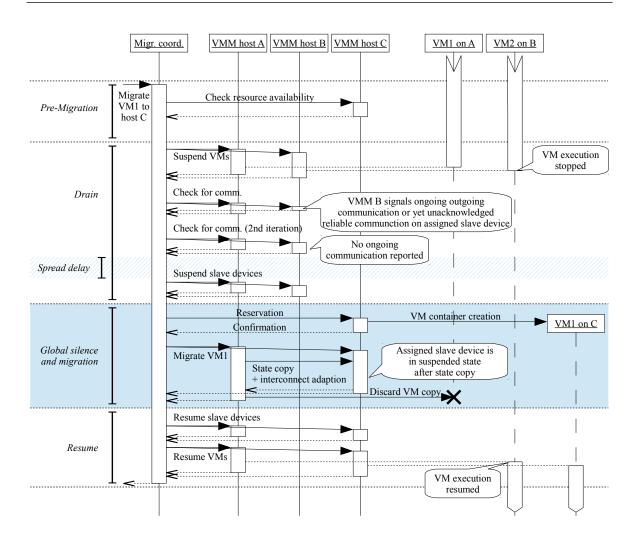

In addition, the presented approaches rely on the assumptions that interactions with the VM are using an interconnect technology that can handle temporary service downtimes and that adapting the environment configuration is transparent to interacting remote parties. The second assumption is not necessarily valid in HPC: For instance, in InfiniBand interconnects, end point node addresses are managed by a dedicated network instance and bound to the physical hardware [25]. As long as such addresses cannot be migrated with the VM in any way, interacting remote parties have to be involved in the reconfiguration process of the interconnect (e.g., by reconnecting to a new end point address). Some alternatives to pure VM-local considerations utilize checkpoint procedures, such as Checkpoint-restart. Checkpoint-restart of a virtual HPC cluster, as proposed by Scarpazza et al. [71], involves suspending the whole cluster and bringing it to a save point before further changes, such as VM migration, are made. On failure, the environment can continue operating from its last checkpoint. The migration itself is performed within a global silence phase where the HPC cluster is completely stopped and all outstanding communication operations are completed (including RDMA operations). This approach eliminates many side effects and reduces the implementation complexity of the migration procedure of a VM. For instance, quiescence of cluster interconnect devices, as we pointed out as requirement for special hardware in Section 2.2.1 on page 15, is achieved automatically. No stopped VM is able to initiate new communication operations (including RDMA). Furthermore, service downtime due to migration plays a minor role, since stopped VMs do not access services (e.g., tasks of HPC workload) of migrated VMs any further. The actual environment adaption can then be performed by all involved VMMs. Scarpazza et al. [71] describe Checkpoint-restart procedures with a three-phase model:

#### Phase 1: Drain

The Drain phase begins with the suspend notification to the virtual cluster and covers the time the cluster needs to reach global silence. It includes successfully suspending all VMs as well as completing outstanding communication.

#### Phase 2: Global Silence

At this phase it is possible to simultaneously migrate multiple VMs to different VMMs and to perform interconnect reconfiguration.

#### Phase 3: Resume

The Resume phase covers the time the cluster needs to go back into normal operation. All VMs are resumed in this phase.

However, this approach does make downtime only invisible to interacting parties when they are all under the control of a coordinating instance. This instance has therefore to be able to suspend each party. Generally, these assumptions apply for HPC IaaS, where each HPC node is virtualized and the according virtual cluster is managed by a data center management instance. Furthermore, compared to traditional cloud jobs, HPC jobs are typically isolated from third party communication and communication is used only within the cluster for synchronization and intermediate stage coordination purposes.

# 2.3 InfiniBand as HPC Interconnect

*InfiniBand* is currently a popular and modern interconnect for HPC which is also reflected by the TOP500 supercomputer list of November 2012 [79]: *InfiniBand* is used in 44.8% of all listed installations and the most used one, even amongst the 15 highest ranged supercomputers. It is mainly designed for building system area networks (SANs). Such a SAN is intended, like shared bus architectures, to connect processors nodes and I/O nodes together [25]. However, *InfiniBand* resolves scalability, expandability, and fault tolerance limitations of bus architectures by utilizing bidirectional point-to-point links through switches and routers [9]. Because *InfiniBand* utilizes massive protocol offloading, zero processor-copy data transfer (also called RDMA), and OS-bypass techniques [25], it provides cutting edge communication performance and low latency that meet the requirements for communicationintensive HPC workloads running on multiple processor nodes [21].

In the following sections we give a brief overview of the *InfiniBand* architecture specification [25] which was published by the *InfiniBand Trade Association* in November 2007. After that we discuss in Section 2.3.5 on page 25 how self-virtualization is implemented on common *InfiniBand* host adapters.

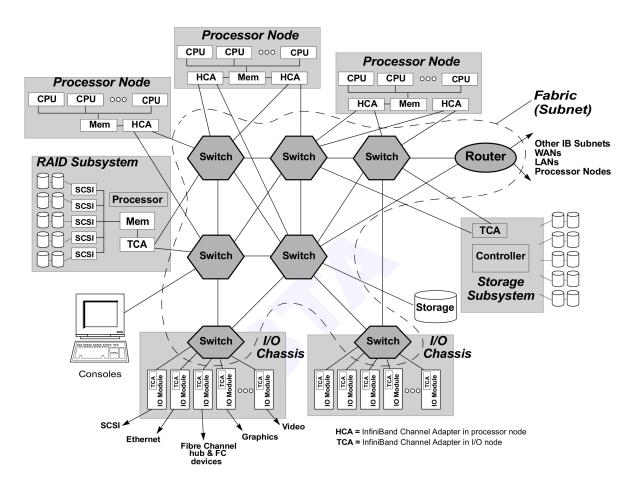

### 2.3.1 Subnets and Network Management

*InfiniBand* networks are organized in subnets, also called fabrics [73]. As represented in Figure 2.7 on the facing page, they consists of multiple *InfiniBand* endnodes that are interconnected with bidirectional point-to-point links through switches or routers or are interconnected directly [16]. Such an endnode is defined as a device, other than a network switch or router, and is connected to the fabric with a channel adapter (CA) [73]. Such a CA may have multiple ports. A CA of a host device is called host channel adapter (HCA) and a CA for an I/O device, like a storage subsystem, is called target channel adapter (TCA). Each CA, and also its ports, is uniquely identifiable with persistent global unique IDs (GUIDs). These GUIDs are assigned by the CA vendor during manufacturing [25]. Switches route traffic within its local subnet and router route traffic between different subnets [73].

For each *InfiniBand* subnet one subnet manager (SM) entity is responsible for configuring and managing switches, routers, and CAs. When multiple SMs are active in a subnet, the SM instances negotiate which of them will operate as master SM [16]. Such a SM is typically implemented within a fabric device, more precisely on a CA or a switch. For instance, *OpenSM* [51] is a popular open source software SM that can be run on a host configured with a HCA. The master SM checks periodically, or on a incoming signaling message (trap), the fabric for changes and assigns each port of every CA connected to the subnet with a local ID (LID) and the subnet prefix. The LID is unique within the subnet and the subnet prefix addresses the according subnet. Further, the master SM performs route calculations and configures the switches of the according fabric [16]. Routers connected to the fabric run

Figure 2.7: Exemplary InfiniBand network overview (source: [25])

a low level functionality which is called subnet manager agent SMA that responses to the commands and queries sent by the master SM [9].

Within a subnet, remote CA ports are addressed with their LID. Outer-subnet addressing, however, works a bit different: Routers are not completely transparent to the endnodes since the source CA needs to specify the LID of the router port in the subnet and also the global ID (GID) of the destination. This GID is assembled with the target port GUID and the assigned subnet prefix.

### 2.3.2 Queue Pairs and Transport Services

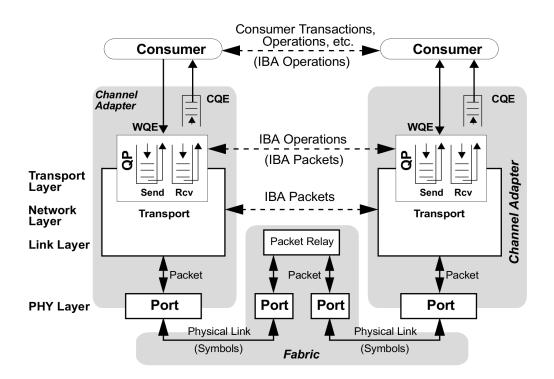

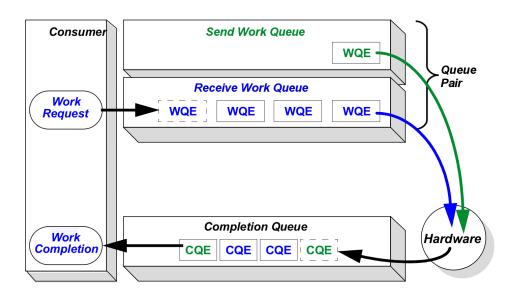

Communication over *InfiniBand* interconnects takes place between two queue pairs (QP). They form a virtual interface of the CA hardware to the consumers (e.g., an application on a processor node). Each QP is isolated and protected from other QPs and can be considered as a private resource assigned to a single consumer. Such a QP consists of two work queues (WQ) where a consumer can post work queue elements (WQEs) on it: (1) a receive WQ

Figure 2.8: Communication stack of InfiniBand (source: [25])

and (2) a send WQ. Such a WQE describes a work request and is picked-up (according to the FIFO principle) for execution by the CA [9]. The request is either a sending operation request on the send WQ (e.g., data send, RDMA access) or a receiving operation request on the receive WQ. However, there is only one receive operation currently available and it is to specify a receive data buffer for data that will be received by a remote consumer executing a send operation. When a CA completes a work request, it places a completion queue element (CQE) on a associated completion queue (CQ) of the QP. This way, the status result of a WQE is reported by the hardware. Such a CQ can be associated to multiple work queues and has to be created by the consumer beforehand. The Figure 2.9 on the next page provides an illustration of this QP interface concept.

Each QP instance is associated with a so called queue pair number (QPN) which uniquely identifies it on a CA. There are only two predefined QPs that exist for each particular port of a CA: QP0 is dedicated for the SMA instance of the CA as well as for a possible SM application instance running on the according node. QP1 is reserved to be used by special management service agents (on further interest, we refer to the *InfiniBand* specification [25]).

Before a consumer can use a QP and start to communicate through the *InfiniBand* fabric, it must first create a QP instance and specify its class of transport service. In connection oriented communication, each QP is bound to exactly one other QP usually on a remote node. Further, a QP rejects every WQE that is not valid for the configured service class.

Like Ethernet, InfiniBand uses packet based data transport on the interconnect but imple-

Figure 2.9: Queue pair (QP) driven work requests (derived from [25])

ments mechanisms for transport services classes within the CA. A consumer can thereby specify between, as shown in Table 2.2 on the following page, five different QP transport services during QP creation:

#### **Reliable connection**

Reliable transfer of data between exactly two connected QP instances in the *InfiniBand* network [9]. They are comparable with TCP connection in the TCP/IP standard [54] which means that they include error recovery, flow control, and reliability due delivery acknowledgement.

#### Unreliable connection

Unreliable transfer of data between exactly two connected QP instances in the *In-finiBand* network. However, messages may be lost or delivered out-of-order or even corrupted.

#### **Reliable datagram**

A QP configured in this mode can just send and receive messages from one or more QPs without establishing a connection beforehand. Delivery of messages is error recovered and acknowledged.

#### Unreliable datagram

A QP configured in this mode can just send and receive messages from one or more QPs without establishing a connection beforehand. Like unreliable connection, a datagram may also be lost or delivered corrupted. This type of transport service is comparable with UDP datagrams in the TCP/IP standard.

#### **Raw datagram**

Raw datagrams are messages that are not interpreted and handled by the CA hardware.

| Service type          | Connection oriented | Acknowledged | Transport  |

|-----------------------|---------------------|--------------|------------|

| Reliable connection   | Yes                 | Yes          | InfiniBand |

| Unreliable connection | Yes                 | No           | InfiniBand |

| Reliable datagram     | No                  | Yes          | InfiniBand |

| Unreliable datagram   | No                  | No           | InfiniBand |

| Raw datagram          | No                  | No           | Raw        |

Table 2.2: Service types of InfiniBand QPs (source: [25])

Raw datagram QPs can be seen as an interface from the *InfiniBand* data link layer that is directly exported to the consumer [9]. The properties of raw datagrams are the same as unreliable datagrams: They can be sent and received from one or more QPs without establishing a connection beforehand. Such a datagram may also be lost or delivered corrupted.

The main purpose of raw datagram QPs are to send and receive messages for a consumer-handled protocol other than *InfiniBand*, for instance, IP or *Ethernet* packets [73]. This way, non-*InfiniBand* packets can be sent through a *InfiniBand* interconnect [73].

### 2.3.3 Remote DMA (RDMA)

*InfiniBand* supports RDMA operations that perform directly a write or read access to memory of a remote endnode. Such a memory access operation is directly executed by the according remote CA without further involvement or notification to the remote consumer. The consumer requesting a RDMA access thereto submits a RDMA WQE on a send WQ of a reliable connection QP or reliable datagram QP. Access permission is coordinated by the remote consumer with a prior setup of host memory regions that shall be accessible via RDMA. These regions are protected with pairs of memory keys, a local key (LKey) and a remote key (RKey), generated by the CA during memory region registration. The LKey is used internally in work requests to describe a memory region to a local QP. The RKey is passed to every consumer allowed to perform RDMA, which then have to supply this key in each RDMA WQE.

### 2.3.4 Fabric Partitioning

*InfiniBand* supports a way of subnet partitioning via partition keys (PKey). They are setup by the SM which assigns corresponding keys to each port of a CA. In the result, QPs, except QP0, QP1, and raw datagram QPs, are required to be configured for the same partition to be able to communicate with each other. PKeys are therefore carried in every packet of the *InfiniBand* transport (see Table 2.2 on the preceding page) and compared with the configured PKey of the receiving entity. Received packets whose comparison failed are rejected.

## 2.3.5 Resource Sharing Logic of Self-Virtualizing HCAs

HCAs that implement self-virtualization using unequal device exposure (as introduced in Section 2.1.3 on page 12) typically assemble this with the (1) virtual switch or (2) shared port model. In the following we discuss these models based on a presentation by Mellanox's architect Liran Liss held on the *OpenFabrics Alliance* workshop in 2010 [39] and published patches by Mellanox [46] to the Linux RDMA development mailing list [38]. These patches add support for *InfiniBand* HCAs that implement self-virtualization with the shared port model.

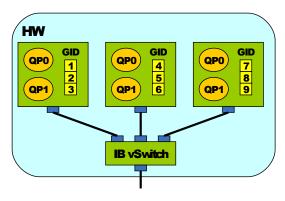

Figure 2.10: Slave HCAs (VFs) behind virtual switch (source: [39])

The *InfiniBand* virtual switch model (see figure 2.10) is comparable with virtual switch implementations of self-virtualizing *Ethernet* adapters. In this model, the *InfiniBand* HCA presents each slave device as a fully stand-alone HCA with own ports and own GUIDs to the interconnect. The ports are connected together on a virtual switch logic implemented in the physical HCA.

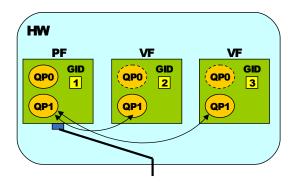

In the shared port model (see figure 2.11), however, the ports of the physical HCA get shared between multiple slave devices. In the point of view of the *InfiniBand* network, there are still only the physical HCA ports seen. Although, each slave HCA and slave port gets its own GUID generated by the master driver and assigned LIDs and subnet prefixes of the master's HCA ports are passed to the depending slaves. Thus, they are shared between master HCA and slave HCAs. Certainly, each virtual port GUID is registered as an alias at the master's physical port. So, each slave still has its own GID. Some other resources, however, are necessarily shared between the master and slave devices. For instance, the QPN space is shared between every HCA instance on a physical HCA and PKey configurations are shared between master HCA when using the same physical port. Since QP0 is coupled with the physical management of the subnet, QP0 is not exposed to slave HCA ports and is totally owned by the master HCA. Slave HCA ports still have a QP0 but no data is

Figure 2.11: Shared port model (source: [39])

coming from and all data that is put into is be dropped. This implies that a SM cannot be run on a slave. All traffic to and from a slave's QP1 is tunneled through the master HCA where it can virtualize or forward certain requests. This way, the master HCA remains full control of *InfiniBand* management and eventually exposes QPs instances to slave devices.

As discussed by Mellanox, the shared port model seems to be more attractive for *Infini-Band* implementation, because it provides higher scalability and lower potential performance degradation compared to the virtual switch model: Since the *InfiniBand* network is unaware of slave HCAs, no additional LIDs are assigned per VM which would unnecessarily bloat the LID space when a huge bunch of VMs configured with slave devices present in a fabric. This way, no routing entries in switches are wasted and potentially associated caching effects in the *InfiniBand* network components that slow down packet forwarding are circumvented.

# 3 Design

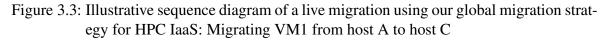

In this chapter, we propose our approach and tool sets to enable guest-transparent live migrating virtual machines (VMs) configured with a directly assigned slave device of a selfvirtualizing hardware. Despite we target our approach for High Performance Computing Infrastructure as a Service (HPC IaaS), we introduce our approach as generic as possible since some of the introduced concepts are also valid in migrating other device states.